### A PIPELINED MULTIPLIER ACCUMULATOR FOCUSING ON PIPELINE ARCHITECTURE

Perpustakaan SKTM

By

## WEK000336

A final year project submitted to the Faculty of Computer Science and Information Technology University of Malaya In fulfillment of the requirements for the degree of Bachelor of Computer Science

Session 2002/2003

#### A PIPELINED MULTIPLIER ACCUMULATOR FOCUSING ON PIPELINE ARCHITECTURE

BY:

LAILI ERNI HITAM

DEPARTMENT OF SYSTEM AND COMPUTER TECHNOLOGY

SESSION 2002/2003

FACULTY OF COMPUTER SCIENCE AND INFORMATION TECHNOLOGY UNIVERSITY OF MALAYA

#### ABSTRACT

The Pipelined Multiplier Accumulator has brought many approaches and changes to the conventional MAC. The Pipelined MAC is believe can speed up the operations of the previous conventional MAC plus it can reduce the time and cost. The effectiveness of pipelining concept in the system's implementation is undeniable as the performance of the system is improved where the multiplication process is pipelined with the addition process. Pipelining reduces cycle time but does not reduce the total time required for multiplication. One way to speed up multiplication is Booth Algorithm, which perform several steps of the multiplication at once. Booth's algorithm takes advantage of the fact that an adder-subtractor is nearly as fast and small as a simple adder. The implementation of Accumulator using Carry Look-ahead Adder (CLA) technique has brought to fast operation achieved in addition process of 8-bit data. The pipeline MAC is designed to increase the speed of MAC operations, decrease the cycle time and to avoid the delay in the conventional MAC.

#### ACKNOWLEDGEMENT

First and foremost 'Alhamdulillah' to Allah, my supervisor Encik Mohd. Yamani Idna Idris for the guidance, advices, tolerant and consideration given in making this project a success. I also would like to thank you my moderator, Encik Zaidi Razak for his comments and evaluation on this project. Not forget my colleagues, Rabiatul Adawiyah Jamil and Norfadilah Khalil for the endurance, tolerant and time spent in making this project. In the way morale support from family deeply appreciated, roommates (for laugh and jokes) and all my friends. In the end, all of this cannot be true if not all the support that I get in making this project success. Last but not least, I want to thank you all members of Faculty of Computer Science and Information Technology for all the information given to complete this course.

i

ii

iii

vi

vii

#### **TABLE OF CONTENTS**

#### Abstract

Acknowledgement

Table of Contents

List of Figures

List of Tables

| 1.0 | Intro | duction                   |   |

|-----|-------|---------------------------|---|

|     | 1.1   | Introduction              | 2 |

|     | 1.2   | Problems Definition       | 4 |

|     | 1.3   | Scope                     | 5 |

| -   | 1.4   | Objective                 | 6 |

|     | 1.5   | Constraints               | 7 |

|     | 1.6   | Works Plan and Scheduling | 8 |

| 2.0 | Liter | ature Review                                             |    |

|-----|-------|----------------------------------------------------------|----|

|     | 2.1   | Introduction                                             | 10 |

|     | 2.2   | Pipeline                                                 | 10 |

|     |       | 2.2.1 Pipeline Overview                                  | 11 |

|     |       | 2.2.2 Operations of Pipeline                             | 11 |

|     |       | 2.2.3 Pipeline Concept in System's Arithmetic Operations | 13 |

|     |       | 2.2.4 Advantages of Pipeline                             | 15 |

|     |       | 2.2.5 Conventional MAC                                   | 17 |

|     |       | 2.2.6 Why Pipelined MAC?                                 | 18 |

|     | 2.3   | Multiplier                                               |    |

|     |       | 2.3.1 Multiplier Overview                                | 19 |

|     |       | 2.3.2 Algorithms in Multiplier Unit                      | 20 |

|     |       | 2.3.3 Booth Algorithm                                    | 21 |

|     | 2.4   | Accumulator                                              |    |

|     |       | 2.4.1 Accumulator Overview                               | 22 |

|     |       | 2.4.2 Approach in Accumulator Unit                       | 22 |

|     |       | 2.4.3 Carry Look-ahead Adder                             | 23 |

|     | 2.5   | Conclusion                                               | 24 |

| 3.0 | Metho | odology                      |    |

|-----|-------|------------------------------|----|

|     | 3.1   | Introduction                 | 27 |

|     | 3.2   | Method of Design             | 27 |

|     | 3.3   | VHDL                         | 29 |

|     |       | 3.3.1 What is VHDL?          | 29 |

|     |       | 3.3.2 The Advantages         | 30 |

|     |       | 3.3.3 New Design Methodology | 32 |

|     |       | 3.3.4 Hardware Abstraction   | 32 |

|     |       | 3.3.5 Basic Concept          | 33 |

|     |       | 3.3.5.1 Timing               |    |

|     |       | 3.3.5.2 Concurrency          |    |

|     |       |                              |    |

|     |       | 3.3.6 VHDL vs. Verilog       | 34 |

|     | 3.4   | ASIC, CPLD and FPGA          | 35 |

|     |       | 3.4.1 ASIC                   | 35 |

|     |       | 3.4.2 CPLD                   | 36 |

|     |       | 3.4.3 FPGA                   | 37 |

|     |       | 3.4.4 CPLD vs. FPGA          |    |

|     | 3.5   | Conclusion                   | 39 |

| 4.0 | Syste | em's Design        |        |

|-----|-------|--------------------|--------|

|     | 4.1   | Introduction       | 41     |

|     | 4.2   | System Overview    | 41     |

|     | 4.3   | Top-Level Design   | <br>43 |

|     | 4.4   | Pipeline in MAC    | 44     |

|     | 4.5   | Multiplier in MAC  | 47     |

|     | 4.6   | Accumulator in MAC | 48     |

|     | 4.7   | Signal Controller  | 49     |

|     | 4.8   | Conclusion         | 50     |

|     |       |                    |        |

|  | 5.1 | 5.1 | Introduction |  |

|--|-----|-----|--------------|--|

|--|-----|-----|--------------|--|

System Implementation

5.0

| 5.2 | PeakF  | PGA Designer Suite FPGA Synthesis Edition | 53 |

|-----|--------|-------------------------------------------|----|

| 5.3 | Pin De | escription                                | 57 |

| 5.4 | System | n Coding                                  | 58 |

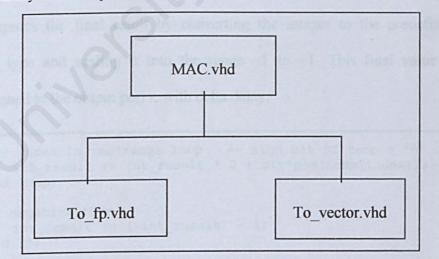

|     | 5.4.1  | The Behavioral Model                      | 59 |

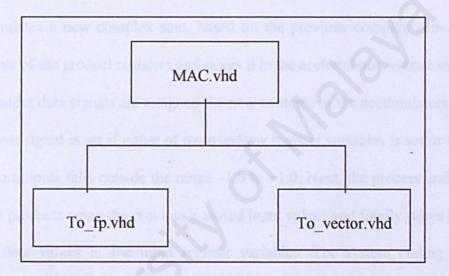

|     |        | 5.4.1.1 To_fpo Module                     | 60 |

|     |        | 5.4.1.2 To_vector Module                  | 61 |

|     |        | 5.4.1.3 MAC Module                        | 62 |

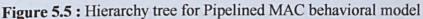

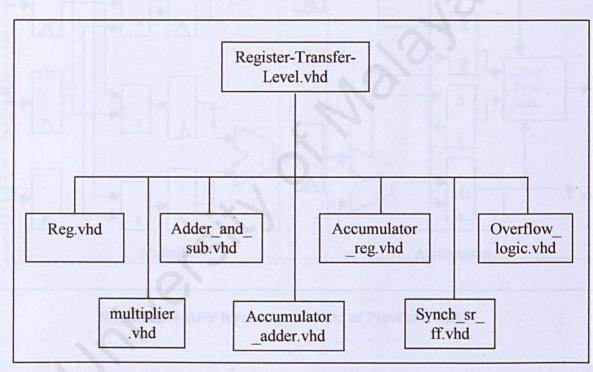

|     | 5.4.2  | The Register-Transfer-Level Model         | 63 |

|     |        | 5.4.2.1 Pipeline register Module          | 64 |

|     |        | 5.4.2.2 Set/Reset Flipflop Module         | 65 |

| 5.5 | Conclu | usion                                     | 65 |

53

#### 6.0 Testing

| 6.1 | Introd | uction                    | 69 |

|-----|--------|---------------------------|----|

| 6.2 | Simul  | ation Using PeakFPGA      | 70 |

|     | 6.2.1  | Compiled Selected         | 71 |

|     | 6.2.2  | Link Selected             | 71 |

|     | 6.2.3  | Load Selected             | 72 |

|     | 6.2.4  | Options                   | 73 |

| 6.3 | Unit T | esting                    | 75 |

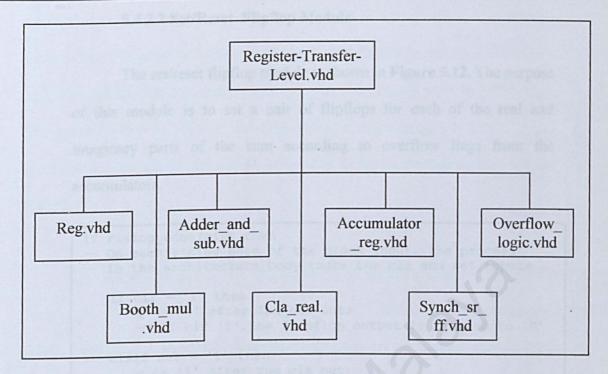

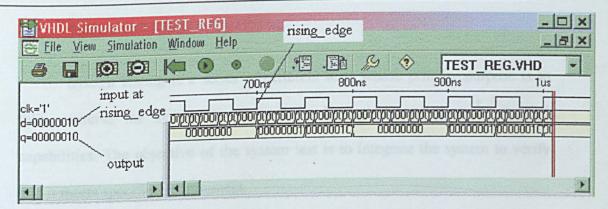

|     | 6.3.1  | Pipeline Register Module  | 75 |

|     | 6.3.2  | Set/Reset Flipflop Module | 76 |

| 6.4 | System | n and Integration Testing | 77 |

| 6.5 | Concl  | usion                     | 78 |

# 7.0System Evaluation7.1Introduction807.2Discussion807.3System Strengths837.4System Constraints85

|      | 7.5   | Future           | Enhancements                                           |     |

|------|-------|------------------|--------------------------------------------------------|-----|

|      |       | 7.5.1            | Module Changing                                        | 86  |

|      |       | 7.5.2            | Implementation of Pipelined MAC                        | 89  |

|      | 7.6   | Know             | ledge And Experience Gained                            | 89  |

|      | 7.7   | Conclu           | usion                                                  | 91  |

| ppen | dix   |                  | cunventoral MAC                                        |     |

|      |       |                  |                                                        |     |

|      | Appen | dix 1: F         | Pipelined Mac Pins Description                         | 94  |

|      | Appen | dix 2 <b>:</b> F | Pipeline                                               | 96  |

|      | Appen | dix 3 <b>:</b> ( | Carry Look-Ahead Adder                                 | 99  |

|      | Appen | dix 4: E         | Booth Algorithm                                        | 101 |

|      | Appen | dix 5: 7         | The Behavioral Model Of The Pipelined Mac              | 102 |

|      | Appen | dix 6: 7         | The Register-Transfer-Level Model Of The Pipelined MAC | 106 |

|      | Appen | dix 7: F         | PeakFPGA Designer Suite FPGA Synthesis Edition         | 110 |

#### References

A

#### LIST OF FIGURES

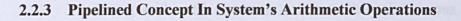

| Figure 2.1 | An arithmetic pipeline with N units                                      | 15 |

|------------|--------------------------------------------------------------------------|----|

| Figure 2.2 | Dataflow diagrams showing order of operations<br>by the conventional MAC | 18 |

| Figure 2.3 | Pipelined concept in system's operation                                  | 19 |

| Figure 3.1 | Top-down design and bottom-up implementation                             | 28 |

|            |                                                                          |    |

| Figure 3.2 | CPLD Architecture                                                        | 36 |

|            |                                                                          |    |

| Figure 4.1 | System's block diagram                                                   | 42 |

|            |                                                                          |    |

| Figure 4.2 | Black box for top-level design                                           | 43 |

| Figure 4.3 | Dataflow diagrams showing order of operations by the pipelined MAC       | 44 |

| Figure 4.4 | Black box for pipelined in MAC                                           | 46 |

| Figure 4.5 | Black box for multiplier in MAC                                          | 47 |

| Figure 4.6 | Black box for multiplier in MAC                                          | 48 |

| Figure 5.1 | Main Application Window for PeakFPGA                                     | 54 |

| Figure 5.2 | Hierarchy Browser Window for PeakFPGA                                    | 54 |

| Figure 5.3 | Transcript Window for PeakFPGA                                           | 55 |

| A Pipelined | Multiplier Accumulator : Pipeline                              | 0  |

|-------------|----------------------------------------------------------------|----|

| Figure 5.4  | Pipelined MAC Top Level Design Symbol                          | 57 |

| Figure 5.5  | Hierarchy tree for Pipelined MAC behavioral model              | 59 |

| Figure 5.6  | Coding to convert input to a bit vector                        | 60 |

| Figure 5.7  | Loop to get the final result                                   | 60 |

| Figure 5.8  | Coding to convert input into the correct range                 | 61 |

| Figure 5.9  | Loop to bet the floating-point result                          | 62 |

| Figure 5.10 | Hierarchy tree for Pipelined MAC Register-Transfer-Level model | 64 |

| Figure 5.11 | Architecture Body for a Pipeline Register Module               | 64 |

| Figure 5.12 | Architecture for Set/Reset Flipflop Module                     | 65 |

| Figure 6.1  | Window show the simulate menu options for PeakFPGA             | 70 |

| Figure 6.2  | Waveform from test bench for pipeline register                 | 76 |

| Figure 6.3  | Waveform from test bench for set/reset flipflop                | 76 |

#### **LIST OF TABLES**

| Table 1.1 | Work plan and scheduling for Pipelined MAC       | 8  |

|-----------|--------------------------------------------------|----|

| Table 2.1 | Comparison between algorithms in multiplier unit | 20 |

| Table 2.2 | Comparison between adders in Accumulator         | 22 |

| Table 3.1 | Comparison between VHDL and Verilog              | 34 |

| Table 3.2 | Comparison between CPLD and FPGA                 | 38 |

| Table 5.1 | Pipelined MAC Pins Description                   | 58 |

**Chapter 1**

## INTRODUCTION

A Pipelined Multiplier Accumulator : Pipeline

#### CHAPTER 1 INTRODUCTION

#### 1.1 Introduction

Multiplier Accumulator also known as MAC is design for a stream of complex numbers. The MAC Unit can be broken up into two distinct units: a data storage path and a data processing path. The data storage path consists of a set of registers that hold data values. The data processing path consists of multiplier unit and adder unit, which perform data multiplication and accumulation sequentially. The control signals provided by the i-unit (instruction unit) designate what process the MAC will perform to get the desired data in one clock cycle.

In the MAC design, both the multiplier and adder are complete custom designs. The multiplier uses the combination of a Booth bit pair encoding algorithm, a sign extension technique, and a carry look-ahead adder with two levels of look-ahead. The Booth encoding algorithm is a technique that will reduce the number of partial products generated. Using the booth-encoding algorithm, fewer partial products will have to be added and therefore the overall speed of the multiplication will be faster.

A complex MAC operates on two sequences of complex numbers,  $\{x_i\}$ and  $\{y_i\}$ . The MAC multiples corresponding elements of the sequences and accumulates the sum of the products. The result is

$$\sum_{i=1}^{N} x_i y_i$$

Where N is the length of the sequences. Each complex number is represented in Cartesian form, consisting of a real and an imaginary part. If we are given two complex numbers x and y, their product is a complex number p, calculated as follows :

$$p_{real} = x_{real} \times y_{real} - x_{imag} \times y_{imag}$$

$p_{imag} = x_{real} \times y_{imag} + x_{imag} \times y_{imag}$

The sum of x and y is a complex number s calculated as follows :

s real = x real + y real

$s_{imag} = x_{imag} + y_{imag}$

MAC calculates its results by taking successive pairs of complex numbers, one each from the two input sequences, forming their complex product and adding it to an accumulator register. The accumulator is initially cleared to zero and is reset after each pair of sequences has been processed.

If we count the operations required for each pair of input numbers, the MAC must perform four multiplications to form partial products, then a subtraction and an addition to form the full product and finally two additions to accumulate the result. Since the operations must be performed in this order, the time taken to complete processing one pair of inputs is the sums of the delays for the three steps.

In a high-performance digital signal processing application, this delay may cause the bandwidth of the system to be reduced below a required minimum. Because of that, the Pipelined Multiplier Accumulator is design by pipelining the MAC to avoid the delay at non-pipelined MAC. The pipelining allows the overlapped of the task in multiplier operations.

#### **1.2 Problems Definition**

The problem that occurs in this project is time delay. Before pipeline is used, to finish a complete instruction in MAC takes 3 clock cycles. Therefore, CPU must wait for 3 clock cycles to run the complete instruction before it will be used in additions operation in accumulator. The delay can be avoided by pipelining the MAC.

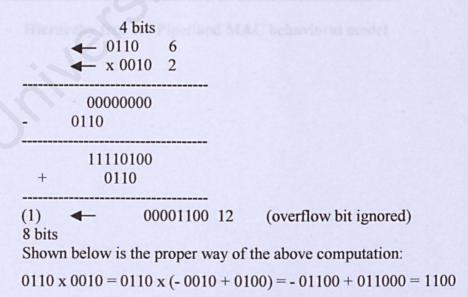

The other problem is in the multiplier part, pipelining reduces cycle time but does not reduce the time required for multiplication. The design of multiplier is important since it determines the overall performance (in term of speed) of the whole system. In adder part, the problem is overflow case. It occurs when the sum of the product is out of the range. Possibility of overflow is high and the system does not work correctly when it happen.

#### 1.3 Scope

The researches will mainly concentrate on the problem that occurs in pipelined part besides the problem in multiplier part and accumulator part. In case to avoid delay, the pipeline method is used in the multiplier accumulator. But, pipelining only reduces cycle time but does not reduce the total time required for multiplication. So, another method is needed as a solution for this problem. For overflow condition, instead of the possibility of overflow is low, one solution is needed to make sure the overflow cannot affects the system. This project will be finished by the simulation part only because there is no implementation part. The topics that covered for every chapter is describe below:

**Chapter 1** of Pipelined Multiplier Accumulator project is about the introduction of this project. This chapter will be discussing about problems definition in this project, objective of the Pipelined Multiplier Accumulator, scope of project and works plan and scheduling.

**Chapter 2** is about the literatures review. This chapter will de discussing about problem researches that has been occurred before this project will be implement. The discussion will include the researches and analysis for the methods and technique that will be used in this project. There is a comparison between some methods. The most important thing in pipeline MAC is pipeline method.

Chapter 3 will be discussing about the methodology that will be used in this project. Some of the method that will be discuss in this chapter is VHDL, FPGA, CPLD and ASIC. All the method will be discuss but only the best method will be used for this project.

Chapter 4 will be discussing about system analysis and design. The functional, hardware and software requirement will also be discussed in this chapter. Besides that, in this chapter, combinational of the Pipelined Multiplier Accumulator will also be represented.

#### 1.4 Objective

The main goal of this project is to reduce time delays in MAC. In a highperformance digital signal processing application, this delay may cause the bandwidth of the system to be reduced below a required minimum. Because of that, the Pipelined Multiplier Accumulator is design by pipelining the MAC to avoid the delay at non-pipelined MAC.

In order to operate the system under a fast, continuous stream of data, the concept of pipelining these multiplication and addition process is implemented in the design of the system units. Pipelining reduces cycle time but doesn't reduce the total time required for multiplication. One way to speed up multiplication is **Booth Algorithm**, which performs several steps of the multiplication at once. [Wayne, 98] Booth Algorithm will be discussed later in next chapter (Chapter 3: Literature Reviews).

As a conclusion, the goals of Pipeline Multiplier Accumulator design is:

- Avoid the delay

- Speed up multiplication

- Easy for stream of complex numbers

#### 1.5 Constraints

Some limitation can be expected in designing this pipelined multiplier accumulator, because some standard need to be familiarize so it can be implemented. Pipeline in MAC only reduces the cycle time but do not reduce the total time required for multiplication. It means, besides pipelining the MAC another algorithm is needed to speed up the multiplication. Beside that, the needs for development tools are limited. Tools such as VHDL simulator and test or demo board to download the design are hard to obtain. Hence, due to these limitations the some of the feature maybe can't be implemented fully.

#### 1.6 Works Plan and Scheduling

The works will be based on the planning and timetable that has been created earlier. This important because each work must be done in time and careful planning will make it possible.

| TOPIC      | JUNE | JULY | AUGUST | SEPTEMBER | OCTOBER | NOVEMBER | DECEMBER | JANUARY |

|------------|------|------|--------|-----------|---------|----------|----------|---------|

| Research   |      |      |        |           |         |          |          |         |

| Analysis   |      |      |        |           |         |          |          |         |

| Design     |      |      |        |           | 1       |          |          |         |

| Simulation |      |      |        |           |         |          |          |         |

| Report     |      |      |        |           |         |          |          |         |

Table 1.1 Work plan and scheduling for Pipelined MAC

**Chapter 2**

## LITERATURE REVIEW

#### CHAPTER 2 LITERATURE REVIEW

#### 2.1 Introduction

This chapter will be discussing about the technique and algorithm that used in this project and why it is chosen. There are three parts, which is literature review in pipeline, multiplier and accumulator. In pipeline, it will discuss about the basic concept of pipeline, why pipelining is needed in multiplier accumulator, pipeline operation and pipeline concept in system's arithmetic operations. In multiplier, there will be a comparison between some of the method. But Booth Algorithm will be used with the purpose to speed up multiplication rather than other method. Besides that, in adder part, a few method of adder will also be discussed. But the best adder will be used in this project is Carry Look-Ahead Adder (CLA).

#### 2.2 Pipeline

Pipelined Multiplier Accumulator will be designed to avoid the delay in conventional MAC. This method is based on the concept of the pipelining, which is can make the cycle time become faster. Discussion below will be discussed about the concept of pipelining and how it will reduces the cycle time.

Pipeline is an implementation technique in which multiple instructions are overlapped in execution. Today, pipelining is the key to make fast processors. The pipeline approach will take much less time. Pipelining is a logic design technique that adds ranks of memory elements to reduce clock cycle time at the cost of added latency. Pipelining is organizational approach is quite common used to reduces cycle time but doesn't reduce the total time required for multiplication. That's why pipeline is suitable to use in Multiplier Accumulator (MAC).

#### 2.2.2 Operations of Pipeline

Most of the complex arithmetic functions encountered in computation can, in principle, be implemented by pipelining. Basic operation on fixed point and floating point numbers can be efficiently partitioned into sub-operations suitable for pipelining.

Pipelining is a method, which can be used to increase the speed of operation of the control processor on arithmetic function operations circuitry. They are often applied to the internal design of high speed computers, including advanced microprocessors as a type of multiprocessing. Pipelining is a technique in which a task or operation is divided into a number of subtasks that are perform in sequence. Its own logic unit performs each subtask, rather than by a single unit, which performs subtasks. The units are connected together in a serial fashion with the output of the connecting to the input of the next and all the units operate simultaneously. While one unit is performing a subtask of the *i*th task, the proceeding unit in the chain is performing a different subtask on the (i+1)th task. [Barry, 91]

In pipelining, a task is presented to the first unit. Once the first subtask of this task is completed, the results are presented to the second unit and another task can be presented to the first unit. Results from one subtask are passed to the next unit as required and a task is completed when all the units have processed the subtasks.

Suppose each unit in the pipeline has the same operating time to complete a subtask and that the first task is completed and a series of task is presented. The time to perform one complete task is same as the time for one unit to perform one subtask of the task, rather than summation of all the unit times. Ideally, each subtask should take the same time, but if this is not the case, the overall processing time will be that of the slowest unit with the faster units being delayed. It may be advantages to equalize stage-operating times with the insertion of extra delays.

During the design of the arithmetic circuitry, speed improvement is considered, as a continuous data stream is processed. The technique of pipeline process is recommended due to the increase speed achieved, compared with other conventional methods.

In conventional arithmetic design, most increase in the number of tasks that could be executed in a unit time interval by arithmetic processor have been achieved by reducing the length of time required to perform a single task, using faster logic circuitry. For instance, faster adders are designed to allow simultaneous addition of many numbers.

However, the circuit technology has almost reached its ultimate limit of light speed. Furthermore, when dueling with large processing works, it could not provide significant increases in computing speed. This problem of speed improvement could be solved through allowing simultaneous execution of many tasks by multiple arithmetic units, which is referred as pipelining operation.

Pipelined approach is a type of architectural design, which significantly increases the number of task that can be executed in a unit time interval, with only a moderate increase in hard ware investment compared with conventional design.

Pipelining arithmetic operation refers to the subdivisions of the total computation workload into individual tasks, so that they can be executed in an overlapped fashion by each own logical unit or segment rather than by a single unit, which performs the whole workload. This overlapped executions are often used in central processor design, in which the fetch, decode, effective address calculation and operand fetch of the next instruction can be overlapped with execution of the current instruction. In this case, when the instruction overhead and the execution times are nearly equal, the overlapped processor will be twice as fast as the conventional design.

A pipelined arithmetic operating unit is defined as a collection of series of hardware resources (units of task), which are arranged as a pipeline with synchronized timing control (for synchronous pipeline data transfer), such that a flow of subdivided tasks can be simultaneously executed by the successive units of the pipeline, as illustrated in Figure 2.1.

In this pipelined arithmetic operation, each operational unit is a special purpose combinational arithmetic logic circuitry with delay T, such as an adder, a multiplier etc. data latches are used as synchronized registers, in order to hold the input and output data of successive units. Each of these latches will latch its data to the next unit when triggered by its external clock signal. In the normal cases, two additional latches are

added to the two end units, which handle the inputs and outputs of the

entire pipelined system.

Figure 2.1 An arithmetic pipeline with N units

#### 2.2.4 Advantages of Pipelined

There are many advantages of pipeline that make it suitable to use in MAC to reduces the latency and time delays problem. The most important advantage of pipeline is it increasing the speed of the system. It makes time to finished the clock cycle become more faster than not the time to finished without it. The cycle time T of an instruction pipeline is

the time needed to advance a set of instruction one stage through the pipeline. The cycle time can be determined as

$$t = \max[t_i] + d = t_m + d$$

$i, 1 \le I \le k$

where

$t_m$  = maximum stage delay (delay through stage which experiences the largest delay)

k = number of stages in the instruction pipeline

d = time delay of a latch, needed to advance signals and data from one stage to the next.

In general, the time delay d is equivalent to a clock pulse and  $t_m >> d$ . Now suppose that n instructions are processed, with no branches. The total time required  $T_k$  to execute all n instruction is

$$T_k = [k + (n-1)]_t$$

A total of k cycles are required to complete the execution of the first instruction and the remaining n-1 cycles.

The speedup factor for the instruction pipeline compared to execution without pipeline is defined as

$$S_k = T_l/T_k = nkt / [k + (n-1)]t = nk / k + (n-1)$$

Besides increasing the speed of system, in some cases, the pipelining technique has the advantage of requiring less logic than a non-pipelined system. Obviously, it could be seen that, the rate of the pipelined system depends on the unit with maximum delay time. [William, 96]

In conventional MAC, a complex MAC operates on two sequences of complex numbers,  $\{x_i\}$  and  $\{y_i\}$ . The MAC multiples corresponding elements of the sequences and accumulates the sum of the products. The result is

$$\sum_{i=1}^{N} x_i y_i$$

N

where N is the length of the sequences. Each complex number is represented in Cartesian form, consisting of a real and an imaginary part. If we are given two complex numbers x and y, their product is a complex number p, calculated as follows :

$p_real = x_real \ge y_real - x_imag \ge y_imag$  $p_imag = x_real \ge y_imag + x_imag \ge y_imag$

The sum of x and y is a complex number s calculated as follows :

s\_real = x\_real + y\_real s\_imag = x\_imag + y\_imag

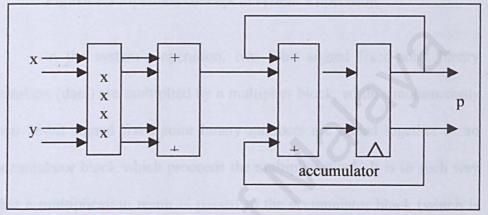

MAC calculates its results by taking successive pairs of complex numbers, one each from the two input sequences, forming their complex product and adding it to an accumulator register. The accumulator is initially cleared to zero and is reset after each pair of sequences has been processed. To count the operations required for each pair of input numbers, the MAC must perform four multiplications to form partial products, then a subtraction and an addition to form the full product and finally two additions to accumulate the result, this is shown in Figure 2.2. Since the operations must be performed in this order, the time taken to complete processing one pair of inputs is the sums of the delays for the three steps.

Figure 2.2 Dataflow diagrams showing order of operations by the conventional MAC

#### 2.2.6 Why Pipelined MAC?

The previous research done by many researches have pointed out the issue to create a MAC with higher execution speed and decrease cycle time. Therefore, the best solution is used pipeline technique in multiplication unit. MAC is pipelining to avoid the delay in the process. This design of pipelined multiplier accumulator (MAC) is for a stream of complex number.

In order to operate the system under a fast, continuous stream of data, the concept pipelining these multiplication and addition process is

implemented in the design of the system units, as shown in a block

diagram below in Figure 2.3.

Figure 2.3 Pipelined concept in system's operation

In the system's operation, two 8-bit signed fixed-point binary numbers (data) are multiplied by a multiplier block, while simultaneously two 16-bit signed fixed-point binary numbers are added together in an accumulator block which proceeds the multiplier block. It is in such way that a multiplication result is passed to the accumulator block (which is feedback to the block for next additional operation); in order to obtain the next output result.

#### 2.3 Multiplier

#### 2.3.1 Multiplier Overview

Multiplier is one part of Pipelined Multiplier Accumulator. Multiplier design starts with the elementary school algorithm for multiplication. The computation of partial products and their accumulation into the complete product can be optimized in many ways, but an understanding of the basic steps in multiplication is important to a full appreciation of those improvement. One approach to speed up the

operation of speed up multiplication is Booth Algorithm [Boo, 51], which

performs several steps of the multiplication at once.

#### 2.3.2 Algorithms in Multiplier Unit

| Approach                                                        | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit-Pair Recording                                              | <ul> <li>-Multiplication speed up technique that guarantees that<br/>an n-bit multiplier will generate at most n/2 summands<br/>and will uniformly handle the signed- operand case<br/>(Cavanagh, 84).</li> <li>-The total number of clock pulses needed is small.</li> <li>-This technique can multiply the products two times<br/>than the Booth Algorithm.</li> <li>-In this technique, three data bits are checked in each<br/>time.</li> </ul> |

| Add-Shift Sequential<br>Multiplication                          | -Only required positive multiplier. If negative<br>multiplier is used, both multiplicands had to be in 2's<br>complement before the multiplication is performed.<br>-Method becomes complex when perform negative<br>multiplier because it need to change the binary<br>representation to 2's complement.<br>-Inflexible due to the need to exchange the circuit to<br>execute certain task.                                                        |

| 2's Complement<br>Modular Arrays<br>Multiplication<br>Technique | <ul> <li>-Using general multiply algorithm with special feature where the whole operation is modularized into section.</li> <li>-Used Carry-Save and Carry Look-Ahead adders approach to sum up these module outputs to get the final product.</li> <li>This technique leads to delay where it need more time to perform the local multiplication; speed of overall operation is increased.</li> </ul>                                              |

| Booth Algorithm                                                 | -Generates 2n-bit product with n-bit input.<br>-Direct algorithm. Treats positive and negative<br>numbers equally (in the same manner).                                                                                                                                                                                                                                                                                                             |

Table 2.1 Comparison between algorithms in multiplier unit

In Pipelined MAC, the speed of multiplier in performing its task is essentially important. Therefore, a fast multiplication technique is needed. In multiplication, four algorithms have been considered to implement in the design. Each of every algorithm has own characteristic as shown in Table 2.1.

#### 2.3.3 Booth Algorithm

The Booth Algorithm is chosen for its speed up operations and simplicity. This algorithm is believed can achieve certain goals that have been highlighted earlier. Booth's algorithm takes advantage of the fact that an adder-subtractor is nearly as fast and small as a simple adder. It treats the negative and positive number uniformly. With this technique, system can multiply operand to get the partial products more quickly with the decoding method. With streams of bit 0's instead of the alternate streams of 0's and 1's, doing multiplication is not a nightmare anymore.

The implementation of this approach in hardware is the most consideration for choosing this method. The simplicity and ease understanding the hardware suits the design purposes. The components can be used more than once and this approach can save the cost in developing the system.

#### 2.4 Accumulator

#### 2.4.1 Accumulator Overview

As for the design requirement where synchronous type of pipeline data transfer is used, only synchronous adders are considered in the construction of the Accumulator unit. In order to select the most suitable adders which meet the requirements, a good understanding of the carry speed-up techniques used in these adders is essential. Therefore, a thorough study on these adders's hardware organization is needed.

#### 2.4.2 Approach in Accumulator Unit

| Approach           | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ripple-Carry Adder | <ul> <li>Get the name due to the result of an addition of two bits depends on the carry generated by the addition of the previous two bits.</li> <li>Has considerably low speed due to large propagation delay in its operation.</li> <li>It limits the frequency rate of data stream to be processed, although its implementation is rather simpler than other type of adders being discussed later.</li> </ul> |

| Carry-Select Adder | <ul> <li>Using the carry in assumption technique which can increase<br/>the speed of operation.</li> <li>This technique is implemented for each of partition of four<br/>bit groups or section adders which consist of the same<br/>design.</li> </ul>                                                                                                                                                           |

| Conditional Sum    | - Using the carry in assumption technique but for individual                                                                                                                                                                                                                                                                                                                                                     |

| Adder              | bit.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Carry Look-Ahead   | - Solves the slow speed problem by calculating the carry                                                                                                                                                                                                                                                                                                                                                         |

| Adder              | signals in advance, based on the input signals.                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 2.2 Comparison between adders in Accumulator

#### 2.4.3 Carry Look-ahead Adder

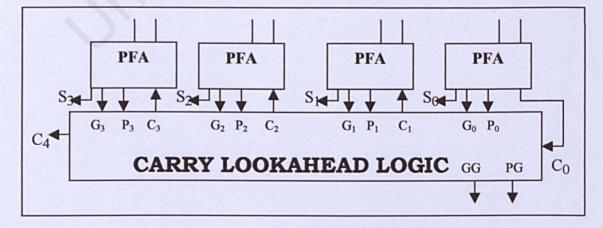

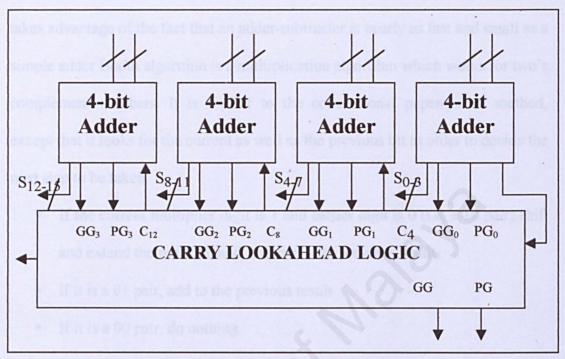

Based on the comparison above, Carry Look-ahead Adder is the best choice to use in Accumulator unit. Using Carry Look-ahead Adder will solve the slow speed problem that occurs when many bits need to add. Carry Look Ahead solves this problem by calculating the carry signals in advance, based on the input signals. It is based on the fact that a carry signal will be generated in two cases:

- 1. when both bits A<sub>i</sub> and B<sub>i</sub> are 1, or

- 2. when one of two bits is 1 and the carry-in (carry of the previous stage) is 1.

The Carry Look-ahead Adder can be broken up in two modules:

1. the Partial Full Adder, PFA, which generates S<sub>i</sub>, P<sub>i</sub> and G<sub>i</sub> as defined by equations below:

$$\begin{array}{l} G_{i} = A_{i.} B_{i} \\ P_{i} = (A_{i} \$ B_{i}) \\ S_{i} = A_{i} \$ B_{i} \$ C_{i} = P_{i} \$ C_{i} \end{array}$$

the Carry Look ahead Logic, which generates the carry-out bits according to equations below:

$$\begin{split} C_1 &= G_0 + P_0 \ C_0 \\ C_4 &= G_3 + P_3 \ G_2 + P_3.P_2.G_1 + P_3.P_2.P_1.G_0 + P_3.P_2.P_1.P_0.G_0 \end{split}$$

The 4-bit adder can then be built by using 4 PFAs and the Carry Look-ahead Logic.

### 2.5 Conclusion

From all the topics that discuss above, that's why pipelined multiplier accumulator (MAC) is designed. It supposes to make the operation in the multiplier accumulator (MAC) faster and avoid the delay and latency in that operation. Pipelining will increase the system speed up by allow the overlapped of the tasks. Pipelined MAC makes the operation of conventional MAC become more faster. This is because the pipelined MAC has pipeline register that will store the input temporarily before it is used in summation, while the system will fetch the next input. As mentioned earlier, with pipeline, three steps delay have been reduced. This will make the process more faster because the system didn't need to wait for the first input to finished it summation before the second input will entered.

The another approach to boost or speed up the operation of Pipelined MAC is Booth Algorithm and Carry Look-Ahead Adder make the operation of Pipeline MAC become more faster than the conventional one. Besides that, the pipelined MAC also has the overflow status signal to control or reduce any possibilities of the overflow to happen in summation.

The Multiplier unit mainly determines the overall performance of the system. The multiplier design is much emphasized in order to select a suitable method for its construction. Although Bit-Pair Recoding is faster than Booth Algorithm technique, the complexity of its design is very much higher than the ladder. With large data processing, the overall operation's performance of Booth

As a conclusion, the effectiveness of pipelining concept in the system's implementation is undeniable as the performance of the system is improved where the multiplication process is pipelined with the addition process. The pipelined MAC has been increased the conventional execution's speed and decrease the cycle time but doesn't reduce the total time required for multiplication.

The next chapter will cover about the methodology that will be used in designing a Pipelined multiplier Accumulator. In the chapter, methods of design that will be used in this project will be discussed. Hardware description language (VHDL) that will be used in simulation and testing will also be discussed later, in chapter 3. Furthermore, the chapter also will be discuss about ASIC and programmable devices, which is CPLD and FPGA and the comparison between these two devices will also be presented.

**Chapter 3**

## METHODOLOGY

### **3.1 INTRODUCTION**

This chapter will be discussing about the methodology that will be used in designing a Pipelined Multiplier Accumulator. There are two methods of design used in this project, which are top-down design and bottom-up design. Hardware description language (VHDL) that will be used in simulation and testing will also be discussed in this chapter. Besides that, this chapter also will discuss about ASIC and programmable devices, which is CPLD and FPGA and the comparison between these two devices will also be presented.

### 3.2 Method of Design

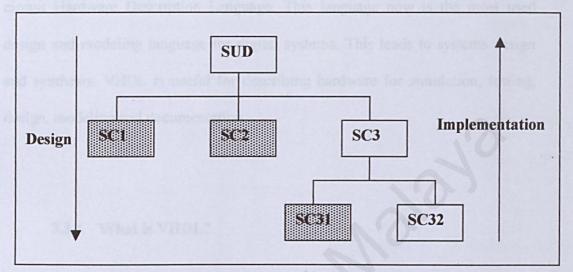

There are two design method will be used in this project, top-down design and bottom-up design. Top-down design technique is recursively partitions a system into its sub-component until all sub-components become manageable design parts. Design became manageable when the component is available as part of the library. It can be implemented by modifying an already available part. Mapping to hardware depends on target the technology, available libraries and tools. Generally, a system can be further partitioned into its simpler components. Figure 3.1 shows the implementation of top-down design and bottom-up design.

SUD – system under design SSC – system sub-component Shaded areas designate sub-component with hardware implementation

Figure 3.1 Top-down design and bottom-up implementation

### 3.3 VHDL

In this project, all the design will be using a hardware description language or better known as VHDL. VHDL stand for Very High-speed integrated circuit Hardware Description Language. This language now is the most used design and modeling language for digital systems. This leads to systems design and synthesis. VHDL is useful for describing hardware for simulation, testing, design, modeling and documentation.

### 3.3.1 What is VHDL?

VHDL it is language that can be used for modeling a digital system at many level of abstraction, from algorithm level to the gate level. The complexity could vary from simple gate to a complete digital electronic system, or anything in between. VHDL always regarded as integrated amalgamation of some language, which is:

- Sequential language

- Concurrent language

- Net-list language

- Time specification

- Waveform generation language

The language has feature or constructs that enables users to express the concurrent or sequential behavior of a digital system as an interconnection of components. By using this constructs, test waveforms can be generated. In the end, the constructs can provide a comprehensive description of system in a single model.

### 3.3.2 The Advantages

The advantages that VHDL offers are :

- Portability

- Because of the code used can be simulated and used in many design tools and in different stages, it reduces dependency for the set of tools whose limited in capability. The VHDL standard also transform design data much easier than a design database of a proprietary design tool.

- Modeling capability

- It is developed to model all level of designs, from electronic boxes to transistors. It can accommodate behavioral constructs and mathematical routines that describe complex models. It allows use of multiple architectures and associates with the same design during various stages of the design process.

### Reusability

- Design can be describes, verified and modified for future use. This eliminates reading and marking changes to schematic pages that are time consuming beside subject to error.

- Documentation

- VHDL is a description language, which allows documentation to be located in single place by embedding it in the code. The combining of comments and the code actually dictates what the design should do reduces the ambiguity between specification and implementation.

- New design methodology

- Using VHDL and synthesis creates a new methodology that increases the design productivity, shortens the design cycle and lower costs.

- Technology and foundry independence

- The functionality and behavior of the design can be described with VHDL and verified, making it foundry and technology independent. This frees the designer to proceed without having to wait for the foundry and technology to be selected.

### 3.3.3 New Design Methodology

The introduction of VHDL and synthesis enables the design community to explore a new design methodology. With the traditional approach, starts with schematics drawing and then performs functional and timing simulation based on the same schematics. If occur errors it back to update the schematics again. After the layout, function and back-annotated timing are verified again with the same schematics. With VHDL, the design is functionally describe.

### 3.3.4 Hardware Abstraction

VHDL is used to describe a model for a digital hardware device, which specifies the external view of the device and one or more internal views. The internal view specifies the functionality or structure, while the external view specifies the interface of the device through which it communicates with the other model in its environment.

The device-to-device model mapping is strictly one-to-many. For example, a device modeled at high level of abstraction may not have been used in the description. Also, the data transfer at the interface may be treated in terms of integer values, instead of logical values. In VHDL, each device model is treated as a distinct representation of a unique device, called an *entity* in this text.

### 3.3.5 Basic Concept

Since VHDL is a hardware description language, it has features, which are conceptually different than other languages. These represents special characteristic of hardware components and carries. These are:

### Timing

Timing is associated with the values that are assigned to the hardware carriers. Signal represent real wires, where the delays of the transfer through wire are concern, thus assignment to signal in VHDL, involve timing.

### Concurrency

The terms refer to the simultaneous operation of various components. The VHDL has constructs that allow a virtually concurrent environment to be created. These constructs satisfy concurrency required for the description of the hardware. Through the use of concurrent constructs, timing of the interconnecting signals and order of the simulation construct or components, a VHDL simulator makes us think that the execution is being done concurrently.

## -0)

### 3.3.6 VHDL vs. Verilog

The table below is shown about the comparison between VHDL

### and Verilog.

|                | VHDL                                  | Verilog                                |  |  |  |  |

|----------------|---------------------------------------|----------------------------------------|--|--|--|--|

| Data Types     | A multitude of language or user       | Very simple, easy to use and very      |  |  |  |  |

| time of a      | defined data types can be used.       | much geared towards modeling           |  |  |  |  |

| devices a      | The Complex Programmable Lord         | hardware structure as opposed to       |  |  |  |  |

|                |                                       | abstract hardware modeling             |  |  |  |  |

| Design         | Procedures and functions may be       | There is no concept of packages.       |  |  |  |  |

| reusability    | placed in a package so that they are  | Functions and procedures used          |  |  |  |  |

| but here with  | avail able to any design-unit that    | within a model must be defined in      |  |  |  |  |

|                | wishes to use them.                   | the module.                            |  |  |  |  |

| Managing large | Configuration, generate, generic and  | There are no statements that help      |  |  |  |  |

| designs        | package statements all help manage    | manage large designs.                  |  |  |  |  |

| 3.4            | large design structures.              |                                        |  |  |  |  |

| Procedures and | Allows concurrent procedure calls     | Does not allow concurrent task calls.  |  |  |  |  |

| tasks          | The Application Section Internet      | ed Circuit (ASIC) verdor bas           |  |  |  |  |

| Libraries      | A library is a store for compiled     | There is no concept of a library. This |  |  |  |  |

|                | entities, architectures, packages and | is due to it's origins as an           |  |  |  |  |

|                | configurations. Useful for managing   | interpretive language                  |  |  |  |  |

|                | multiple design projects.             | ne musks and oursulactores the         |  |  |  |  |

Table 3.1 Comparison between VHDL and Verilog

From all the advantages and specification of VHDL that discuss above, VHDL is choosing to be used in this project. From the comparison above, it shows that VHDL is better than Verilog to use in this project.

### 3.4 ASIC, CPLD and FPGA

Application Specific Integrated Circuit, or ASIC, is a chip that can be designed by an engineer with no particular knowledge of semiconductor physics or semiconductor processes. Ideally, the hardware designer wanted something that gave the flexibility and complexity of and ASIC but with the shorter turn-around time of a programmable device. The solution came in the form of two new devices - the Complex Programmable Logic Device (CPLD) and Field Programmable Gate Array (FPGA). CPLD are as fast as Programmable Array Logic (PAL) but more complex. FPGA approach the complexity of Gate Arrays but are still programmable.

### 3.4.1 ASIC

The Application Specific Integrated Circuit (ASIC) vendor has created a library of cells and functions that the designer can use without needing to know precisely how these functions are implemented in silicon. The vendor then lays out the chip, creates the masks and manufactures the Asics.

The gate array is an ASIC with a particular architecture that consists of rows and columns of regular transistor structures. Each basic cells or gate consists of the same small number of transistors, which are not connected. In fact, none of the transistors on the gate array are initially

-0)

connected at all. The reason for this is that the connection is determined completely by the design that will implement.

### 3.4.2 CPLD

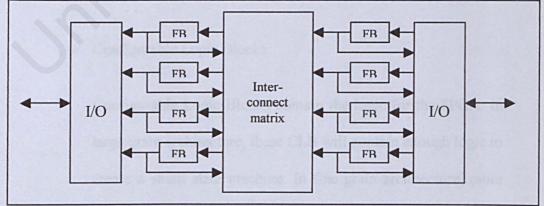

Complex Programmable Logic Device (CPLD) is exactly what they claim to be. Essentially CPLD are designed to appear just like a large number of Pals in a single chip, connected to each other through a cross point switch. The CPLD use the same development tools and programmers and based on the same technologies but they can handle much more complex logic and more of it.

### 3.4.2.1 CPLD Architecture

The diagram in Figure 3.1 shows the internal architecture of a typical CPLD. While each manufacturer has a different variation, in general they are similar in that they consists of function blocks, input/output block and an interconnect matrix.

Figure 3.2 CPLD Architecture

Faculty of Computer Science & Information Technology Session 2002/2003

### 3.4.3 FPGA

Field Programmable Gate Array (FPGA) are called this because rather than having a structure similar to a PAL or other programmable device, they are structured very much like a gate array ASIC. This makes FPGA very nice for use in prototyping ASIC or in places where and ASIC will eventually used. For example, an FPGA maybe used in designs that need to get to market quickly regardless of the cost. Later an ASIC can be used in place of the FPGA when the production volume increases, in order to reduce cost.

### **3.4.3.1 FPGA Architectures**

Each FPGA vendor has its own FPGA architecture, but in general terms they are all a variation. The architecture consists of configurable logic blocks, configurable I/O blocks and programmable interconnect. Also, there will be clock circuitry for driving the clock signals to each logic block and additional logic resources such as ALU, memory and decoders may be available.

Configurable Logic Blocks

Configurable Logic Blocks contain the logic for the FPGA. In large grain architecture, these CLB will contain enough logic to create a small state machine. In fine grain architecture, more

like a true gate array ASIC, the CLB will contain only very basic logic.

Configurable I/O Blocks

A Configurable I/O Block is used to bring signals onto the chip and send them back off again. It consists of an input buffer and output buffer with three state and open collector output controls.

### 3.4.4 CPLD vs. FPGA

The table below is shown the comparison between FPGA and CPLD.

| CPLD                              | FPGA                               |  |  |  |

|-----------------------------------|------------------------------------|--|--|--|

| Complex Programmable Logic Device | Field Programmable Gate Array      |  |  |  |

| PALs                              | Gate Arrays                        |  |  |  |

| Short lead rime                   | High density                       |  |  |  |

| Programmable                      | Can implement many logic functions |  |  |  |

| No NRE charges                    | Relatively fast                    |  |  |  |

Table 3.2 Comparison between CPLD and FPGA

From all the specification of ASIC, CPLD and FPGA that discuss

above, it shows that there are many advantages of FPGA compared to the

others. That is why the FPGA is choosing for implement this project.

### -0)

### 3.5 Conclusion

The discussion above is including the methodology that will be used in designing a Pipelined Multiplier Accumulator. There are two methods of design will be used in this project, which are top-down design and bottom-up design. Top-down design will be used in design part, meanwhile the bottom-up design will be used in implementation part. This chapter also discuss about the hardware description language that will be used in simulation and testing. VHDL is choosing considered on the comparison that had been discussed above. ASIC and programmable devices, which is CPLD and FPGA and the comparison of this two devices also discussed in this chapter. From all the fact above, FPGA is choosing to be used in this project.

The next chapter (Chapter 4) will discuss about Pipelined Multiplier Accumulator Analysis and Design. That chapter will discuss about system analysis and design for a pipelined MAC. The discussion will include discussion about the system overviews, conventional MAC and pipelined MAC. Besides that, the comparison between conventional MAC and pipelined MAC also will discuss in that chapter. That chapter also will discuss about signals controller that used in the pipeline multiplier accumulator and also the top-level design of this system. **Chapter 4**

## SYSTEM DESIGN

## -0)

### CHAPTER 4 SYSTEM DESIGN

### 4.1 Introduction

This chapter will be discussing about system analysis and design for a pipelined MAC. That discussion will be included with the pipelined MAC overview and design of the pipelined MAC. Furthermore, this chapter also will be investigated about the design of multiplier, accumulator and pipeline design in pipelined multiplier accumulator. The description of top-level design, black box and system's block diagram will also be presented to show in this chapter.

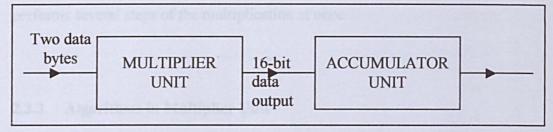

#### 4.2 System Overview

The Pipelined Multiplier Accumulator, which is implemented, will facilitate the arithmetic operations of multiplying pairs of 8-bit binary number and adding 16-bit binary numbers that is initially the multiplication result obtained.

In order to operate the system under a fast, continuous stream of data, the concept pipelining these multiplication and addition process is implemented in the design of the system unit (Refer Figure 2.3: Pipelined concept in system's operation; Chapter 2: Literature review; pg 19). Each stage of system is pipelined, so that it can perform on a continuous data. A control unit controls each stages of

the pipelined unit. The details of the control unit will be discussed in the following sections. (Section 4.6 : Signal Controller).

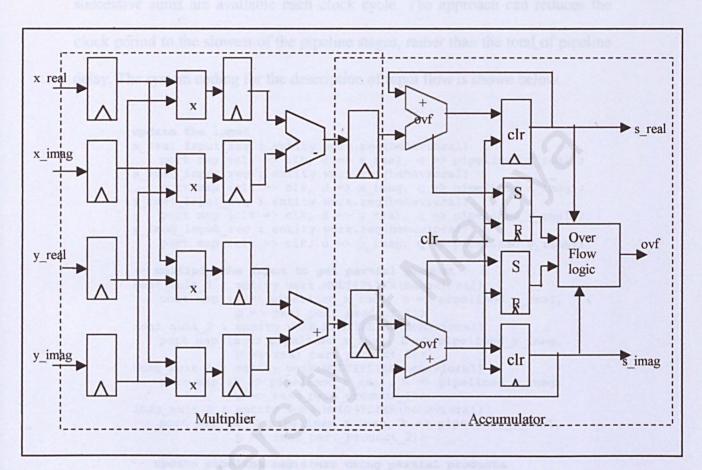

In the system's operation, two 8-bit signed fixed-point binary numbers (data) are multiplied by a multiplier block, while simultaneously two 16-bit signed fixed-point binary numbers are added together in an accumulator block which proceeds the multiplier block. It is in such way that a multiplication result is passed to the accumulator block (which is feedback to the block for next additional operation); in order to obtain the next output result.

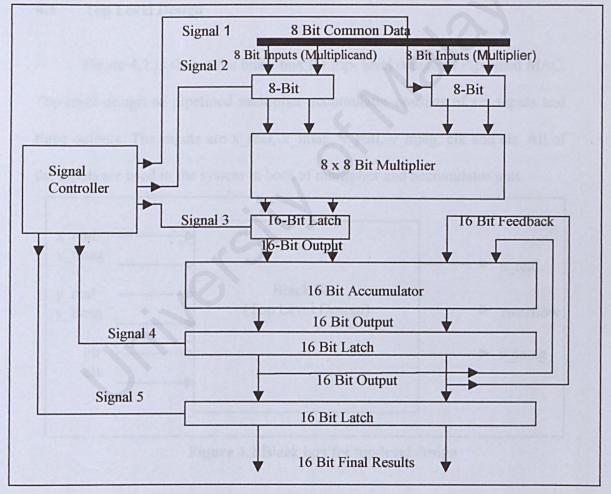

Figure 4.1 System's block diagram

For this design, synchronous transfer of data bit between the multiplier and accumulator blocks is used, where latches are used for latching data bits in and out of those block in order to synchronize the multiplication and addition operations. The clocking rates to these latches are controlled by a signal controller block, from which different rates of clock pulsing are generated and channeled to the respective latches. The system's block diagram is shown in Figure 4.1.

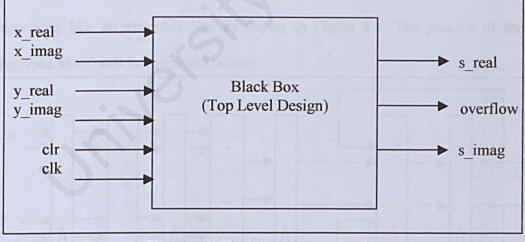

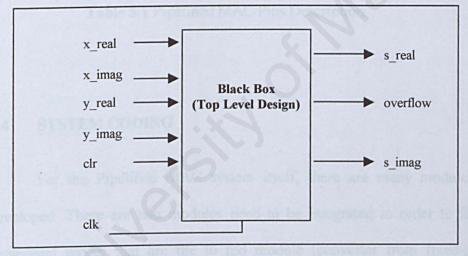

### 4.3 Top Level Design

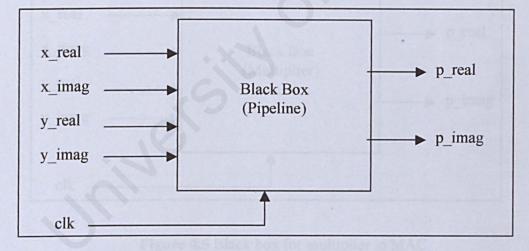

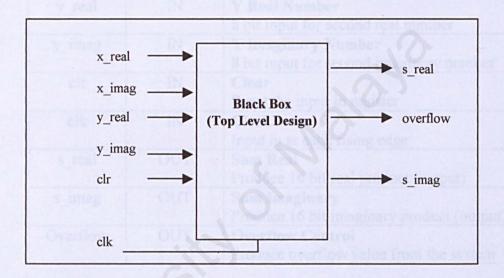

Figure 4.2 is shown the black box for top- level design of Pipelined MAC. Top-level design of pipelined multiplier accumulator consists of six inputs and three outputs. The inputs are x\_real, x\_imag, y\_real, y\_imag, clk and clr. All of the inputs are used in the system in both of multiplier and accumulator unit.

Figure 4.2 Black box for top-level design

-0

The x\_real, x\_imag, y\_real and y\_imag inputs will be used in multiplication operation of multiplier part and addition operation in accumulator part in the pipelined MAC. The 'clr' input only use in accumulator part to clear the pipeline register to zero and reset the overflow condition. Meanwhile the 'clk' will be used to control the clock signal.

The outputs are s\_real, s\_imag and overflow. All of this output except for overflow will appeared as a final sum of all operation in multiplier and accumulator. Overflow happened only in the certain case.

### 4.4 Pipeline in MAC

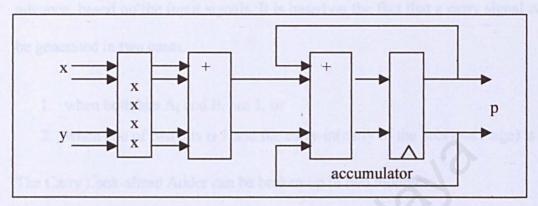

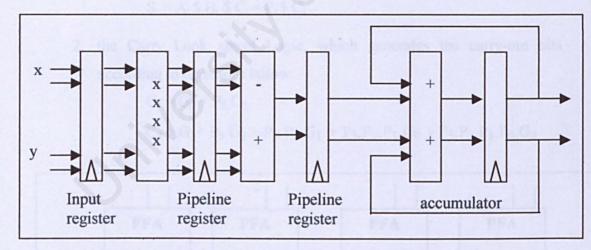

The main purpose of designing pipelined MAC is to avoid delay that occurs in multiplication operations. The pipelining process in pipelined MAC is organizing like an assembly line as shown in Figure 4.3. The process of the pipelined MAC will be discussed below.

Figure 4.3 Dataflow diagrams showing order of operations by the pipelined MAC

Firstly, the first pair of input numbers is stored in the input register on the first clock edge. During the first clock cycle, the multipliers calculate the partial products, while the system prepares the next pair of inputs. On the second clock edge the partial product are stored in the first pipeline register and the second pair of inputs numbers is entered into the input register. During the second clock cycle, the subtracter and adder produce the full product for the first input pair; the multipliers produce the partial products for the second input pair, while the system prepares the third input pair.

On the third clock edge, all input is stored in the second pipeline register, the first pipeline register and the input register. Then in the third clock cycle, the address accumulate the product of the first pair with the previous sum and the preceding stage operates on the second and third pairs, while the system prepares the fourth pair.

The sum in the accumulator is updated on the fourth clock edge. Thus, three clock cycles after the first input pair was entered into the input latch, the sum including this pair is available at the output of MAC. Thereafter, successive sums are available each clock cycle. The approach can reduces the clock period to the slowest of the pipeline stages, rather than the total of pipeline delay. [Ash, 96]

In pipeline case, initializing and restarting the pipeline should be considered. It is important to do this to accumulate sums of product of a number of an input sequences, one after another. The simplest approach is to include a 'clear' input to the accumulator register that forces its content to zero on the next

This causes the accumulator to reset at the same time as the product of the first pair of numbers reaches the second pipeline register. On the following cycle, this product will be added to the zero value forced into the accumulator. Three clock cycles after the last pair in the input sequence has been entered, the final sums will appears at the output of the MAC. Successive input sequences must separate by at least one idle cycle and reset the accumulator between summations. It is important to reset all values to zero before the next summation will be operates.

Figure 4.4 Black box for pipelined in MAC

### -0

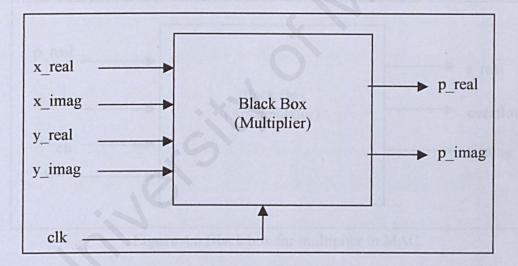

### 4.5 Multiplier in MAC

To form a partial product, MAC must perform four multiplications. Then, a subtraction and addition is executed to form the full product and finally two additions to accumulate the result. Since the operations must be performed in this order, the time taken to complete processing one pair of inputs is the sum of the delays for the three steps.

This delay may cause the bandwidth of the system to be reduced below a required minimum, in a high-performance digital signal processing application. Figure 4.5 is shown the black box for multiplier in MAC. The multiplier unit is consisting of five inputs and two outputs.

Figure 4.5 Black box for multiplier in MAC

### 4.6 Accumulator in MAC

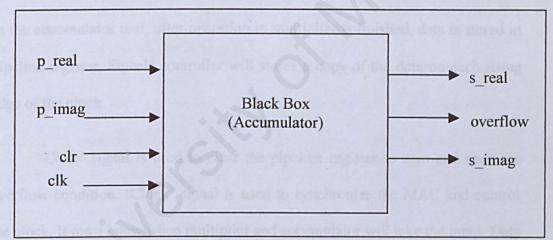

MAC calculates its result by taking successive pairs of complex number (that have been discussed in Chapter 2, Section 2.2.5), one of each from the two input sequences, forming their complex product and adding it to an accumulator register. Accumulator is initially cleared to zero and is reset after each pair of sequences has been processed. Refer Figure 2.2: Dataflow diagrams showing order of operations by the conventional MAC in Chapter 2: Literature review (pg 18) to look for dataflow in accumulator unit of Pipelined MAC. Figure 4.6 is shown the black box for accumulator in MAC. The multiplier unit is consisting of four inputs and three outputs.

Figure 4.6 Black box for multiplier in MAC

### 4.7 Signals Controller

It is an essential part of the whole system to generate clock pulse signals, which synchronize the processes in the multiplier and accumulator units, besides providing interrupt signal for the printer port. Signals controller is important to control stages of pipeline and the continuous of input data in pipeline MAC. Signals controller will work in both of multiplier and accumulator units.

In the multiplier unit, signals controller in the system will take the new input value when the clock is '1'. It is because at the time clock is '1'; latch is opened to allow data entered into the system. When the clock is '0', latch is closed and data cannot enter into the system. The process will operate at this time. In the accumulator unit, after operation in multiplier is finished, data is stored in pipeline register. Signals controller will stores a copy of the data on each rising edge of the clock.

'Clear' signal is used to clear the pipeline register to zero and reset the overflow condition. 'Clock' signal is used to synchronize the MAC and control the clock. It must know when multiplier and accumulator will take the input. Data entered when the clock is '1'.

Efficiency of signals controller part is greatly affects the reliability of the overall system. The design has been done carefully through the use of GateSim simulator, in order to obtain correct and stable output control signals for the entire system's operation. The simulator has been as essential supporting tool in detecting the weak points of the design. The weaknesses are fundamental basis for improvement of the design, although there are differences between the simulation and actual design. Basically, it operates in the same manner as the actual operation. As long as the differences are well defined and understood, the use of simulator is obvious, to be an important reference for the actual work.

### 4.8 Conclusion

The design and construction of the system is done in the way where simplicity and fast speed criterions are emphasized. Selections of construction method of Accumulator and Multiplier have been done through analyzing few method which are commonly used.

The Multiplier unit mainly determines the overall performance of the system. The multiplier design is much emphasized in order to select a suitable method for its construction. Besides that, efficiency of signals controller part is also greatly affects the reliability of the overall system.

The effectiveness of pipelining concept in the system's implementation is undeniable as the performance of the system is improved where the multiplication process is pipelined with the addition process. The next chapter (Chapter 5) will discuss about systems implementation. That chapter will discuss about system implementation for a pipelined MAC. The discussion will include discussion about the system implementation, description of **PeakFPGA Designer Suite FPGA Synthesis Edition** and the system coding. Besides that, the behavioral model also will discuss in that chapter.

## **Chapter 5**

# SYSTEM IMPLEMENTATION

### CHAPTER 5 SYSTEM IMPLEMENTATION

### 5.1 INTRODUCTION

To bring forward on designing a logic device for Pipelined Multiplier Accumulator, this chapter will take the reader to the description of **PeakFPGA Designer Suite FPGA Synthesis Edition.** These tools will be extensively used throughout the design implementation process. The coding for the system's modules is developed using the VHISC Hardware Description Language (VHDL) programming language (discussed before in Chapter 3.3 page 29). This chapter also will discuss about system development, the description of all pins in top-level design and system coding for Pipelined Multiplier Accumulator.

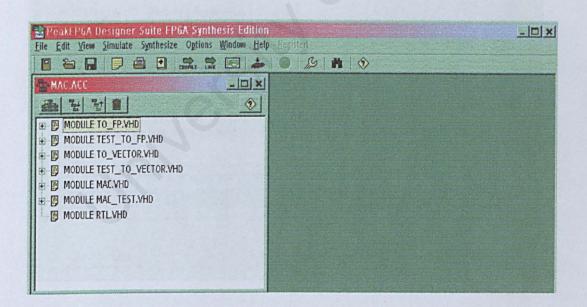

### 5.2 PeakFPGA DESIGNER SUITE FPGA SYNTHESIS EDITION

PeakVHDL is an advanced software product intended to help you use VHDL for digital design projects. PeakVHDL includes an integrated VHDL simulator, VHDL source file editor, Hierarchy Browser and other resources for VHDL users. To get started using PeakVHDL, we should load one of the sample projects included in the Examples subdirectory of PeakVHDL installation. The examples provided are intended to demonstrate a variety of useful VHDL concepts, including various methods of writing test benches. These examples will also help us to understand how to create and manage a PeakVHDL project.

| Br | eakl | PGA E | )esigne | r Suite FP6 | A Synth      | esis Ed | ition |  |  |  | - 0 × |

|----|------|-------|---------|-------------|--------------|---------|-------|--|--|--|-------|

|    |      |       |         | Synthesize  |              |         |       |  |  |  |       |

|    | -    | G     |         |             | onenie Lania |         | -     |  |  |  |       |

|    |      |       |         |             |              |         |       |  |  |  |       |

Figure 5.1 : Main Application Window

To load a sample project, select Open Project from the PeakVHDL File menu, and navigate to the Examples subdirectory of the PeakVHDL installation directory. Select one of the sample projects and open the .ACC file associated with that project. When we have opened a sample project, we will see two or more .VHD source files listed in the Hierarchy Browser window. We can double click on any file name listed to open a VHDL source file-editing window.

### Figure 5.2 : Hierarchy Browser Window

To process the project and start the PeakVHDL simulator (PeakSIM), select the top-most VHDL source file (the test bench) by clicking on it then choose Load Selected from the Simulate menu or click on the Load Selected button from the PeakVHDL toolbar. When we highlight the top-most module and choose Load Selected, the following occurs:

- All VHDL source file modules in the project are compiled in bottom-up order as determined by the Hierarchy Browser.

- The compiled source file modules are linked together (elaborated), and a .VX simulation executable is generated.

- The .VX simulation executable is loaded into the PeakSIM simulation application.

| Transcript                                                                                                                                                       |                                        |                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------|

| Compile Link Simulate                                                                                                                                            | Synthesize System                      |                          |

| DP VHDL Analyzer Version<br>Copyright by Protel Internal<br>All rights reserved.<br>Build Apr 19 1999.<br>Compiling entity MAC_TES<br>Compiling architecture BEN | ional, 1999.                           |                          |

| Tip: click on a line with a n                                                                                                                                    | umbered error message and click Jump t | o Line or Error Summary. |

| Jump to Line                                                                                                                                                     |                                        | Close                    |

Figure 5.3 : Transcript Window

If there are any errors during this process, they are reported to the PeakVHDL transcript window. If there are no errors, the PeakSIM application appears with your project loaded, ready for simulation. Refer to the PeakSIM online help for information about how to control simulation, monitor signals and debug your design.

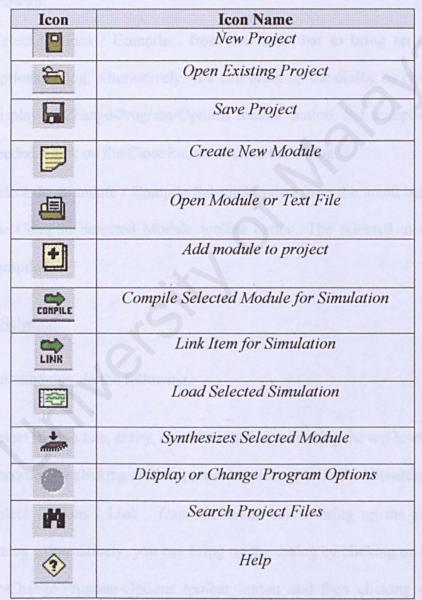

The main application window includes 13 toolbar buttons. These buttons, which can be toggled on or off are summarized below, from left to right. Note that as we move our cursor over a toolbar button, a tip appears that explains the function of that button.

- Create New Project same as File / New Project

- Open Existing Project same as File / Open Project

- Save Project same as File / Save Project

- Create New Module same as File / New Module

- Open Module or Text File same as File / Open Module

- Add Module to Project same as File / Add Module

- Compile Selected Module same as Compile / Compile Selected

- Link Selected Module same as Link / Link Selected

- Load Selected Simulation Executable same as Simulation

/ Load Selected

- Synthesize Selected Module same as Synthesize / Synthesize Selected

- Display or Change Program Options opens the Options dialogue with the Compile folder active (same as Compile / Options... or Options / Compile...)

• Help Contents - same as Help / Contents

### 5.3 PIN DESCRIPTION

To describe the behavior of digital systems in VHDL code, a designer must plan the specification of each pin and register. Therefore, the following discussion will be concentrated on the design specification of the Pipelined Multiplier Accumulator pins and registers. The function of each pin and register will also be discussed in this section.

Figure 5.4 : Pipelined MAC Top Level Design Symbol

Table 5.1 will describe the function and the description of all PipelinedMAC pins available at the top-level design (Figure 5.4) of the VHDLimplementation. The 9 pins Pipelined MAC are describe as follows:

A Pipelined Multiplier Accumulator : Pipeline

| Pin                                         | In/out       | Description                               |

|---------------------------------------------|--------------|-------------------------------------------|

| x real                                      | IN           | X Real Number                             |

| ed which is                                 |              | 8 bit input for first real number         |

| x imag                                      | IN           | X Imaginary Number                        |

| accuse that at                              | adder model  | 8 bit input for first imaginary number    |

| y real                                      | IN           | Y Real Number                             |

| acculoulator                                |              | 8 bit input for second real number        |

| y imag                                      | IN           | Y Imaginary Number                        |

|                                             |              | 8 bit input for second imaginary number   |

| clr                                         | IN           | Clear                                     |

| for and per/ros                             |              | Reset the input in register               |

| clk                                         | IN           | Clock                                     |