# CIRCUIT DESCRIPTION AND CIRCUIT SIMULATION USING C++

Perrustakaan SKTM

## **ROZITA BT OTHMAN**

WEK010397

Faculty Of Computer Science And Information Technology,

University Of Malaya

Mac 2005

### ABSTRACT

Techniques used for circuit description have often been treated differently from the methods used to simulate hardware. This report will attempt to demonstrate how a common platform, and hence a uniform environment, can be established to both describe and simulate hardware, using a programming paradigm known as *objectoriented programming* as supported by the C++ language. This paradigm is powerful enough to allow a hierarchical description of the hardware and at the same time provide an extensible method for its simulation.

This report will provide a brief overview of C++ and its support for the object-oriented programming paradigm.

## ACKNOWLEDGEMENT

Utter most gratitude goes to the almighty Allah for all the confidence and patience in the completion of my thesis

I would like to express my deep gratitude to my supervisor Mr. Yamani Idna Idris for the tremendous help he has given me during this project, technical advise and thoughtful comment. And also to my moderator Ms. Rafidah Mohd Noor for her valuable advise and motivation.

Also taking this opportunity expressing my thanks to all fellow members and especially the family of Computer Science and Networking for their support to face the difficulties and challenging time.

Finally but not least, I am much obliged to my lovely husband, Mawardi Saad and my parents who have been given invaluable support and inspiration to me throughout my university life.

# **TABLE OF CONTENTS**

| Abstract           | i   |

|--------------------|-----|

| Acknowledgement    | ii  |

| Tables of Contents | iii |

| List of Figures    | ix  |

# **CHAPTER I: INTRODUCTION**

| Introduction       | 1                                                                       |

|--------------------|-------------------------------------------------------------------------|

| Problem Definition | 3                                                                       |

| Scope              | 4                                                                       |

| Objectives         | 5                                                                       |

| Scheduling         | 6                                                                       |

|                    | Introduction<br>Problem Definition<br>Scope<br>Objectives<br>Scheduling |

# CHAPTER II: LITERATURE REVIEW

| 2.1 | C++ B  | Background and History                       | 7  |

|-----|--------|----------------------------------------------|----|

|     | 2.1.1  | Features Borrowed from Other Languages       | 8  |

|     | 2.1.2  | C++ Versus C                                 | 9  |

| 2.2 | Objec  | t Oriented Programming                       | 10 |

|     | 2.2.1  | The Problem of Complexity                    | 11 |

|     | 2.2.2  | The Problem of Classification                | 13 |

| 2.3 | Featur | res of Object-Oriented Programming Languages | 13 |

|     | 2.3.1  | Data Encapsulation                           | 14 |

|     | 2.3.2  | Inheritance                                  | 15 |

|     | 2.3.3  | Dynamic Binding of Function Call             | 15 |

| 2.4 | VHDI   | (VHSIC Hardware Description Language)        | 16 |

|     | 2.4.1  | Basic Language Organization                  | 17 |

# CHAPTER IV: SYSTEM ANALYSIS

| 4.1 | Syster | n Requirement Specification          | 40 |

|-----|--------|--------------------------------------|----|

| 4.2 | Functi | onal Requirement                     | 41 |

|     | 4.2.1  | Classification of Circuit Components | 41 |

| 4.3 | Non-F  | unctional Requirement                | 46 |

|     | 4.3.1  | Correctness                          | 47 |

|     | 4.3.2  | Reliability                          | 47 |

|     | 4.3.3  | Response Time                        | 47 |

|     | 4.3.4  | Expandability                        | 48 |

| 4.4 | Consi  | deration of Programming Language     | 48 |

| 4.5 | Hardy  | vare Requirement                     | 50 |

# CHAPTER V: SYSTEM DESIGN

| 5.1 | What  | is System Design                    | 51 |

|-----|-------|-------------------------------------|----|

| 5.2 | The M | lethod of Designing                 | 51 |

| 5.3 | Hardw | are Description Component           | 53 |

|     | 5.3.1 | Two-input AND Gate                  | 54 |

|     | 5.3.2 | Three-Input AND Gate                | 56 |

|     | 5.3.3 | S-R Latch                           | 58 |

|     | 5.3.4 | Full-Adder                          | 61 |

| 5.4 | Hardy | vare Simulation Using C++           | 62 |

|     | 5.4.1 | Circuit Simulation: Time and Queues | 62 |

|     | 5.4.2 | Signals and Signal Transmission     | 64 |

## CHAPTER VI: SYSTEM IMPLEMENTATION AND CODING

| 6.1 | Introd | uction                                | 68 |

|-----|--------|---------------------------------------|----|

| 6.2 | Progra | am Coding                             | 68 |

|     | 6.2.1  | Coding Style                          | 69 |

|     | 6.2.2  | Code Documentation                    | 69 |

|     | 6.2.3  | Internal documentation                | 69 |

|     | 6.2.4  | Naming Convention                     | 70 |

|     | 6.2.5  | Modularity                            | 70 |

|     | 6.2.6  | Readability                           | 70 |

|     | 6.2.7  | Robustness                            | 70 |

|     | 6.2.8  | Maintainability                       | 71 |

| 6.3 | Imple  | mentation of the Simulation Algorithm | 71 |

| 6.4 | Virtua | al process () function                | 74 |

| 6.5 | Code   | Modules/files                         | 76 |

# CHAPTER VII: SYSTEM TESTING

| 7.1 | Introduction                              | 78 |

|-----|-------------------------------------------|----|

| 7.2 | Sample Simulation of Three-Input AND Gate | 79 |

| 7.3 | Sample Simulation of RS-Latch             | 83 |

## **CHAPTER VIII: DISCUSSION**

| 8.1 | Introdu | etion                             | 87 |

|-----|---------|-----------------------------------|----|

| 8.2 | Problem | n Encountered and Solutions       | 88 |

|     | 8.2.1   | Problems in getting the resources | 88 |

|     | 8.2.2   | Lack of Knowledge in the Language | 88 |

|     | 8.2.3   | Time Constraint                   | 89 |

| 8.3 | Project | Strength                          | 89 |

|     | 8.3.1   | Predefined Library                | 89 |

|      | 8.3.2 Easy to Create Sample Gate | 89  |

|------|----------------------------------|-----|

| 8.4  | Project Limitation               | 90  |

| 8.5  | Future Enhancement               | 90  |

| Cond | clusion                          | 91  |

| App  | endix A: .CPP Files              | 92  |

|      | comp.cpp                         | 93  |

|      | complib.cpp                      | 96  |

|      | connect.cpp                      | 99  |

|      | port.cpp                         | 101 |

|      | signal.cpp                       | 104 |

|      | wire.cpp                         | 106 |

|      | main.cpp                         | 109 |

| App  | endix B: Header Files            | 117 |

|      | comp.h                           | 118 |

|      | complib.h                        | 119 |

|      | connect.h                        | 121 |

|      | port.h                           | 122 |

|      | signal.h                         | 123 |

|      | wire.h                           | 124 |

|      | sim.h                            | 125 |

| App  | endix C: Output                  | 126 |

|      | Output 1: Two-input AND Gate     | 127 |

|      | Output 2: Three-input AND Gate   | 127 |

|      | Output 3: RS-Latch               | 128 |

|      | Output 4: Half Adder             | 129 |

| Refe | erences                          | 130 |

# LIST OF FIGURES

| Figure 2.1: The Problem of Complexity                                | 12 |

|----------------------------------------------------------------------|----|

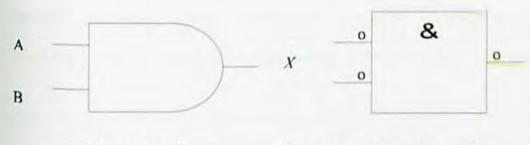

| Figure 2.2(a): Logic Symbol of Two-input AND Gate                    | 18 |

| Figure 2.2(b): VHDL Description of a 2-input and operator            | 18 |

| Figure 2.3(a) logic schematic                                        | 20 |

| Figure 2.3(b) VHDL description of majority function                  | 20 |

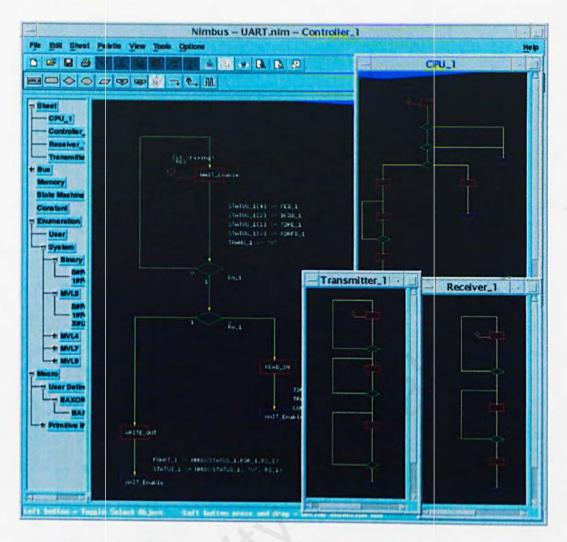

| Figure 2.4: The Nimbus display of 3 threads of the UART model        | 27 |

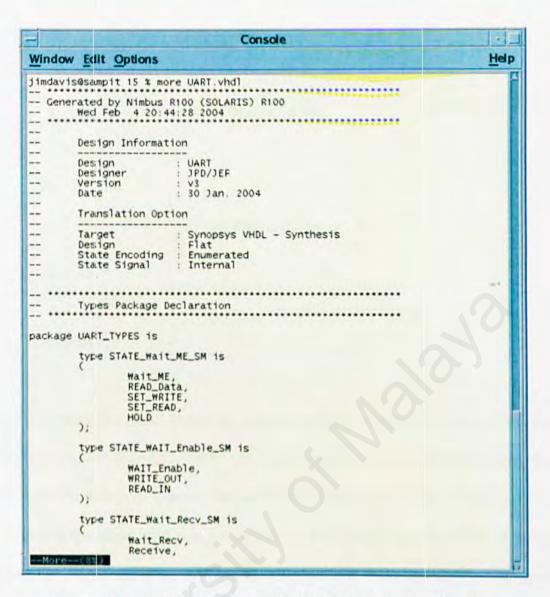

| Figure 2.5:. Viewing the Generated VHDL Code in Text Window          | 28 |

| Figure 3.1: The core workflows and the phases of the Unified Process | 33 |

| Figure 5.1: Standard logic symbols for the AND gate with two input   | 54 |

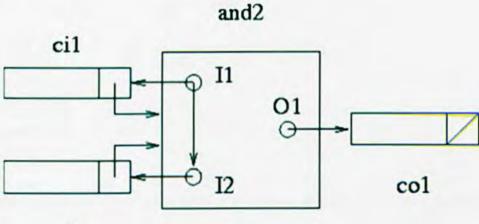

| Figure 5.2: Two-Input AND Gate with External Wires                   | 56 |

| Figure 5.3: Three-Input AND Gate with External Wires                 | 58 |

| Figure 5.4: Active-LOW input S'-R' latch                             | 59 |

| Figure 5.5: RS-Latch with External Wires                             | 60 |

| Figure 5.6(a): Full-Adder Logic Diagram for Sum                      | 61 |

| Figure 5.6(b): Full-Adder Logic Diagram for Carry                    | 62 |

| Figure 7.1: Three-Input AND Gate Before Simulation                   | 79 |

| Figure 7.2: Three-Input AND Gate After Simulation                    | 82 |

| Figure 7.3: RS-Latch Before Simulation                               | 83 |

| Figure 7.4: RS-Latch After Simulation                                | 86 |

## CHAPTER 1

## INTRODUCTION

#### 1.1 Introduction

As high-level computer programming languages become increasingly more powerful and abstract, there is a tendency amongst the computing society to use such general purpose languages for the benefit of their own fields of research and study. Instead of using highly specific languages, which are usually restricted in their scope and availability, members of both the software and hardware community are tempted to use higher level languages that are more accessible and flexible. This report will show how one such high-level language and its support for the object-oriented programming paradigm can be used for both the description and simulation of hardware modules.

The advantages of using a popular general purpose language for hardware description and simulation are multifold. Firstly, if the hardware designer is already familiar with the language from software development, then all he or she has to do is to apply the language to the problem of hardware description and simulation. This means that the designer does not have to learn an entirely new language with its own peculiar syntax rules and idiosyncrasies. Secondly, general purpose languages have a much greater population of users than do languages which specifically support hardware description. Therefore, translators, compilers and/or interpreters for such high-level languages are usually more readily available, efficient and reliable. Thirdly, using the same language to both describe and simulate hardware creates a more uniform and consistent environment for the user. This uniform environment results in more control, since the designer does not have to keep track of one language for circuit description and an entirely different language for parsing the circuit description and simulating it.

Obviously, some high-level languages are better suited for hardware description and simulation than others. A language which can be used for hardware description and simulation must permit the designer to specify the hardware in an intuitive and hierarchical manner, consistent with how the designer thinks. In addition, such a language must be easily extensible so that new modules can be easily added without any modifications being made to the simulation code. Ideally, such a language must also provide support for circuit designs at several levels of abstraction and should also give the designer the choice of either using a ``bottom-up" or a ``top-down" approach to circuit description.

One language which appears to satisfy all the requirements for a hardware description and simulation language is C++. In addition to providing support for objectoriented programming, this language is also undergoing standardization by ANSI, which means that the language mechanisms and features used by this report should be portable across most C++ compilers. Since use of the language is undergoing exponential growth, C++ compilers and translators have be written for a variety of platforms. Therefore, C++ is available to a wide community of programmers.

## 1.2 Problem Definition

When designing a hardware, commonly we used HDL or VHDL hardware description language. There are some major obstacles to do successful system-on-chip. Some of the obstacles are:-

- (i) There is a lack of a single system-level environment that can be used throughout the design flow. While algorithms might be designed at high level in C, gates still have to synthesised out of HDL. Each manual format translation, no matter how small, is a possible source of errors.

- (ii) The designer has insufficient control over the design process. He or she has to accept the result that (synthesis) tools produce. This is result of those tools being sold as closed boxes. Assembling a system level design flow out of such tools however requires an open environment.

- (iii) There is lack of a systematic verification strategy. There are as many testbenches as there are tools used the design flow.

Since hardware description languages are closely related to programming language, it is natural to try to adapt object-oriented technique to hardware description.

#### 1.3 Scope

In this project scope, there are two major sections dealing with C++ and the object-oriented paradigm, circuit description and circuit simulation using C++.

- The first section serves as an introduction to the basic mechanics and techniques associated with the object-oriented paradigm and how C++ provides support for this paradigm.

- Describe and simulate circuits using this paradigm. It will be shown how concepts of object-oriented programming map cleanly into the problem of hardware description.

## 1.4 Objectives

There are two types of objective that must be achieve, so that the target of system development can successfully accomplish.

- 1. General/overall project objective

- 2. Explicit project objective.

Some of the overall project objectives are:-

- (i) To understand system process or system development

- (ii) To practice all the knowledge that we have learned such as skill in system analysis, system design and programming and also system development.

- (iii) To adapt with all the software that related in designing system.

- (iv) To understand all the problem and constraint in developing system and software.

Explicit project objectives are:-

- To discuss the advantages of C++ as object-oriented programming to describe and simulate hardware.

- (ii) To introduce classification of circuit components which is component, connector, wire and port programming in C++.

- (iii) To describe simple hardware using C++ programming which is AND gate,

RS-Latch, Adder and the result of simulation.

## 1.5 Schedulling

The bar chart below shows the activities of each process phase that will be carried out through the development of the system. It will take an approximate time of 9 months to finish the whole thesis project. Starting on the first phase, which is system analysis from June to July. At this phase, information is collected on systems available and study is made on methodology that will be used in this project. The second phase starts from August until September, which is working on the system design. At the beginning of October and second part of the thesis will be started by the implementation of the system, which is the system coding. System testing will be carried out at the middle of December until the end of January. The system will be tested to check if it's free from errors.

The last phase of system development is the system evaluation. It starts at the end of January until the end of February. The required system output will be checked in this phase.

|     |                                       |      | Syste | m De | velopm | ent  |     |     |     |     |     |

|-----|---------------------------------------|------|-------|------|--------|------|-----|-----|-----|-----|-----|

| No. | Year                                  | 2004 |       |      |        | 2005 |     |     |     |     |     |

|     | Phase & Month                         | Jun  | Jul   | Og   | Sep    | Okt  | Nov | Dis | Jan | Feb | Mac |

| 1   | Identify Constraint<br>and Objectives | -    | . *   |      |        | -    |     |     |     |     |     |

| 2   | Identify Information                  | K    |       |      | _      |      |     |     |     |     |     |

| 3   | System Analysis                       | 0    | -     |      | _      |      |     |     |     |     |     |

| 4   | System Design                         |      |       |      | -      | -    | -   |     |     |     |     |

| 5   | Documentation and<br>Develop Software |      | -     |      |        |      |     |     |     |     |     |

| 6   | System Testing and<br>Maintenance     |      |       |      |        |      |     |     | _   |     | -   |

| 7   | Implement & System<br>Evaluation      |      |       |      |        |      |     |     |     |     | -   |

#### CHAPTER II

#### LITERATURE REVIEW

## 2.1 C++ Background and History

C++ is a programming language developed at AT&T Bell Laboratories by Bjarne Stroustrup in the early 1980's. The language was designed with the intent of merging the efficiency and conciseness of C with the object-oriented programming features of SIMULA-67. Since its creation, the language has evolved rapidly and several new features have been added since its initial release in 1985. The language also promises to provide support for several other useful mechanisms such as parameterized types and exception handling in the near future. A formal ANSI-C++ committee (X3J16) has since been established to help develop an accurate and reliable standard for the language which should eliminate most, if not all, ambiguities in the C++ compilers and translators of today. It is expected that this committee will adopt most of the rules present in the ANSI base document *The Annotated C++ Reference Manual* as written by Ellis and Stroustrup. With a few modest exceptions, C++ can be considered a superset of the C programming language. While C++ is similar to C in syntax and structure, it is important to realize that the two languages are radically different. C++ and its support for object-oriented programming provide a new methodology for designing, implementing and ease of maintaining software projects which C, a structured programming language, is unable to support. Extensive libraries are available for the C programming language; consequently, a deliberate effort was made on behalf of the developers of C++ to maintain backward compatibility with C. Any major deviation from the C programming language would have meant that all the libraries available for C would have to be tediously rewritten for C++. This would have severely limited the usefulness of C++ in an environment where C libraries were used extensively.

## 2.1.1 Features Borrowed from Other Languages

C++ is largely an amalgamation of several other programming languages. Obviously, C++ inherits most of its characteristics, such as its syntax, looping mechanisms and the like, from C. A part from C, C++ borrows most heavily from the aforementioned SIMULA-67 programming language. Nearly all the support that C++ provides for object-oriented programming comes from this language. The concept of a class and the so-called virtual function mechanism are a few of the features present in SIMULA-67 which have been integrated in C++.

To a limited extent, C++ also borrows some programming mechanisms from Algol-68. These include support for operator overloading and the declaration of variables almost anywhere in the code. The newer C++ compilers will provide support for parameterized types and exception handling, concepts borrowed from Ada and Clu.

#### 2.1.2 C++ Versus C

When a user defines a type in C++, support is provided in the language to permit that type to behave in a manner similar to types already built into the language. The user may define how the standard operators act upon these user defined types (operator overloading) and how these type can be converted to another type (user defined conversions). The user may also specify how memory is allocated or deallocated when an instance of that type is created or destroyed. This is done through the use of constructors and destructors which are called implicitly by the compiler when an instance of that type is brought into and taken out of scope respectively.

C++ provides support for function prototypes, hence enabling strong type checking of function parameters to take place during compilation. In addition, C++ provides support for the *pass by reference* mechanism and also supports default arguments to functions. This means that should a function require an argument that often has the same value, the user can default the argument to that value and not pass that parameter when the function is called. In the few cases where the function has to be called with a different value for the default argument, the user simply passes that argument into the function and the new value overrides the default value.

The most important features which C++ provides support for are data encapsulation, inheritance and runtime binding which form the foundation for the language's support for object-oriented programming.

## 2.2 Object-Oriented Programming

The object-oriented paradigm was first conceived in the 1960's and implemented in languages such as SIMULA-67. One of the initial concerns with early object-oriented languages was their efficiency. Programs written using structured languages, such as Pascal and C, executed faster than programs written using early object-oriented languages. Although programs which used the object-oriented paradigm were more extensible and easier to maintain from a programmer's point of view, an unacceptable price had to be paid in the program's runtime behaviour. Recently, however, the runtime execution of object-oriented programs has improved considerably. This has been due in part to both the development of faster hardware and the creation of efficient languages and compilers which support object-oriented programming, such as C++. These facts, in addition to the ever-increasing accessibility of object-oriented languages to the common programmer has created a major evolution in the area of software development.

There is, as yet, no universally agreed upon definition of exactly what constitutes object-oriented programming. Booch suggests:

10

"Object-oriented programming is a method of implementation in which programs are organized as cooperative collections of objects, each of which represents an instance of some class, and whose classes are all members of a hierarchy of classes united via inheritance relationships."

From this definition, one can infer that object-oriented programming consists of instantiating a number of objects which communicate with one another so as to achieve some desired behaviour. This paradigm is natural with how humans see the world; as a series of cause-effect relationships, where an action performed on one object has effects on the objects with which it communicates.

## 2.2.1 The Problem of Complexity

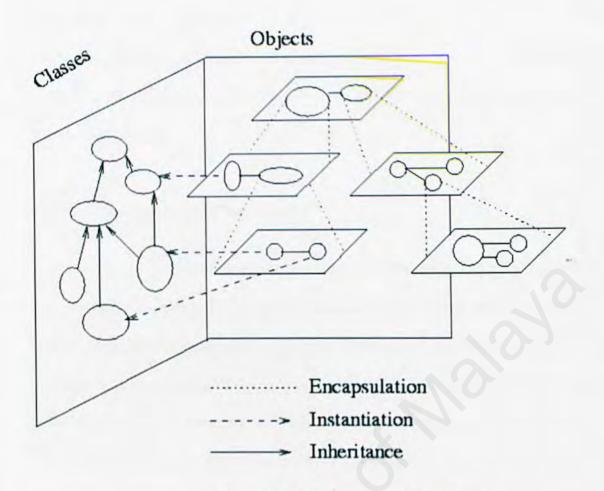

Object-oriented programming is particularly useful for reducing problems of complexity associated with the writing of large scale software packages. It is useful to think of a typical complex system as consisting of two orthogonal planes of hierarchy (**Figure 2.1**).

Figure 2.1: The Problem of Complexity

The first plane consists of a set of *classes*, each of which acts as a "blueprint" for the instantiation of *objects*. This plane contains a hierarchy known as the "is a kind of" relationship. Any class, D, in the plane which points to another class, B, is said to be *a kind of* class B. All the properties of class B (commonly called a *base class*) are passed down to class D (referred to as a *derived class*). As can be seen from the diagram, a derived class can be used as the base class of another; and a class can be specified as being "a kind of" two or more classes. This "is a kind of" hierarchy is supported in object-oriented languages through the mechanism of *inheritance*. The second plane consists of a series of *objects* which, as mentioned above, are instantiated from the classes of the first plane. This hierarchy is called the "is a part of" relationship and is achieved through the encapsulation, or aggregation, of classes. The hierarchy suggests that one object may be comprised of several objects; each of which can be made up of even more objects.

## 2.2.2 The Problem of Classification

One of the major problems encountered by designers of object-oriented software is *classification*; that is, finding which classes should be grouped together under a shared base class. When attempting to perform classification on the problem space, several issues must be addressed. For example, the designer must decide which properties should be used to determine commonality. The classification should also be flexible enough to permit the introduction of new objects into the system which appear to belong to neither class nor appear to have properties of several classes.

#### 2.3 Features of Object-Oriented Programming Languages

Object-oriented programming languages support three features: data encapsulation, inheritance and dynamic binding of function calls. Each helps the programmer build more abstract, powerful and malleable data types.

#### 2.3.1 Data Encapsulation

Data encapsulation, sometimes referred to as data hiding, is the mechanism whereby the implementation details of a class are kept hidden from the user. The user can only perform a restricted set of operations on the hidden members of the class by executing special functions commonly called *methods*. The actions performed by the methods are determined by the designer of the class, who must be careful not to make the methods either overly flexible or too restrictive. This idea of hiding the details away from the user and providing a restricted, clearly defined interface is the underlying theme behind the concept of an *abstract data type*.

The advantage of using data encapsulation comes when the *implementation* of the class changes but the *interface* remains the same. The concept of data encapsulation is supported in C++ through the use of the public, protected and private keywords which are placed in the declaration of the class. Anything in the class placed after the public keyword is accessible to all the users of the class; elements placed after the protected keyword are accessible only to the methods of the class or classes derived from that class; elements placed after the private keyword are accessible only to the methods of the class.

As a convention, calling a method of an object instantiated from a class is commonly referred to as sending a *message* to that object.

14

#### 2.3.2 Inheritance

Inheritance is the mechanism whereby specific classes are made from more general ones. The child or derived class inherits all the features of its parent or base class, and is free to add features of its own. In addition, this derived class may be used as the base class of an even more specialized class.

Inheritance, or derivation, provides a clean mechanism whereby common classes can share their common features, rather than having to rewrite them.

Inheritance is supported in C++ by placing the name of the base class after the name of the derived class when the derived class is declared. It should be noted that a standard conversion occurs in C++ when a pointer or reference to a base class is assigned a pointer or reference to a derived class.

## 2.3.3 Dynamic Binding of Function Calls

Quite often when using inheritance, one will discover that a series of classes share a common behaviour, but how that behaviour is implemented is different from class to class. Such a situation is a prime candidate for the use of dynamic or runtime binding which is also referred to as *polymorphism*.

C++ implements dynamic binding through the use of *virtual* functions. While function calls resolved at runtime are somewhat less efficient than function calls resolved statically, Stroustrup notes that a typical virtual function invocation requires just five more memory accesses than a static function invocation. This is a very small penalty to pay for a mechanism which provides significant flexibility for the programmer, as will be shown later.

It is from inheritance and runtime binding of function calls that object-oriented programming languages derive most of their power. Some problems lend themselves very well to these two concepts, while others do not. As Stroustrup notes:

"How much types have in common so that the commonality can be exploited using inheritance and virtual functions is the litmus test of the applicability of object-oriented programming."

## 2.4 VHDL (VHSIC Hardware Description Language)

VHDL is one of the computer language for describing digital systems. VHDL is a hierarchical acronym denoting VHSIC Hardware Description Language; VHSIC in turn, denotes Very High Speed Integrated Circuits. The United States Department of Defense Very High Speed Integrated Circuits (VHSIC) Program initiated the design of VHDL to support the development of a new generation of digital system technology. The design of VHDL formally began in 1983 and after a series of several iterations and versions, culminated in 1987 with the acceptance of VHDL as an IEEE (Institute of Electrical and Electronic Engineers) standard.

#### 2.4.1 Basic Language Organization

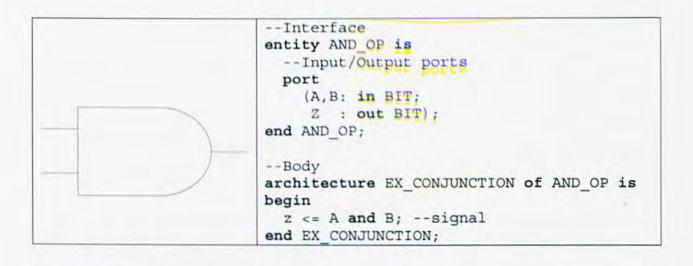

Figure 2.2(a) shows the graphical symbol and VHDL model of a 2-input and operation. The VHDL model shown in Figure2.2(b) comprises a design entity, which is the basic construct in VHDL for modeling a digital system. The digital system can be physical piece of hardware that has been designed or a conceptual piece of hardware that is being designed.

VHDL design entity is composed of two parts: an *interface* and a *body*. The interface is denoted by the keyword **entity** and the body is denoted by the keyword **architecture**. A convenient way to view the roles of the *interface* and a *body* is to imagine a digital system enclosed inside a casing or black box. The *interface* describes aspects of the digital system visible outside the black box that define the boundary between the system and its environment, such as signals that flow into and out of the box. The *body* describes aspects of the digital system visible outside the black box that define the black box that define box. The *body* describes aspects of the digital system inside the black box that define the black box that define box.

Figure 2.2(a): Logic Symbol

Figure 2.2(b): VHDL Description of a 2-input and operator

## 2.4.2 Language Organization of VHDL

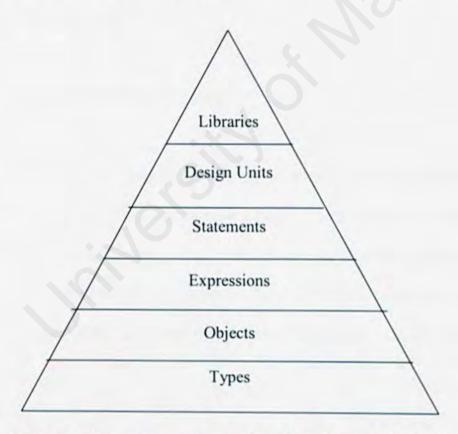

From the base of pyramid, predefined and user-defined types define data "templates" or sets. Objects, such as signals, hold values if the defined data types. Expressions combine operations with objects to yield new values, which are used by statements to describe aspects of digital hardware, Statements are contained within design units and design units are, in turn, contained within libraries.

The design units in VHDL are the following:

- Primary Design Units

- 1. Entity Declaration

- 2. Package Declaration

- 3. Configuration Declaration

- Secondary Design Units

- 1. Architectural Body

- 2. Package Body

## 2.4.3 Structural Modeling in VHDL

Modeling logic schematic or netlists introduces a descriptive style called structural modeling. Structural modeling defines the behavior of a design entity by defining the components that comprise the design entity and their interconnection. A structural model implicitly or indirectly defines function because the design entity input/output transform can be derived knowing the constituent and their behaviors.

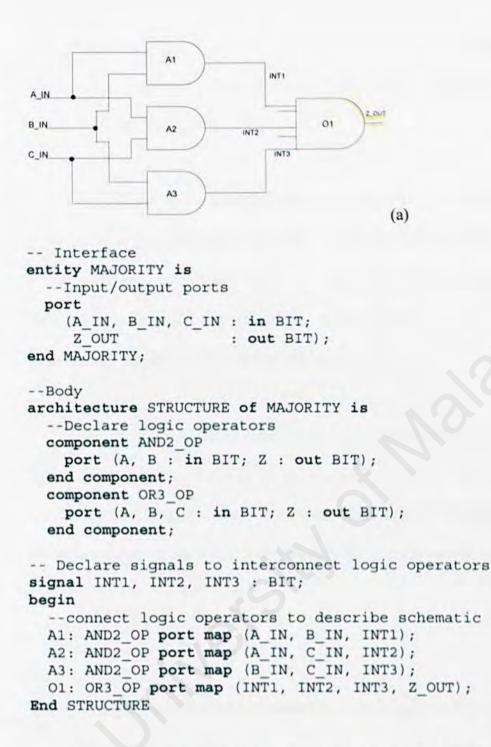

Figure 2.3(a) and 2.3(b) show the logic schematic and VHDL description of majority function.

From the **Figure** 2.3, the declarative part of the architecture STRUCTURE contains three declarations: two component declarations and one signal declaration. The signal declaration declares three signals.

Component declarations start with the reserved keyword component, followed by the name of the component. The AND2\_OP component has two input ports, A and B, and one output port, Z, all of type BIT. The OR3\_OP component has three input ports, A, B, and C and one output port Z, all type BIT. Finally the keywords end component completes a component declaration.

We also need signals to interconnect the component instances. The input/output signals for the majority function, A\_IN, B\_IN, C\_IN and Z\_OUT are declared in the definition of the design interface. Port map clause defines the mapping between which signal are connected to which component ports, in other words, how a component is 'wired-up'

## 2.5 Comparison in Object-oriented C++ Technology and VHDL

## 2.5.1 Object-oriented design strategies

OO programming presents a number of powerful design strategies based on practical and proven software engineering techniques expressed by means of the corresponding object-oriented software programming language structures. They are fundamental and are encountered in different problem-solving contexts and without doubt in hardware design problem-solving context too.

Widely used standard hardware description languages like VHDL or Verilog do not support all of the variations of each of these strategies. Therefore the OO programming is not completely available with standard HDLs.

## 2.5.2 Abstraction and Separation.

Abstraction: A named, tangible representation of the attributes and behavior relevant to modeling a given entity for some particular purpose." According to the purpose of the design, a single entity may have many valid abstractions. The widely used abstraction in hardware design is a hardware component or a "primitive" expressed in the two domains:

- Structural domain: a component is described in terms of an interconnection of more primitive components.

- (ii) Behavioral domain: a component is defining by its input/output response.

In VHDL, the primary entity is called a design entity; it corresponds to a module in SC. In VHDL only structural domain abstraction can be expressed. SC provides additional types of abstraction: communication abstractions can be expressed through the channels, and the ordinary C++ class concept can be used to express the behavioral abstractions. These additional abstractions are very important in H/S co design, allowing the designer to commit to a particular H/S partitioning late in the design process. In the pure hardware modeling these abstractions are also very important since they enable transaction based modeling which are very efficient regarding simulation performance. They are also important in inheriting specific behaviors and attributes when designing a library of components. CAD houses were forced to describe these libraries outside of VHDL, due to the lack of behavioral abstractions.

"Separation: the independent specification of an interface and one or more implementations of that interface."

In VHDL, a design entity consists of two different types of descriptions: the interface description and one or more architectural bodies. In hardware design the interface is presented by the description of entity's inputs and outputs. The architectural bodies can specify the behavior of the entity or a structural decomposition of the entity using more primitive components. In software engineering, an interface defines an external aspect that must be understood to use the software. This is a more general notion than just object inputs and outputs, it can abstract the actions that the object can use to interact with its environment, such as read, write actions for a bus object. The abstraction and separation concepts in the OO programming are expressed by means classes and objects. Each class has private and/or public members. Access from outside to private members is very limited allowing the notion of encapsulation.

"Encapsulation: can be defined as the restriction of access to data within an object to only those methods defined by the object's class".

The last software structure to which the abstraction and separation strategies are mapped is an object.

"Object: a distinct instance of a given class that encapsulates its implementation details and is structurally identical to all other instances of that class." Multiple instantiations of a given class can be made and each of them represents a distinct object. In VHDL, the notion of object corresponds to the one of a component instance that is used to create unique references to lower-level components. In SC, we may have a richer instantiation mechanism where an instance of an object can be an instance of a subclass of the declared type.

#### 2.5.3 Composition

"Composition: an organized collection of components interacting to achieve a coherent, common behavior." There are two forms of composition:

- (i) association

- (ii) aggregation

In an aggregation, the whole is visible and therefore accessible. In association the interacting parts may be shared by different compositions, as they are externally visible. The association purpose is to allow objects to be connected to each other or to know about each other. The association method of building systems is known as the plug-and-play technique and is widely used in the validation and evaluation of the created system.

In hardware design the structural design decomposition is a basic modeling technique and that is why the composition is naturally presented by syntactical HDL structures. In VHDL the composition is presented, in our opinion, in the aggregation form, the design entity is visible as a whole by the others ones. The association form of the composition, which is missing in VHDL can be very useful in the high-level descriptions of the designed system, in test-bench generations, in design exploration and in application of the incremental refinement methodology to a design. The different associations of objects encapsulating some functionality can be validated or verified to find the optimal solution.

#### 2.5.4 Generalization.

"Generalization: the identification, and possible organization, of common properties of abstractions." The generalization identifies commonalities among a set of entities. The commonality may be established in terms of attributes, behavior, or both. The generalization design strategy is directly connected to reusability. There are four forms of generalization expressed by object-oriented software structures:

(i) • Hierarchy;

- (ii) Genericity;

- (iii) Polymorphism;

- (iv) · Patterns;

## 2.6 Using the Synopsis Logic Synthesis Tools with Nimbus

Nimbus [14] is a tool set that allows the capture of digital systems models as a collection of concurrent Algorithmic State Machine (ASM) models. Nimbus provides a design editor, compiler, cycle-based simulator, and model translator to both synthesizable VHDL and Verilog HDL. The technology is industry-proven, having been embodied in tools from another vendor for over a decade, and having been used by such companies as 3-Com, Alcatel, Sony, Hitachi and Ricoh. The use of this technology is as a design capture and architecture exploration medium, as well as a means to clearly communicate design intent.

The Design Analyzer is an older tool set, which primarily is used in logic synthesis and analysis of circuit results for ASIC applications. The FPGA Compiler (FC2) is used for the specific needs of synthesizing circuits on FPGA devices.

Figure 2.4: The Nimbus display of 3 threads of the UART model

Figure 2.5:. Viewing the Generated VHDL Code in Text Window.

### CHAPTER III

### METHODOLOGY

#### 3.1 Methodology

A methodology is a system of methods and principles used in a particular subdiscipline of software design. There are a large number of these, reflecting the way in which software design in practice has specialized. Those which are mature usually are supported by specialist tools and techniques. A traditional view of design in software engineering is analogous to building a cathedral: we make careful, comprehensive blueprints; use these as the reference point for coordinating architects and craftspeople; and ensure that the individual components connect precisely in the way described in our blueprints. We shall look at an example of this style of design: the Unified Process this, however, is not the only approach available. We also can adopt a less prescriptive, opportunistic style of design where a greater emphasis is placed on rapid revision of blueprints and the artifacts built from them. In order to get the overview requirement of the Circuit Description and Elementary Hierarchical Circuit Simulation Using  $C_{\pm\pm}$ , an analysis to this topic is needed. The purpose of the analysis is to determine the entire functional requirement and also non-functional requirement for the tool.

### 3.2 Unified Process

The Unified Process is a software engineering process. It provides a disciplined approach to assigning tasks and responsibilities within a development organization. Its goal is to ensure the production of high-quality software that meets the needs of its endusers, within a predictable schedule and budget. (Ali Bahrami, 1999)

The Unified Process is a traditional "cathedral" style of incremental design driven by constructing views of system architecture. It has the following key features:

- It is component based, commonly being used to coordinate object oriented programming projects.

- (ii) It uses UML a diagrammatic notation for object oriented design for all for all blueprints.

- (iii) The design process is anchored, and driven by, use-cases which help keep sight of the anticipated behaviors of the system.

- (iv) It is architecture centric.

(v) Design is iterative and incremental - via a prescribed sequence of design phases within a cyclic process.

The Unified Process is a process product, developed and maintain by Rational Software. The Unified Process is a guide for how to effectively use the Unified Modelling Language (UML). UML is the tool that we use to represent (Model) the target software product. A major reason for using a graphical representation like UML is best expressed by the old proverb, a picture is worth a thouseand words. UML diagrams enable software professionals to communicate with one another more quickly and more accurately than if only verbal descriptions were used..

### 3.3 Iteration and Incrementation

In this project, I will use object-oriented modelling. The object-oriented paradigm is an iterative and incremental methodology. Within the Unified Process, each cycle contains four phases and each phase contains one or more iterations. Iterations is a complete development loop resulting in a release (internal or external) of an executable product, a subset of the final product under development which grows incrementally from iteration to iteration to become the final system. This is a system that released with additional or improved functionality.

The advantages of the Iterative and Incremental Approach compare with the traditional waterfall process are:

- (i) Risks re mitigated earlier.

- (ii) Change is more manageable.

- (iii) Higher level of reuse.

- (iv) The project team can learn along the way.

- (v) Better overall quality.

### 3.4 The Phases of the Unified Process

The software life cycle is broken into few cycles, each cycles working on a new generation of the product. Unified Process divides one development cycle in four consecutive phases. Those phases are:

- (i) Inception phase

- (ii) Elaboration phase

- (iii) Construction phase

- (iv) Transition phase

Each phase will end with the milestone as conclusion. A milestone means a point to make the critical decision about whether to continue development.

Figure 3.1: The core workflows and the phases of the Unified Process

### 3.4.1 The Inception Phase

Inception is the first phase for the life cycle, developers establish the business case for the system and delimit the poject scope during this phase. The aim of the inception phase is to determine whether it is worthwhile to develop the target software product. In other words, the primary aim of this phase is to determine whether the proposed software product is economically viable. The major milestone associated with the inception phase is called life-cycle objectives. The evaluation criteria for the inception phase are:

- Stakeholder agree on the scope of the system.

- Bussiness case for the system is strong enough to continue development.

- Sets of criticalhigh-level requirements are celarly addresses.

### 3.4.2 The Elaboration Phase

The aim of the elaboration phase is to refine the initial requirements, refine the architecture, monitor the risks and refine their priorities, refine the business case and poduce the software project management plan. The major activities of this phase are refinements or elaborations of the previous phase.

Basically the primary goal of the elaboration phase is to establish the ability to build the new system given the financial constraint, and other kinds of constraints that the development project faces. The elaboration phase also ensures the plan, requirement and architecture are stable enough and the risks are sufficiently mitigated.

The major milestone associated with this phase is called Life Cycle Architecture. At this point, developers examine the detailed system objectives and scope, the choice of architecture and the resolution of the major risks. The indications that the project has reached this milestone are:

- Most of the functional requirements for the systems have been captured with use case diagram.

- The project team has an initial project plan that describes how the construction phase will produce.

The architecture baseline is a small, shinny system that will serve as a solid foundation for ongoing development.

### 3.4.3 Construction Phase

The purpose of this phase is to build system that is capable of operating successfully in beta customer environment. This means all remaining components and application features are developed and integrated into the product and all features are throughly tested during construction phase. The milestone for the construction phase is initial peration capability. The project has reached this milestone if a set of beta customers has more or less fully operational system in their hands.

### 3.4.4 Transition Phase

The aim of the transition phase is to ensure that the client's requirements have indeed been meet. This phase is driven by feedback from the sites at which the beta version has been installes. Faults in the software product are corrected. Also, all the manuals are completed. During this phase, it is important to try to discover any previously unidentified risks. The main objectives of the transition phase are:

- Achieving user self-supportability

- Achieving stakeholder concurrence thet deployment baselines are complete and consistent with the evaluation criteria of the vision

- Achieving final product baseline as rapidly and cost effectively as practical

The milestone associated with this phase is called product release. At this point, developers should decide if the objectives were met, or should start another development cylce.

#### 3.5 Core Workflows

The Unified Process identifies core workflows that occur during the software development process. These workflows include Business Modeling, Requirements, Analysis, Design, Implementation and Test. The workflows are not sequential and likely will be worked on during all of the four phases. The workflows are described separately in the process for clarity but they do in fact run concurrently, interacting and using each other's artifacts.

### 3.5.1 Requirement Workflow

- · Capture the functional requirement with case model.

- Describe what the system should do and allows the developers and the customer to agree on that description.

#### 3.5.2 Analysis Workflow

- Aimed at building the analysis model to help the developer refine and structure the functional requirement captured.

- This workflow contains realizations of use cases that lend themselves better than the use cases to design and implementation work.

#### 3.5.3 Design Workflow

- Aimed at building the design model to describe the physical realizations of the use cases

- Also focus on the deployment model, which defines physical organization of the system in terms of computational nodes.

#### 3.5.4 Implementation Workflow

Aimed at building the implementation model, which describes how the elements of the design model are packaged into software component.

### 3.5.5 Test Workflow

Aimed at building the test model, which describes how integration and system tests will exercise executable components from the implementation model. Contains test case that are often derived directly from use cases.

#### 3.6 Requirement Elicitation

During the analyzing process, many data and information are requiring to do analysis. The data congregation is an essential part in order to have a throughout understanding of the system to develop. There are few techniques are use to get useful data and information at the beginning of the project.

To define the requirement, the following techniques are used:

- Internet surfing

- Interview

- Library research

#### 3.6.1 Internet Surfing

The internet is the largest information pool in the world. Whatever information requires also can get from the internet such as the information about circuit description and circuit simulation using object-oriented language and the advantages compared to other language.

#### 3.6.2 Interview

At the beginning, I try to contact by e-mail some of the researcher that doing their research and journal writing on this topic. Luckily I get some respond from them and here I make some discussion and Q & A session regarding on circuit description and circuit simulation using C++ and why they did research on that.

### 3.6.3 Library Research

Collecting some journal paper, reference books and articles that related to the project topic. Studies are done on various issues, problems and solutions that are detailed in the journal paper.

#### CHAPTER IV

### SYSTEM ANALYSIS

### 4.1 System Requirement Specification

System analysis is the one of the important phase, which focuses on understanding a system domain and the requirement. System analysis is conducted with the following objectives:

- Determine the functional and non-functional requirement for Circuit Description and Elementary Hierarchical Circuit Simulation Using C++.

- (ii) To determine the tools that will be used.

- (iii) To determine the programming language, software and hardware needs for Circuit Description and Elementary Hierarchical Circuit Simulation Using C++.

The system requirement need to drawn out to provide a guideline when developing a system. Therefore, the requirement analysis needs to cover the area of the functional requirement and non-functional requirement of <u>Circuit</u> Description and Elementary Hierarchical Circuit Simulation Using C++.

### 4.2 Functional Requirements

Functional requirement is a function or feature that must be included in an information system to satisfy business need and acceptable to the user. Functional requirement describe an interaction between system and the environment. In this project, the functional requirement is circuit component and the class that will be used in the circuit description.

### 4.2.1 Classification of Circuit Components

For the purpose of this report, objects which are at the digital level and above will only be considered. Therefore, switch level devices such as transistors will not be considered.

One possible way to classify these numerous objects is to consider all the circuit entities at their highest level of abstraction and attempt to group objects which have similar properties under the same base class. From this, three very general classes are formed:

- Component -- All elements derived from this class process input signals and generate output signals to the objects to which they are connected. It is possible for one component to be part of another component. Circuit elements which can be considered as kind of components would include AND gates, RS-latches and random functional blocks.

- Connector -- All elements derived from this class would be responsible for connecting components with other components or with the external world. Each connector is part of a component at some level of abstraction.

Since a connector can ``feed" one or more components via fan-out, a list of components can be considered part of a connector. Some circuit elements which are kind of connectors include wires, and I/O ports.

- Signals -- Objects instantiated from this class are passed from component to component via the connectors. A list of signals also can be considered as part of a wire. This report will consider signals as two entities: a signal value (such as HIGH, LOW or X) and an associated unit of time.

As alluded to above, linked list classes are required for components and signals. The need will also arise for a linked list class for I/O ports. Due to the current lack of parameterized types in the C++ language, some duplication of code is necessary to create the three linked list classes. Fortunately, the replication of code is relatively small.

#### The Component Class

Components are responsible for getting inputs, processing them and producing outputs. In order for components to get their inputs from and send their outputs to the external world, ports must be made part of the components in some way. To increase the ease at which the simulation algorithm can access the component's ports, pointers to both the input and output ports will be stored in separate linked lists within the components. Therefore, there are at least two elements of the Component class: two linked lists of input and output port pointers. Since ports form the interface of a component, these linked lists are placed in the public section of the class. However, the operations that can be performed on this linked list are limited by the public interface of the Port\_List class.

Next, the user should be given the option of assigning some name to a component, which will be useful from a debugging viewpoint. Therefore, a pointer to a character (string) will be placed in the class. In addition, in this particular implementation, every component maintains its own *local time* during the simulation. Since nothing else outside of the class should be allowed to access the name or local time, these two data members should be placed in the private section of the class so they can be accessed only by methods of this class, such as the constructor.

Every component also has a delay which represents how long it takes to produce its outputs upon receiving its inputs. During the simulation, objects derived from Component should be permitted to change the delay time of the component (for example, the delay time could increase during the simulation, modelling the effect of a component getting warmer, hence increasing its resistance). Since classes derived from Component are the only ones able to change the delay, the delay data member is protected in the class.

Two public methods are declared, which are used extensively during the simulation of the circuit. These two methods are process() and simulate().

Finally, a constructor is required which is used to actually build the component. Since a component is too abstract a concept to be useful from an instantiation perspective, only specialized classes derived from Component may call this constructor. Therefore the Component constructor is made a protected member of the class.

### The Component\_List Class

The Component\_List class, maintains a linked list of components which may be present in the fan-out of a connector.

#### The Connector Class

The Connector class is responsible for connecting components together and for connecting components with the outside world. In circuit description, there are two type of connectors, wires and ports. The Connector class will be used as an abstract base class from which a wire class and a Port class will be derived.

#### The Wire Class

The wire class is derived from the connector class. Wires connect components together and also maintain a history of signals which have travelled through them during the course of the simulation. Connections to components are achieved through the fan\_out data member as inherited from the Connector class. However, in order for the class to keep track of all the signals that have passed through it, it must maintain a linked list of signals. Hence a new class, Signal\_List is created for this purpose. The wire class defines two constructors. The first one accepts an optional name and simply passes that name up to its base class, connector, for initialization. The linked list of signals is then initialized and a single signal is added to the wire to represent its initial value.

#### The Port Class

Ports provide a means whereby components are connected with the external world. It is through ports that components send and receive signals. In addition to maintaining a fan-out of the components that it feeds (which is inherited from Connector), each port must also maintain a pointer to the connector that ``feeds" it. Note that a port can be fed by one, and only one, Connector. This means that a port may be fed by a single wire or by a single port; and not by, for example, two wires. Note, however, that a wire may feed one or more distinct ports. To keep track of the connector that feeds it, the Port class maintains a pointer to the specific Connector.

Since ports are somewhat too generalized, an Input and Output class will be derived from Port. To prevent the programmer from accidentally creating a Port object, the constructor will be kept protected and is therefore usable only by the Input and Output classes.

#### The Input and Output Class

The Input and Output classes are almost the same with just one minor difference.

#### The Port\_List Class

The Component class contains a Port\_List (a linked list of pointers to ports) in the public section of its class. The Port\_List class is almost identical to the Component\_List class. This similarity could be exploited using generic types or templates. Since C++ does not yet support templates, some code replication will be necessary.

### 4.3 Non-Functional Requirement

A non-functional requirement or constraint describes a restriction on the system that limits on choice for constructing a solution to the problem.

#### 4.3.1 Correctness

Correctness is the extent to which program satisfies its specification and fullfill user's requirement and objective.

#### 4.3.2 Reliability

The system will be developed in a way that is reliable and will not cause any unnecessary failure at the overall operation. System will not cause any technical or costly failure when it is used in reasonable manner. Any information display will be risk-free.

### 4.3.3 Response Time

The data retriever time should be considered with on a reasonable interval time. All the desired information should be available to user at any point in time. The user should not be asked to tolerate with slow response time.

#### 4.3.4 Expandability

Expandability measures the capability of a system to be upgraded or enhanced in future. It is important when an existing system needs enhancement to overcome changes in environment and requirement. Expandability of a system also determines whether the system can be integrated with sub-system to increase its functionality.

#### 4.4 Consideration of Programming Language

To implement circuit description and simulation using object-oriented language, I will use Microsoft Visual C++ 6.0. This is because this type of version are widely used in university and other educational institution.

Microsoft's *Visual* C++ 6.0 (VC++ 6.0) lets programmers unlock the power of Office and Internet Explorer and create custom Office and Windows apps. Every version of Microsoft Office and Internet Explorer has powerful custom features-dockable toolbars, tool tips, OLE automation, and ActiveX, for example. But to really put these features to work you need a full-fledged programming language. Features provided by VC++ 6.0 are:

- Fully integrated editor, compiler, and debugger

- Ability to create complex software systems

The list of updates in version 6.0 is lengthy, but two stand above the rest. This rendition of Microsoft's Visual C++ gets smart with IntelliSense technology, Microsoft lingo for auto-completion. What this means for you is after you type a period after a variable name, a handy drop-down menu appears offering the *soup du jour* in the way of the available members for the aforementioned object. Enter a method name and an open parenthesis and you are presented with prototypes, arguments and their types. Better yet, IntelliSense works with all the expected iterations and your code, saving quite a lot of time. Also, the intuitive edit and continue feature allows you to incorporate common, simple edits during your debugging without having to quit, rebuild and restart the debugger.

Other new features include the HTML Help Workshop, a tool for creating HTML-based context-sensitive help that can be integrated with the Web; a gallery of prepackaged C++ components and ActiveX controls; and a slew of inline optimization switches, programs and codes.

# 4.5 Hardware Requirement

| Specification             | Minimum Spec.                                                 |

|---------------------------|---------------------------------------------------------------|

| Required Operating System | Microsoft Windows 95/98, Microsoft<br>Windows NT 4.0 or later |

| Required Memory           | 24MB                                                          |

| Required Disk Space       | 290MB                                                         |

| Required Processor Class  | Intel Pentium                                                 |

| Required Processor Speed  | 90 MHz                                                        |

| Other Requirement         | Mouse or compatible device, CD-ROM                            |

#### CHAPTER V

### SYSTEM DESIGN

# 5.1 What is Systems Design

Information system design is define as those tasks that focus on a specification of a detailed computer based solution. It is also called physical design. System designs focuses on the technical or implementation concerns of the system.

Object-oriented design (OOD) is the newest design strategy. The aim of OOD is to design the product in terms of objects, that is instantiations of the classes and subclasses extracted during object-oriented analysis.

# 5.2 The Method of Designing

The technique used to describe hardware can be outlined in six major steps:

- Identify the internal circuit elements of the component. After the end of this step, one should have *I* input ports, *O* output ports, *S* subcomponents and *W* wires.

- 2. Create a class for the component. Make sure that this class is derived from Component so that it will inherit all the features of this base class. The parameters passed to the constructor of the class should include I + O references to connector objects, a parameter for the delay of the component and a parameter for the name of the component. The constructor should be in the public part of the class. The elements identified above should be encapsulated within the class. Keeping them in the private portion of the class prevents the relationships amongst the wires, subcomponents and ports from becoming corrupt by something from outside the class.

- 3. Connect primary inputs and outputs. When defining the constructor, calls are made to the *I* + *O* port constructors. This expresses the connectivity between the ports of the component and the connectors of the external environment. This will have the effect of connecting the I/O ports with the primary inputs and outputs of the circuit. Calling the I/O port constructors also has the effect of placing the ports in their respective linked lists. This is hidden from the user. It is often useful to disguise the call to the port constructors by using a CONNECT (Port, Wire, "Name").

- Call the W constructors for the wires. This will bring the wires into existence and place an initial value on each wire.

- 5. Construct each of the S subcomponents. One important point to remember when constructing the subcomponents is to pass only the wires and ports that are declared within the component class to the subcomponent constructors. If the external connectors passed to the encompassing component constructor are passed to the encapsulated subcomponents, then the designer may risk corrupting the description.

- 6. Create I + O external wires, and instantiate the component. This is usually done in the main() program of the C++ code. The external wires act as signal sources when hooked up to an input port. When connected to an output port, they act as signal destinations.

# 5.3 Hardware Description Component

In this project, I will concentrate on three type of hardware component. The hardware component are two input AND gate, Three Input AND Gate, RS-Latch and Full-Adder..

### 5.3.1 Two Input AND Gate

(a) Distinctive shape

(b) Rectangular outline with the AND(&) qualifying symbol

Figure 5.1: Standard logic symbols for the AND gate with two input

The Figure 5.1 shown standard logic symbols for the AND gate with two input. The lines connected to each symbol are the inputs and outputs. The inputs are on left of each symbol and the output is on the right. A circuit that performs a specific logic operation AND is called a logic gate. AND gates can have any number of inputs.

An AND gate produces a HIGH output only when all of the inputs are HIGH. When any of the input is LOW, the output is LOW. Therefore, the basic purpose of an AND gate is to determine when certain conditions are simultaneously true, as indicated by HIGH levels on all of its inputs and to produce a HIGH on its output to indicate that all these conditions are true. The gate operation can be stated as follows:

For a 2-input AND gate, output X is HIGH if inputs A and B are HGH; X is LOW if either A or B is LOW, or if both A and B are LOW. Since a two-input AND gate is at the lowest level of abstraction, the only encapsulated circuit elements will be two input ports and a single output port. When a two-input AND gate is actually instantiated and connected to primary input and output wires in the main C++ program, the data structure shown in Figure 5.2 is produced.

A two-input AND class may be declared as follows:

```

class And2 : public Component

public:

And2 (Connector &, Connector &, Connector &,

ckt time = 1L, char* = "And2");

process(ckt time);

void

private:

Input

I1, I2;

Output 01;

};

And2::And2(Connector &cil, Connector &ci2, Connector &col,

ckt time dly, char *name) :

Component(dly, name),

CONNECT(I1, ci1, "And2 I1"),

CONNECT(I2, ci2, "And2 I2"),

CONNECT(01, col, "And2 01")

{ }

```

The constructor is declared as taking three references to connector objects as parameters and the three ports are hidden in the private section of the class. The delay and the name of the component are first passed to the Component base class constructor for initialization. The ports of the class are then connected with its primary inputs and outputs.

Since the AND gate has no nested wires and no nested components, the description of the AND gate is finished. Its functionality is specified by redefining the virtual process() method.

## 5.3.2 Three-Input AND Gate

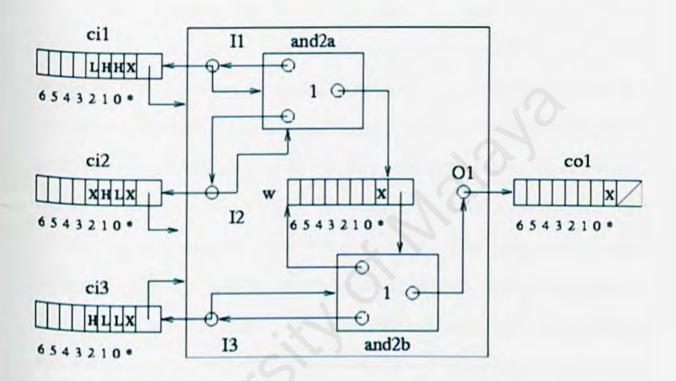

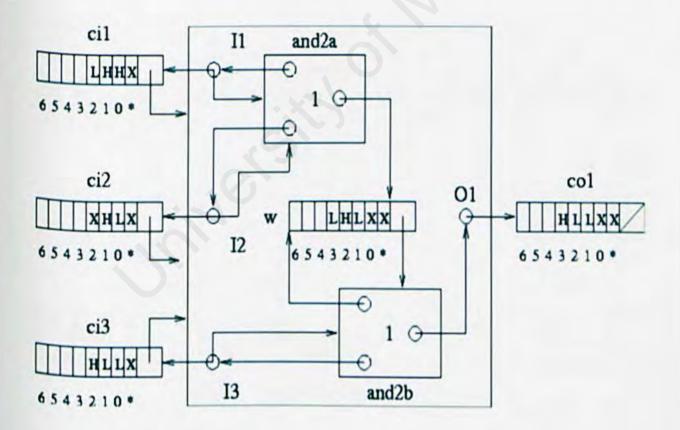

Next, a three-input AND gate will be built using two two-input AND gates, which were created previously, and a single wire that will connect the output of the first AND gate with the input of the second gate. Summarizing the fundamental components: there are three input ports, one output port, one wire and two-input AND gates.

```

The class declaration follows:

class And3 : public Component

1

public:

And3 (Connector &, Connector &,

Connector &, Connector &,

ckt_time = UNDEF_TIME, char* = "And3");

private:

I1, I2, I3;

Input

Output

01;

Wire

W1

and2a, and2b;

And2

};

```

| And3::And | (Connector &ci1, Connector &ci2, |

|-----------|----------------------------------|

|           | Connector &ci3, Connector &co1,  |

|           | ckt_time dly, char *name) :      |

| C         | omponent(dly, name),             |

| C         | NNECT(I1, ci1, "And3 I1"),       |

| C         | NNECT(12, ci2, "And3 12"),       |

| C         | NNECT(I3, ci3, "And3 I3"),       |

| C         | NNECT(01, col, "And3 01"),       |

| w         | "And3 wire"),                    |

| a         | d2a(I1, I2, w, 1L, "and2a"),     |

| { } a     | ud2b(w, I3, O1, 1L, "and2b")     |

The constructor now takes four connector objects since a three input AND gate has a total of four ports. As usual, the ports, wire and two-input AND gates are encapsulated in the private section of the class. The delay time of the three-input AND gate is defaulted to an undefined time because the delay of the gate actually depends upon the delay associated with the two two-input AND gates.

To define the constructor of the three-input AND gate, all the connector objects are connected with the ports accordingly; the wire is instantiated and the two two-input AND gates are constructed. The two inputs of the first two-input AND gate come from the first two input ports of the three-input AND gate, while its output is connected to the nested wire. The second two-input AND gate receives its first input from this wire and gets its second input from the third input port of the three-input AND gate. The output of this two-input AND gate is directed to the output port of the three-input AND gate.

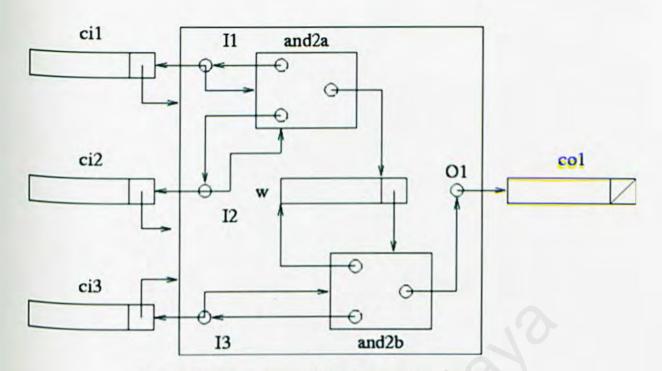

Figure 5.3 shows how all the elements of the circuit are connected when a threeinput AND gate is instantiated using external wires. For clarity, the linked list pointers which link the three input ports together have been omitted.

Figure 5.3: Three-Input AND Gate with External Wires

# 5.3.3 S-R (SET-RESET) Latch

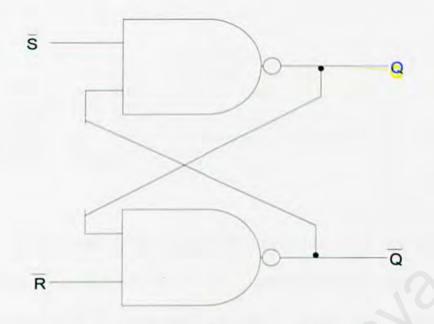

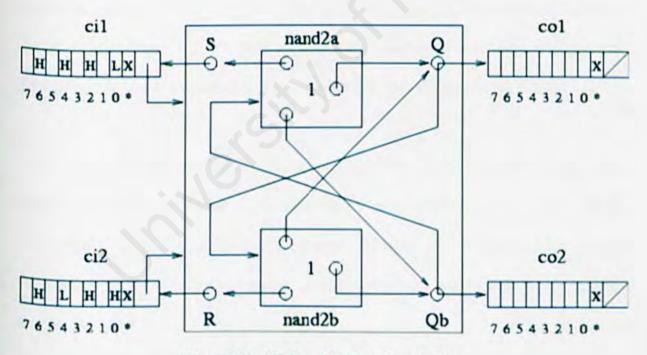

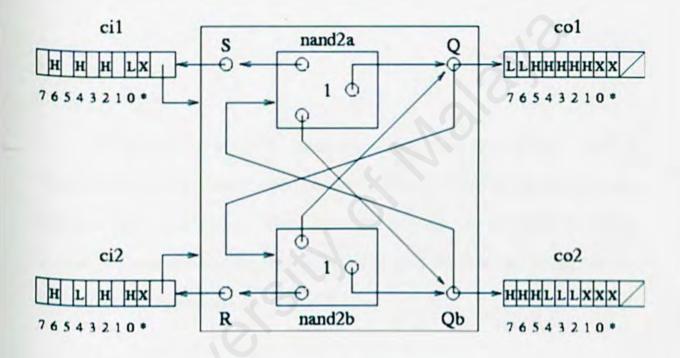

A latch is a type of bistable logic device or multivibrator. An active-LOW input S'-R' latch is formed with two cross-coupled NAND gates as shown in **Figure** 5.4. The output of each gates is connected to an input of the opposite gate. This produces the regenerative feedback that is characteristic of all latches and flip-flops.

Figure 5.4: Active-LOW input S'-R' latch

An RS-latch has two input ports, two output ports and two two-input NAND gates which can be described in a manner identical to the description of the two-input AND gate. Note that an RS-latch does *not* have two wires embedded within it. The feedback mechanism means that the two output ports, Q and Qb, also act as input ports to the two NAND gates. Therefore there are no wires created by the RS-latch.

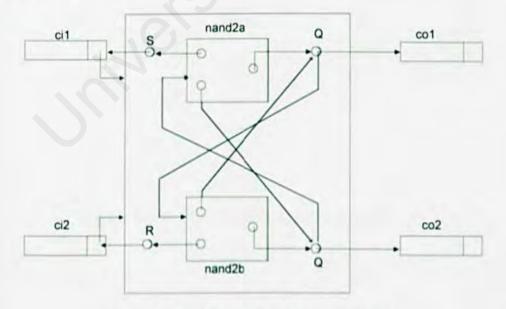

The four ports and the two NAND gates are encapsulated in the RS-latch class as shown in the following class declaration:

Next, the constructor of the class is defined. The four ports are connected with the four connectors passed into the constructor. The first NAND gate gets its first input from the s input port and its second input from the Qb output port. It sends its output to the Q output port. The second NAND gate gets its two inputs from the Q output port and the R input port of the RS-latch. Its output is sent to the Qb output port.

A diagram showing the interconnectivity of the components within the RS-latch is presented in **Figure 5.5**. The pointers connecting the input and output ports are omitted for clarity.

Figure 5.5: RS-Latch with External Wires

### 5.3.4 Full-Adder

Adders are important not only in computers but also in many types of digital systems in which numerical data are processed. An understanding of the basic adder operation is fundamental to the study of digital systems.

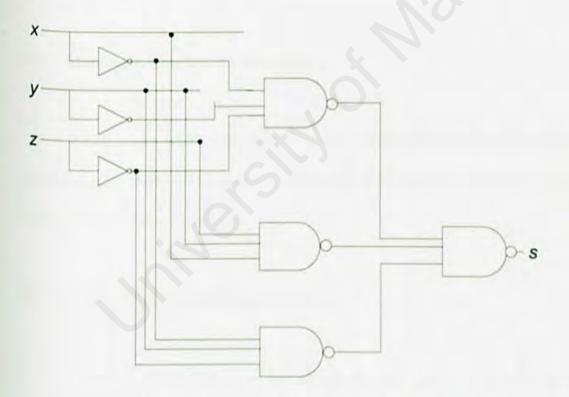

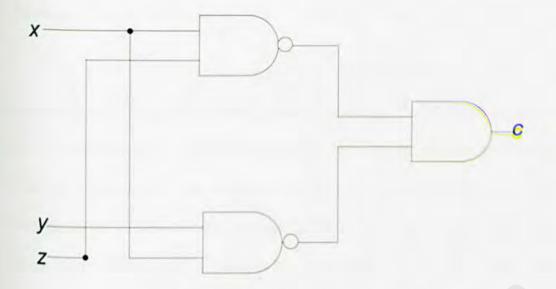

The full-adder accepts two input bits and an input carry and generates a sum output and an output carry. A logic diagram for *sum* of full-adder is shown in figure 5.6 (a) and *carry* in figure 5.6 (b).

Figure 5.6(a): Full-Adder Logic Diagram for Sum

Figure 5.6(b): Full-Adder Logic Diagram for Carry

### 5.4 Hardware Simulation Using C++

An algorithm which implements the new simulation technique will be examined and the signal class will be analyzed. This method of simulation has also been used in various forms in other simulators.

# 5.4.1 Circuit Simulation: Time and Queues

Central to the foundation of any simulator is the concept of time, and how the elements which make up a component move through it. Here we will look at methods of treating time and how that concept of time is manifested in the implementation.

### **Distributed Event Queues**

Here I will describe a new approach to hardware simulation which challenges the commonly used technique described above. Basically, the approach is to encapsulate one or more queues within the components themselves, thereby eliminating all the inherent problems of maintaining a global structure. The queues are distributed throughout the component and can exist at virtually any level of the description. Each queue keeps a history of the signals which have been sent to it during the course of the simulation and maintains a list of all the components which expect the signal. Therefore, the distributed queue serves as a connector between two components and also serves as the means by which signals may be propagated in parallel using a sequential programming language.

With respect to hardware, the distributed event queues represent wires; signals travel along wires and wires connect components together. Since the queues are encapsulated within the circuit components, an asynchronous signal would only affect those components which receive it and would not force the entire circuit back in time. Only those elements who use the asynchronous signal directly or indirectly will actually be moved backwards. The other components would continue to move forward in time where they left off.

## 5.4.2 Signals and Signal Transmission

Every signal is composed of two elements: a signal value (for example, HIGH, LOW, X) and a time when that value was produced. They are stored in linked lists in much the same way that the Component\_List class stores components.

The Signal class is declared as follows:

```

class Signal

friend ostream &operator << (ostream &, const Signal &);

public:

Signal(Sig_Val = X, ckt_time = INIT_TIME);

Sig Val();

operator

ckt time

get_time();

private:

Sig Val

value;

ckt time

t;

};

Signal::Signal(Sig_Val sv, ckt_time ct) :

value(sv), t(ct)

```

```

{ }

```

The operator Sig\_Val() function is a special function called a *user-defined conversion*. It returns the value field whenever a signal object is used in the context where a Sig\_Val is expected. This function essentially converts a signal into a signal value.

```

Signal::operator Sig_Val()

{

return value;

}

```

The get\_time() method is simply an access method which returns the time that the signal occurred.

```

ckt_time

Signal::get_time()

```

{

}

return t;

The ostream &operator << (ostream &, const Signal &) function enables the signal's value and time to be output using the << operator. This function is made a friend of the class so it has access to the hidden members of the class. Overloading this operator enables signals to be treated just like other built-in types which are output using the same technique.

The signal\_List class is declared as follows:

```

class Signal_List

{

public:

Signal_List();

void add(Signal);

Signal find(ckt_time);

void dump();

private:

Signal_Node *sig_list;

};

```

The constructor and the add() method are identical to the corresponding methods in the Component\_List class. The add() function also checks to make sure that signals enter the list in the correct time order. Should a signal be found whose time is less than or equal to the last signal on the wire, a warning message is displayed.