# SINGLE-PHASE CASCADED T AND $\pi$ -TYPE GRID-CONNECTED PV INVERTERS WITH CAPACITOR VOLTAGE BALANCING

**AAMIR AMIR**

# INSTITUTE FOR ADVANCED STUDIES UNIVERSITY OF MALAYA KUALA LUMPUR

# SINGLE-PHASE CASCADED T AND $\pi$ -TYPE GRID-CONNECTED PV INVERTERS WITH CAPACITOR VOLTAGE BALANCING

# **AAMIR AMIR**

# THESIS SUBMITTED IN FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

INSTITUTE FOR ADVANCED STUDIES UNIVERSITY OF MALAYA KUALA LUMPUR

# UNIVERSITY OF MALAYA ORIGINAL LITERARY WORK DECLARATION

Name of Candidate: **AAMIR AMIR**

| Matric No: HHD140009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name of Degree: Doctor of Philosophy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Title of Project Paper/Research Report/Dissertation/Thesis ("this Work"):                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Single-phase cascaded T and $\pi$ -type grid-connected PV inverters with capacito voltage balancing                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Field of Study: Electricity and Energy (Power Electronics)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I do solemnly and sincerely declare that:                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (1) I am the sole author/writer of this Work;                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>(2) This Work is original;</li> <li>(3) Any use of any work in which copyright exists was done by way of fair dealin and for permitted purposes and any excerpt or extract from, or reference to reproduction of any copyright work has been disclosed expressly an sufficiently and the title of the Work and its authorship have bee acknowledged in this Work;</li> </ul>                                                                                                                                   |

| <ul> <li>(4) I do not have any actual knowledge nor do I ought reasonably to know that the making of this work constitutes an infringement of any copyright work;</li> <li>(5) I hereby assign all and every rights in the copyright to this Work to the University of Malaya ("UM"), who henceforth shall be owner of the copyright in this Work and that any reproduction or use in any form or by any mean whatsoever is prohibited without the written consent of UM having been first had and obtained;</li> </ul> |

| (6) I am fully aware that if in the course of making this Work I have infringed an copyright whether intentionally or otherwise, I may be subject to legal actio or any other action as may be determined by UM.                                                                                                                                                                                                                                                                                                        |

| Candidate's Signature Date:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Subscribed and solemnly declared before,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Witness's Signature Date:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Name:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Designation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# SINGLE-PHASE CASCADED T AND $\pi$ -TYPE GRID-CONNECTED PV INVERTERS WITH CAPACITOR VOLTAGE BALANCING

#### **ABSTRACT**

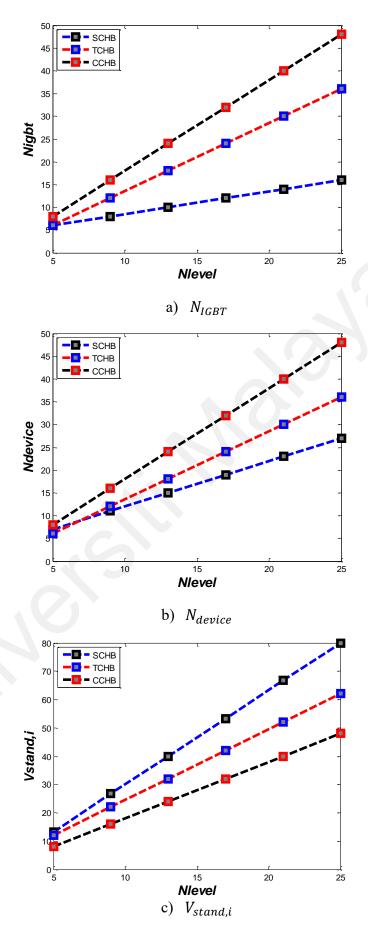

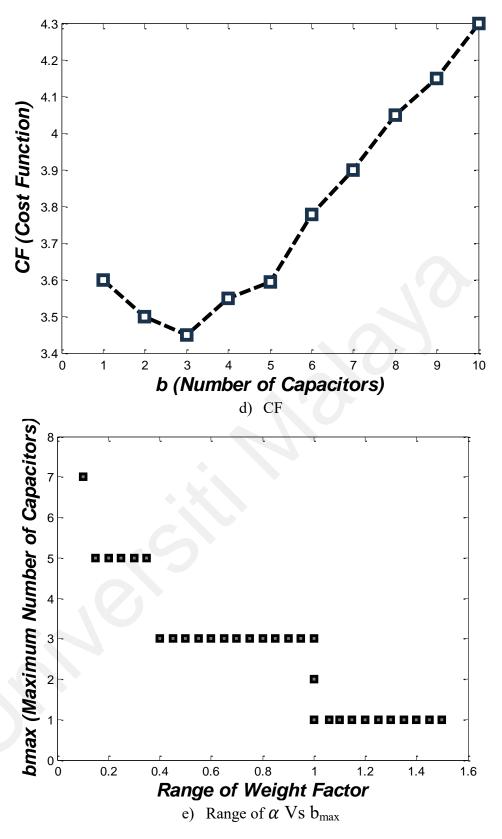

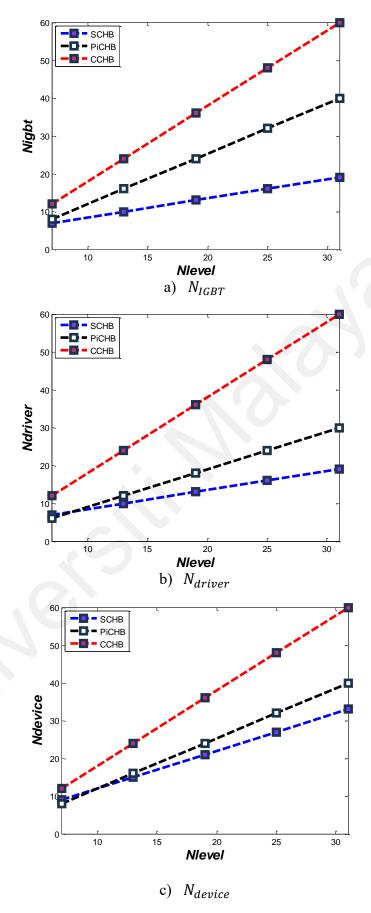

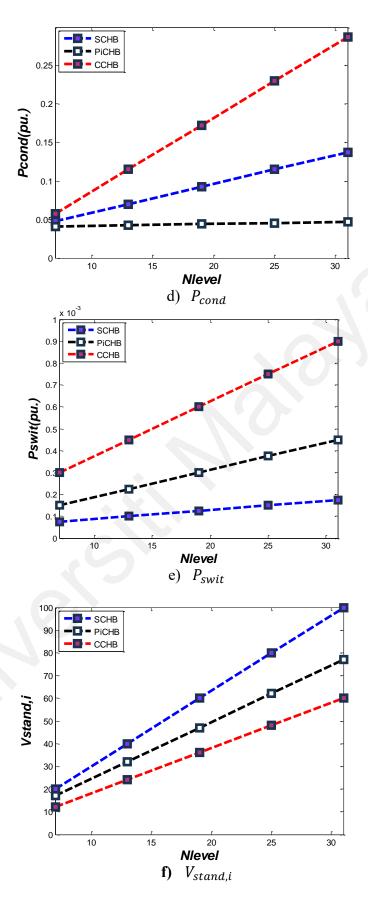

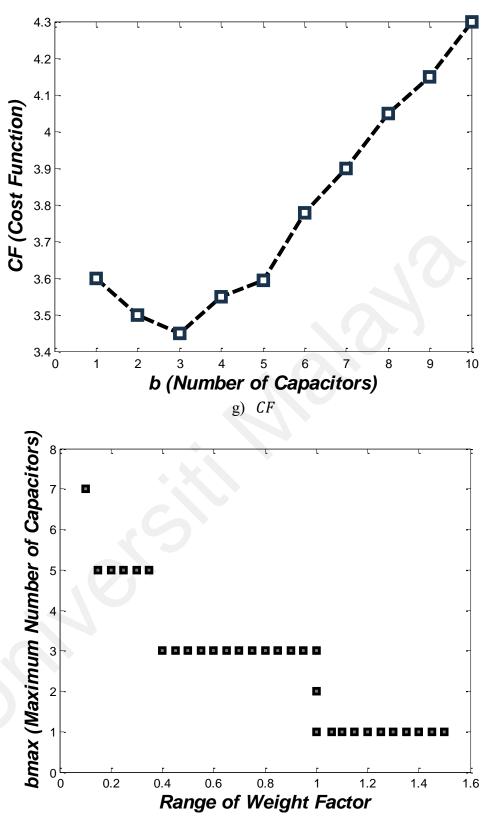

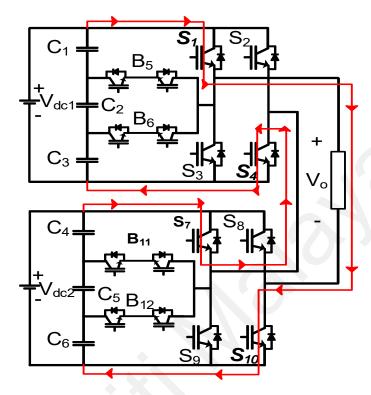

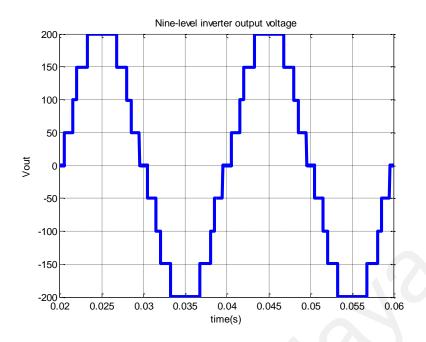

This thesis presents the development of single-phase T and  $\pi$ -type Cascaded H-Bridge inverters for a grid-connected photovoltaic (PV) system. The T-type Cascaded H-Bridge (TCHB) single-phase inverter utilizes two T-type Bidirectional Switches (BSs) and is capable of generating an output-voltage of nine levels (2Vdc, 3Vdc/2, Vdc, Vdc/2, 0, -Vdc/2, -Vdc, -3Vdc/2, -2Vdc) from two separate dc supply voltages. The  $\pi$ -type Cascaded H-Bridge (PiCHB) single-phase inverter employs two  $\pi$ -type BSs and can produce an output-voltage of thirteen levels (2Vdc, 5Vdc/3, 4Vdc/3, Vdc, 2Vdc/3, Vdc/3, 0, -Vdc/3, -2Vdc/3, -Vdc, -4Vdc/3, -5Vdc/3, -2Vdc) from two separate dc supply voltages. In addition, to validate the improved performance of the suggested structures, the TCHB and PiCHB topologies are compared against various other symmetric cascaded topologies, considering the parameters of number of switches  $N_{igbt}$  employed, number of gate drivers  $N_{driver}$  used, standing voltages  $V_{stand}$  on the semiconductor switches and cost function CF.

To realize a low frequency switching, the switching angles were optimized by the Optimized Harmonic Elimination Stepped Waveform (OHESW) technique, whose resulting transcendental equations were solved by an open bracketed numerical method technique. Among the multiple solution sets obtained, the solution offering least output-voltage THD was selected.

High frequency switching with one triangular carrier signal and identical modulation signals at eight and twelve different offsets generated the PWM signals for the stated TCHB and PiCHB inverters, respectively. The PWM switching pulses were attained by the intersection of a high-frequency triangular carrier against low-frequency sinusoidal

signals. These low-frequency signals were considered as the modulating (or reference) signals.

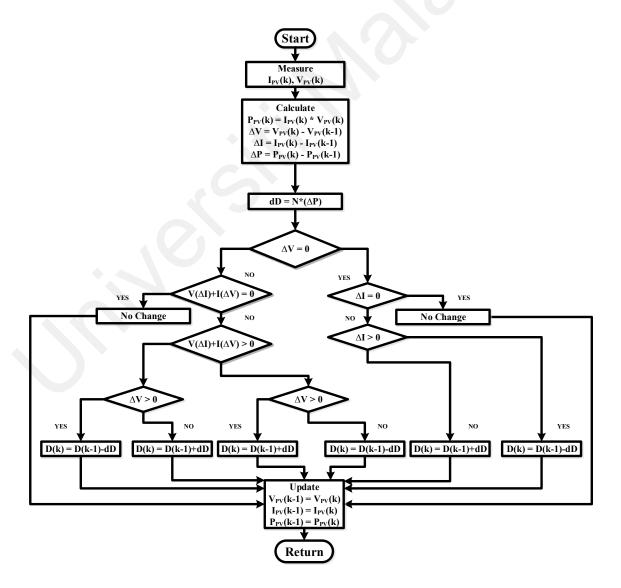

Maximum power point tracking (MPPT) technique based on modified incremental conductance (mINC) method, anti-islanding protection and a digital proportional—integral (PI) current-control algorithm had been employed for the grid-connected PV system application. A TMS320F28335 DSP and an ALTERA cyclone II FPGA board had been used to implement the proposed closed-loop control system.

To validate the performance of the Grid-tied PV system, simulation results were attained by utilizing Matlab/Simulink software, and the experiments, were performed on a hardware prototype.

**Keywords:** Maximum power point tracking (MPPT); modified incremental conductance (mINC) MPPT; T-type nine-level inverter;  $\pi$ -type thirteen-level inverter; pulse width-modulated (PWM).

# PENYONGSANG PHOTOVALTAIK FASA TUNGGAL TERSAMBUNG GRID JENIS T DAN $\pi$ DENGAN PENGIMBANGAN VOLTAN KAPASITOR

### **ABSTRAK**

Tesis ini membentangkan pembangunan inverters H-Bridge Cascaded T dan π fasa tunggal untuk sistem photovoltaic (PV) yang terikat grid. Inverter fasa tunggal T-Cascaded H-Bridge (TCHB) menggunakan dua suis Bidirectional Tipe (BS) dan mampu menghasilkan voltan keluaran sembilan tahap (2Vdc, 3Vdc / 2, Vdc, Vdc / 2, 0, -Vdc / 2, -Vdc, -3Vdc / 2, -2Vdc) daripada dua voltan pembekalan dc yang berasingan. Sedangkan inverter satu fasa Cascaded H-Bridge (PiCHB) π-jenis Cascaded H-Bridge (PiCHB) menggunakan dua jenis π-jenis dan dapat menghasilkan voltan keluaran tiga belas (2Vdc, 5Vdc / 3, 4Vdc / 3, Vdc, 2Vdc / Vdc / 3, 0, -Vdc / 3, -2Vdc / 3, -Vdc, -4Vdc / 3, -5Vdc / 3, -2Vdc) daripada dua voltan pembekalan dc yang berasingan. Di samping itu, untuk mengesahkan peningkatan prestasi struktur yang dicadangkan, topologi TCHB dan PiCHB dibandingkan dengan pelbagai topologi casetik yang lain, memandangkan parameter bilangan suis *Nigbt* digunakan, bilangan pemandu pintu *Ndriver* digunakan, voltan tetap *Vstand* pada semikonduktor suis dan fungsi kos *CF*.

Untuk mencapai peralihan kekerapan yang rendah, sudut pensuisan dioptimumkan oleh teknik Pengekalan Harmonik Kaedah Penghapusan Harmonik yang Dioptimumkan (OHESW), yang menghasilkan persamaan transenden yang telah diselesaikan oleh teknik kaedah berangka terbuka. Di antara pelbagai penyelesaian penyelesaian yang diperolehi, larutan yang menawarkan THD voltan keluaran minimum dipilih.

Pengalihan kekerapan tinggi dengan satu isyarat pembawa segitiga dan isyarat modulasi yang serupa pada lapan dan dua belas offset yang berbeza menghasilkan isyarat PWM untuk inverters TCHB dan PiCHB yang dinyatakan. PWM beralih denyutan dicapai oleh persimpangan pengangkut segi tiga frekuensi tinggi terhadap isyarat

sinusoidal frekuensi rendah. Isyarat frekuensi rendah ini dianggap sebagai isyarat modulasi (atau rujukan).

Teknik pengesanan titik kuasa maksimum (MPPT) berdasarkan kaedah konduktansifkan tambahan (mINC) yang telah diubahsuai, perlindungan anti-pulau dan algoritma kawalan semasa berkadar digital (PI) telah digunakan untuk aplikasi sistem PV yang berkaitan grid. Sebuah DSP TMS320F28335 dan sebuah papan FPGA siklon II ALTERA telah digunakan untuk melaksanakan sistem kawalan gelung tertutup yang dicadangkan.

Untuk mengesahkan prestasi sistem PV bertalian Grid, hasil simulasi dicapai dengan menggunakan perisian Matlab / Simulink, dan eksperimen, dilakukan pada prototaip perkakasan.

**Kata kunci:** pengesanan titik kuasa maksima (MPPT); ubah bentuk konduktansan tambahan (mINC) MPPT; penyongsang sembilan peringkat T; jenis penyongsang 13; denyutan lebar denyutan (PWM).

#### **ACKNOWLEDGEMENTS**

My special gratitude to Prof. Ir. Dr. Nasrudin Abd Rahim and Assoc. Prof. Dr. Jeyraj Selvaraj who supervised and provided me with the proper way of accomplishing this research. Their advice and expertise, right from the fundamentals, helped me develop my understanding of good research in the field of power electronics.

I am grateful to the faculty at the UM Power Energy Dedicated Advanced Centre (UMPEDAC) both teaching staff and administrators. I am particularly indebted to Dr. Che Hang Seng and Mr. Asim Amir whom I owe a great deal of thanks for the valuable knowledge they passed on to me and support they provided.

Above all, no words are eloquent enough to demonstrate my gratitude to my parents, my brothers, my sisters and my whole family. I must acknowledge my father who dedicated all his life supplicating prayers to me, and most special thanks to my mother, the greatest person in my life for her love and giving me prayers without any limits. This research thesis is dedicated to my niece and all my family.

# TABLE OF CONTENTS

| Abst | ract     | •••••      |                                           | iii   |

|------|----------|------------|-------------------------------------------|-------|

| Abst | rak      | •••••      |                                           | v     |

| Ackı | nowledg  | ements     |                                           | vii   |

| Tabl | e of Cor | ntents     |                                           | viii  |

| List | of Figur | es         |                                           | xiii  |

| List | of Table | es         |                                           | xxiii |

| List | of Symb  | ols and A  | bbreviations                              | xxiv  |

| List | of Appe  | ndices     |                                           | xxix  |

|      |          |            |                                           |       |

| CHA  | APTER    | 1: INTRO   | ODUCTION                                  | 1     |

| 1.1  | Backgr   | round      |                                           | 1     |

| 1.2  |          |            | ons                                       |       |

| 1.3  | Resear   | ch Object  | ives                                      | 5     |

| 1.4  | Overvi   | ew of the  | Chapters                                  | 5     |

|      |          |            |                                           |       |

| CHA  | APTER    | 2: OVER    | VIEW OF SOLAR ENERGY SYSTEM               | 7     |

| 2.1  | Introdu  | iction     |                                           | 7     |

| 2.2  | PV Par   | nel Charac | eteristics                                | 7     |

| 2.3  | Maxim    | num Powe   | r Point Tracking (MPPT)                   | 11    |

|      | 2.3.1    | Digital T  | Techniques                                | 13    |

|      |          | 2.3.1.1    | Newton-Raphson method (NRM)               | 13    |

|      |          | 2.3.1.2    | The secant method (SM)                    | 14    |

|      |          | 2.3.1.3    | Bisection search method (BSM)             | 15    |

|      |          | 2.3.1.4    | The central point iterative method (CPIM) | 16    |

|      |          | 2.3.1.5    | False position method (FPM)               | 17    |

|     |                           | 2.3.1.6 Firefly algorithm (FA)                                                                                     | 18                                     |

|-----|---------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|     |                           | 2.3.1.7 Predictor method (PM)                                                                                      | 19                                     |

|     |                           | 2.3.1.8 Ant colony optimization (ACO)                                                                              | 20                                     |

|     |                           | 2.3.1.9 Neural network (NN)                                                                                        | 21                                     |

|     |                           | 2.3.1.10 Fuzzy logic (FL)                                                                                          | 21                                     |

|     |                           | 2.3.1.11 Hill-climbing (HC) techniques                                                                             | 22                                     |

|     | 2.3.2                     | Analog Techniques                                                                                                  | 24                                     |

|     |                           | 2.3.2.1 Ripple correlation control (RCC)                                                                           | 24                                     |

|     |                           | 2.3.2.2 System oscillation technique (SOT)                                                                         | 25                                     |

|     | 2.3.3                     | Hybrid Techniques                                                                                                  | 25                                     |

|     |                           | 2.3.3.1 Droop control MPPT (DCL) DC-link capacitor                                                                 | 25                                     |

|     |                           | 2.3.3.2 Fractional <b>Voc</b> and <b>Isc</b> (FVI)                                                                 | 26                                     |

| 2.4 | Power (                   | Converter Topologies                                                                                               |                                        |

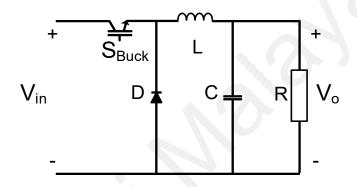

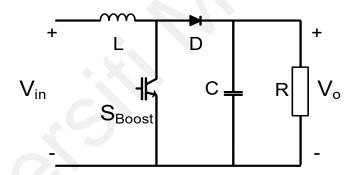

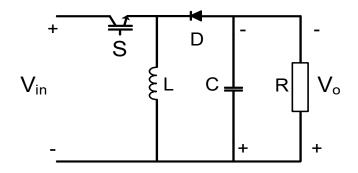

|     | 2.4.1                     | DC-DC Converters                                                                                                   | 27                                     |

|     |                           |                                                                                                                    |                                        |

|     | 2.4.2                     | DMPPT Implementation on Various DC-DC Converter Topologies                                                         |                                        |

|     | 2.4.2                     |                                                                                                                    | 32                                     |

|     | 2.4.2                     | DMPPT Implementation on Various DC-DC Converter Topologies                                                         | 32                                     |

|     | 2.4.2                     | DMPPT Implementation on Various DC-DC Converter Topologies  2.4.2.1 Change in voltage for duty cycle closer to MPP | 32                                     |

| 2.5 | 2.4.3                     | DMPPT Implementation on Various DC-DC Converter Topologies  2.4.2.1 Change in voltage for duty cycle closer to MPP | 32<br>32<br>34                         |

| 2.5 | 2.4.3                     | DMPPT Implementation on Various DC-DC Converter Topologies  2.4.2.1 Change in voltage for duty cycle closer to MPP | 32<br>34<br>35                         |

| 2.5 | 2.4.3<br>Multile          | DMPPT Implementation on Various DC-DC Converter Topologies  2.4.2.1 Change in voltage for duty cycle closer to MPP | 32<br>34<br>35<br>37                   |

| 2.5 | 2.4.3<br>Multile          | DMPPT Implementation on Various DC-DC Converter Topologies  2.4.2.1 Change in voltage for duty cycle closer to MPP | 32<br>34<br>35<br>37<br>38             |

| 2.5 | 2.4.3<br>Multile          | DMPPT Implementation on Various DC-DC Converter Topologies  2.4.2.1 Change in voltage for duty cycle closer to MPP | 32<br>34<br>35<br>37<br>38<br>38       |

| 2.5 | 2.4.3<br>Multile<br>2.5.1 | DMPPT Implementation on Various DC-DC Converter Topologies  2.4.2.1 Change in voltage for duty cycle closer to MPP | 32<br>34<br>35<br>37<br>38<br>38<br>40 |

| 2.5 | 2.4.3<br>Multile<br>2.5.1 | DMPPT Implementation on Various DC-DC Converter Topologies  2.4.2.1 Change in voltage for duty cycle closer to MPP | 32<br>34<br>35<br>37<br>38<br>40<br>41 |

|     | 2.5.3   | Reduced Switch (RS) MLI                          | 44    |

|-----|---------|--------------------------------------------------|-------|

|     |         | 2.5.3.1 No H-bridge MLI symmetric topologies     | 44    |

|     |         | 2.5.3.2 H-bridge MLI symmetric topologies        | 45    |

|     |         | 2.5.3.3 No H-Bridge MLI Asymmetric topologies    | 46    |

|     |         | 2.5.3.4 H-bridge MLI asymmetric topologies       | 47    |

|     |         | 2.5.3.5 Review of hybrid MLI                     | 48    |

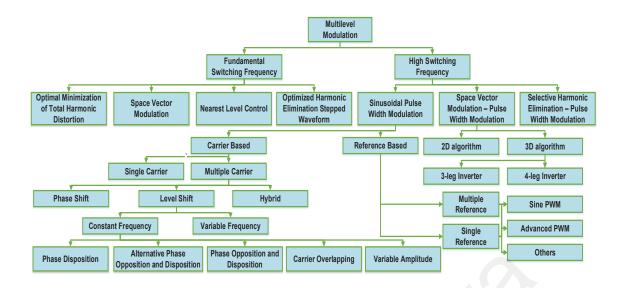

|     | 2.5.4   | Modulation Scheme                                | 50    |

|     | 2.5.5   | Current Control Schemes                          | 53    |

|     |         | 2.5.5.1 Hysteresis current control               | 54    |

|     |         | 2.5.5.2 Linear current control                   | 55    |

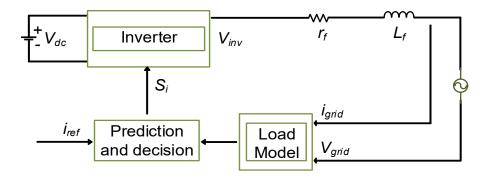

|     |         | 2.5.5.3 Predictive current control               | 56    |

| 2.6 | PV Sys  | stem Protection                                  | 57    |

|     | 2.6.1   | Anti-Islanding Standard                          | 58    |

|     | 2.6.2   | Anti-Islanding Technique                         | 58    |

| 2.7 | Summa   | ary                                              | 59    |

|     |         |                                                  |       |

| CHA | APTER   | 3: PROPOSED SINGLE-PHASE T AND $\pi$ -TYPE       | GRID- |

| COI | NNECT   | ED PV INVERTERS                                  | 61    |

| 3.1 | Introdu | ection                                           | 61    |

| 3.2 | Structu | re and Principle Operation of Proposed Inverters | 62    |

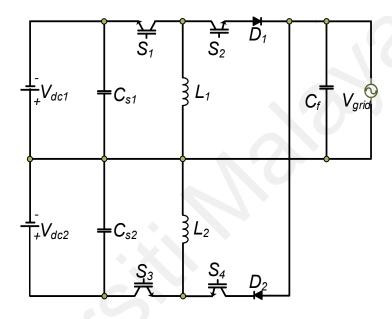

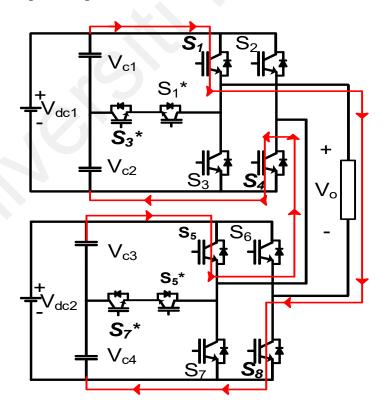

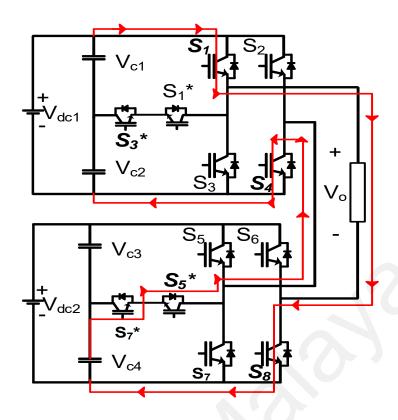

|     | 3.2.1   | TCHB Inverter                                    | 62    |

|     |         | 3.2.1.1 Proposed Circuit Configuration           | 62    |

|     |         | 3.2.1.2 Comparative Analysis                     | 63    |

|     |         | 3.2.1.3 Principles of operation                  | 67    |

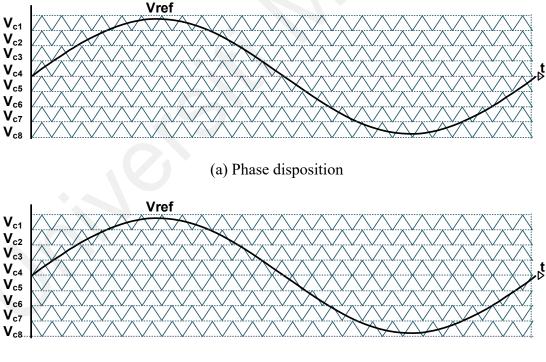

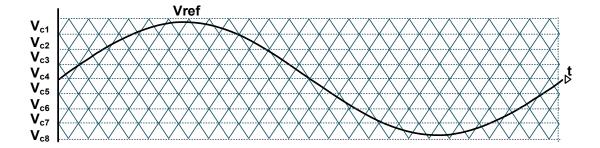

|     |         | 3.2.1.4 PWM method involved                      | 74    |

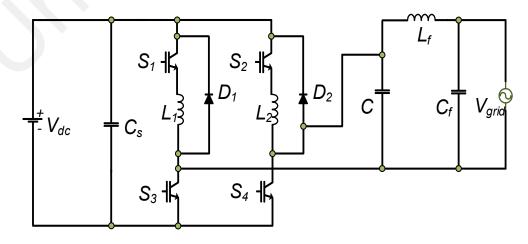

|     | 3.2.2   | PiCHB Inverter                                   | 79    |

|     |         | 3.2.2.1 Proposed Circuit Configuration           | 79    |

|     |         | 3.2.2.2 Comparative Analysis                                | 80 |

|-----|---------|-------------------------------------------------------------|----|

|     |         | 3.2.2.3 Principles of operation                             | 88 |

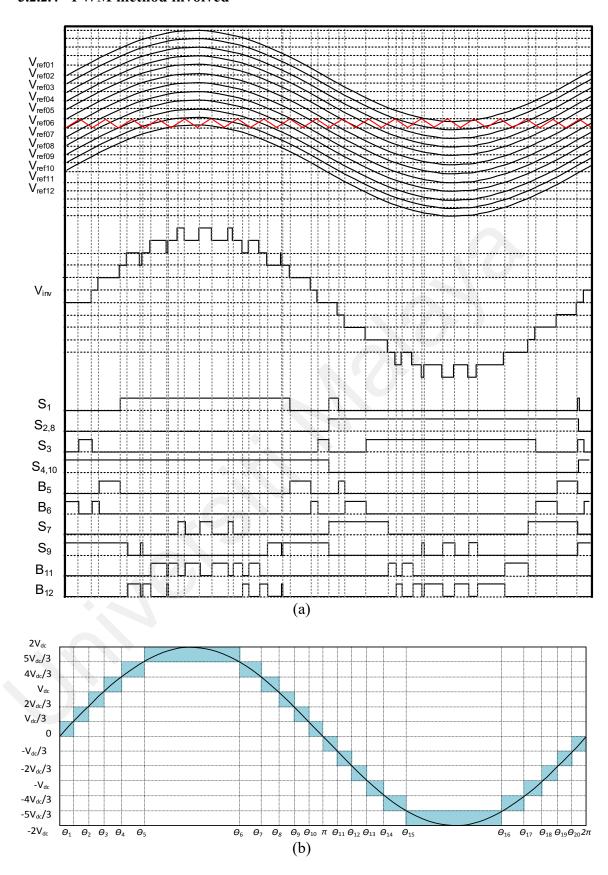

|     |         | 3.2.2.4 PWM method involved                                 | 99 |

| 3.3 | Propos  | ed Modified Incremental (mINC) Technique1                   | 03 |

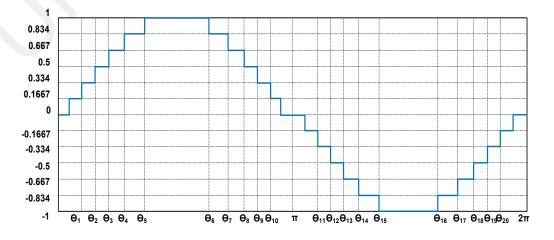

| 3.4 | OHES    | W for Low-Frequency1                                        | 05 |

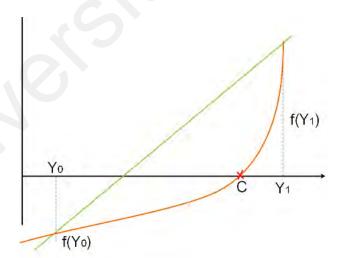

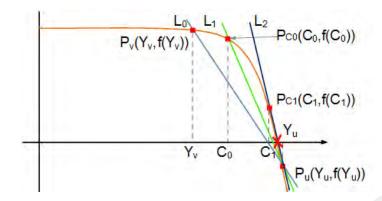

|     | 3.4.1   | Open-Bracket Technique for Optimization of Switching Angles | 06 |

| 3.5 | Contro  | 1 System of the Proposed Inverter in Grid-Tied PV System    | 08 |

| 3.6 | Summa   | ary1                                                        | 12 |

|     |         |                                                             |    |

| CHA |         | 4: SIMULATION RESULTS1                                      |    |

| 4.1 |         | ection                                                      |    |

| 4.2 | Simula  | tions at Low-Frequency Switching1                           | 13 |

|     | 4.2.1   | TCHB Inverter1                                              | 13 |

|     | 4.2.2   | PiCHB Inverter                                              | 17 |

| 4.3 | Simula  | tion of the PWM Control Scheme                              | 21 |

|     | 4.3.1   | TCHB Inverter                                               | 21 |

|     | 4.3.2   | PiCHB Inverter                                              | 33 |

| 4.4 | Simula  | tion for mINC MPPT on Various DC-DC Converters1             | 45 |

| 4.5 | Simula  | tion for Grid-Tied PV Application                           | 48 |

|     | 4.5.1   | TCHB inverter                                               | 49 |

|     | 4.5.2   | PiCHB inverter                                              | 55 |

|     |         | 4.5.2.1 RLC passive balancing                               | 56 |

| 4.6 | Summa   | ary1                                                        | 69 |

|     |         |                                                             |    |

| CHA | APTER   | 5: EXPERIMENTAL RESULTS1                                    | 71 |

| 5.1 | Introdu | iction1                                                     | 71 |

| 5.2 | Implen  | nenting for PWM Switching Frequency                         | 71 |

|      | 5.2.1    | Hardware Configuration                            | 171 |

|------|----------|---------------------------------------------------|-----|

|      | 5.2.2    | TCHB Inverter                                     | 172 |

|      | 5.2.3    | PiCHB Inverter                                    | 175 |

| 5.3  | Imple    | menting the mINC MPPT on various DC-DC Converters | 185 |

| 5.4  | Imple    | menting the Grid-Tied PV Application              | 187 |

|      | 5.4.1    | Hardware Configuration                            | 187 |

|      | 5.4.2    | TCHB Inverter                                     | 189 |

|      | 5.4.3    | PiCHB Inverter                                    | 191 |

| 5.5  | Summ     | ary                                               | 196 |

|      |          |                                                   |     |

| CHA  | APTER    | 6: CONCLUSIONS AND FUTURE WORK                    | 197 |

| 6.1  | Conclu   | uding Remarks                                     | 197 |

| 6.2  | Autho    | r's Contribution                                  | 198 |

| 6.3  | Future   | Works                                             | 200 |

| Refe | erences  |                                                   | 201 |

| List | of Publi | cations                                           | 215 |

| Ann  | endix A  |                                                   | 217 |

# LIST OF FIGURES

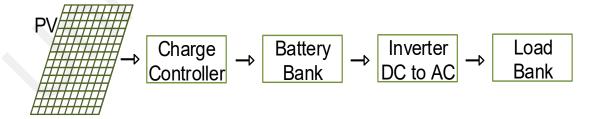

| Figure 1.1: Block diagram for stand-alone PV system with battery pack                | 1  |

|--------------------------------------------------------------------------------------|----|

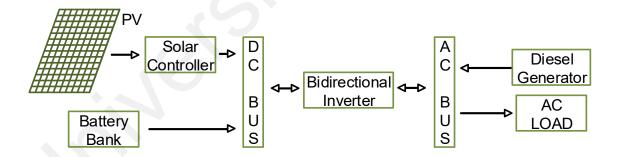

| Figure 1.2: Block diagram for hybrid PV system                                       | 2  |

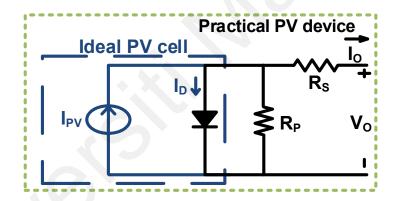

| Figure 2.1: Electrical model of PV cell.                                             | 8  |

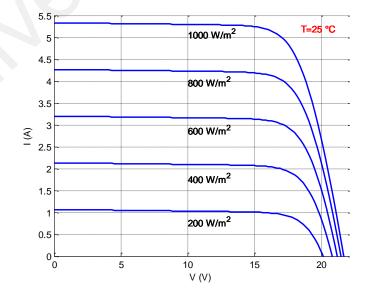

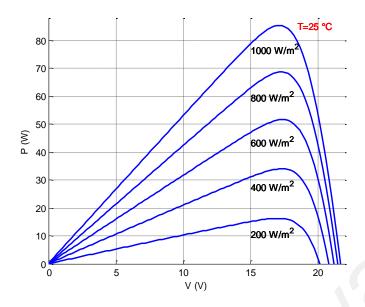

| Figure 2.2: I-V curve of during variations in irradiance                             | 10 |

| Figure 2.3: P-V curve during variations in irradiance                                | 11 |

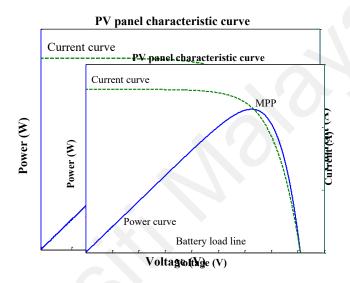

| Figure 2.4: Intersection between battery load line and I-V curve of a PV panel       | 12 |

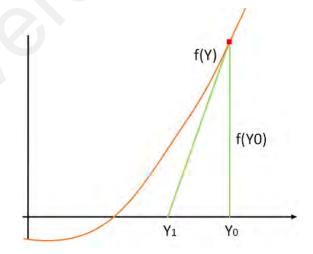

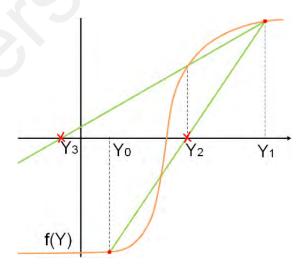

| Figure 2.5: Basic Principle of NRM                                                   | 13 |

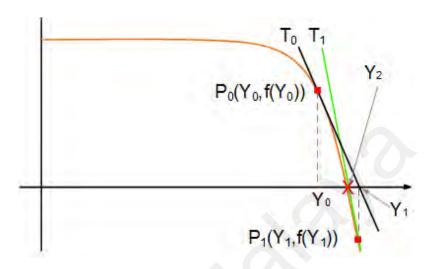

| Figure 2.6: MPPT by NRM                                                              | 14 |

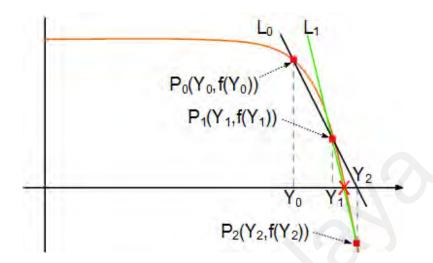

| Figure 2.7: Basic Principle of SM                                                    | 14 |

| Figure 2.8: MPPT by SM                                                               | 15 |

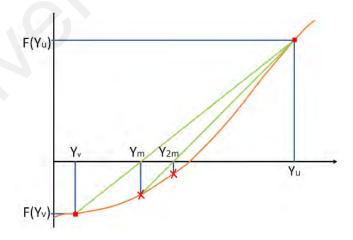

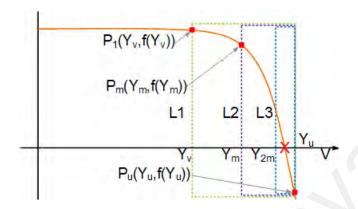

| Figure 2.9: Basic Principle of BSM                                                   | 15 |

| Figure 2.10: MPP tracking by BSM                                                     | 16 |

| Figure 2.11: MPP tracking by CPI                                                     | 16 |

| Figure 2.12: CPI Flowchart                                                           | 17 |

| Figure 2.13: Basic Principle of FPM                                                  | 17 |

| Figure 2.14: MPP tracking with FPM                                                   | 18 |

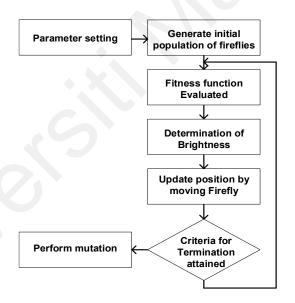

| Figure 2.15: Flowchart of FA                                                         | 18 |

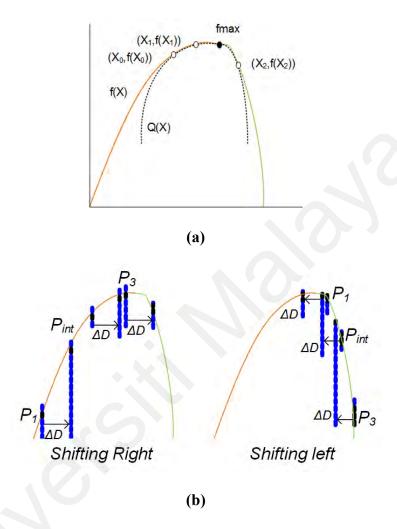

| Figure 2.16: (a) MPP tracking by PM (b) MPP tracking by right and left shift emby PM |    |

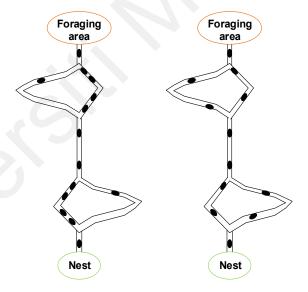

| Figure 2.17: (a) Ant following the shortest path (b) Following a random path         | 20 |

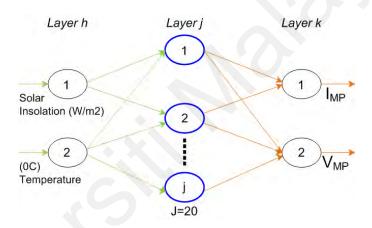

| Figure 2.18: MPP tracking employing the NN technique                                 | 21 |

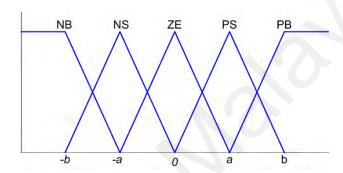

| Figure 2.19: FL membership function                                                  | 22 |

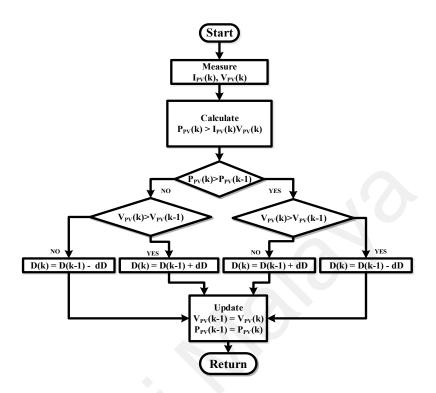

| Figure 2.20: Direct control P&O method flowchart                                     | 23 |

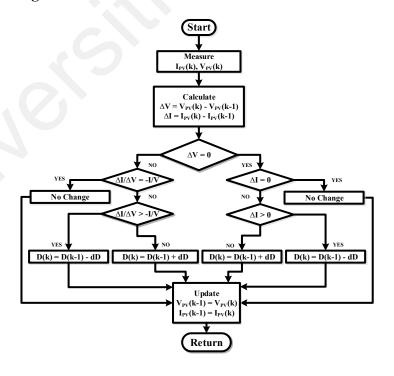

| Figure 2.21: Direct control INC method flowchart                                     | 23 |

| Figure 2.22: MPPT by DCL                                             | 26 |

|----------------------------------------------------------------------|----|

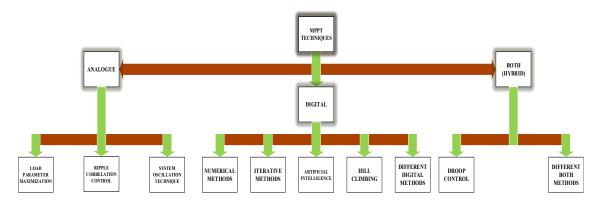

| Figure 2.23: MPPT Classification                                     | 27 |

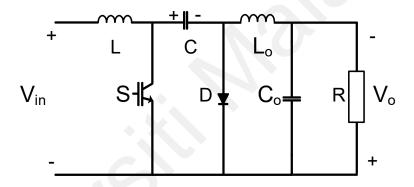

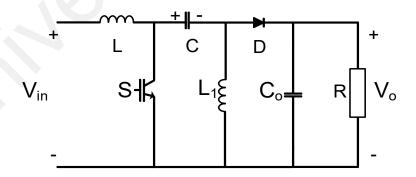

| Figure 2.24: Schematic diagram of the Buck Converter                 | 29 |

| Figure 2.25: Schematic diagram of the boost converter                | 30 |

| Figure 2.26: Schematic diagram of the Buck-Boost Converter           | 31 |

| Figure 2.27: Schematic diagram of the Cuk Converter                  | 31 |

| Figure 2.28: Schematic diagram of the SEPIC Converter                | 31 |

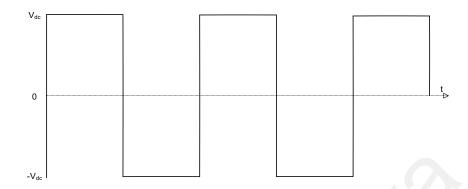

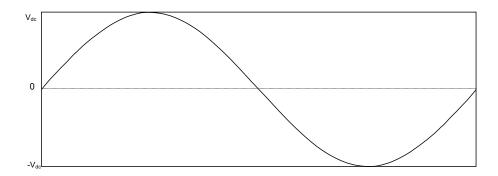

| Figure 2.29: Square-wave output voltage                              | 36 |

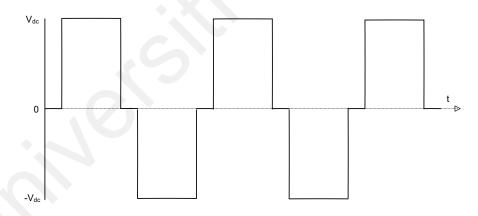

| Figure 2.30: Modified-sine wave output voltage                       | 36 |

| Figure 2.31: Sine-wave output voltage                                | 37 |

| Figure 2.32: Buck-boost inverter                                     | 39 |

| Figure 2.33: Four-switch resonant buck-boost inverter                | 39 |

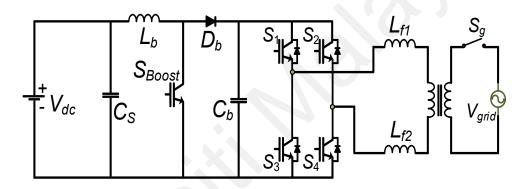

| Figure 2.34: Two-stage boost inverter                                | 40 |

| Figure 2.35: Multiple-stage inverter with DC-link between two-stages | 41 |

| Figure 2.36: Multiple-stage boost inverter with pseudo-DC-link       | 41 |

| Figure 2.37: Multiple-stage boost inverter                           | 41 |

| Figure 2.38: Three-level NPC MLI                                     | 43 |

| Figure 2.39: Three-level FC MLI                                      | 43 |

| Figure 2.40: Three-level H-Bridge MLI                                | 44 |

| Figure 2.41: RS bidirectional MLI                                    | 45 |

| Figure 2.42: Packed U-Cell RS MLI                                    | 45 |

| Figure 2.43: Cascaded half-bridge RS MLI                             | 46 |

| Figure 2.44: RS asymmetric MLI with binary sequence                  | 46 |

| Figure 2.45: RS asymmetric MLI with trinary sequence                 | 47 |

| Figure 2.46: RS MLI asymmetric topology involving H-Bridge                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.47: Hybrid MLI with NPC and CHB                                                                                                                           |

| Figure 2.48: Hybrid MLI with NPC and half bridge inverter cells                                                                                                    |

| Figure 2.49: Hybrid MLI by two NPC and CHB                                                                                                                         |

| Figure 2.50: Hybrid MLI by FC and CHB                                                                                                                              |

| Figure 2.51: Hybrid MLI by two FC and CHB                                                                                                                          |

| Figure 2.52: Classification of Modulation Control Scheme                                                                                                           |

| Figure 2.53: Multicarrier SPWM control strategies                                                                                                                  |

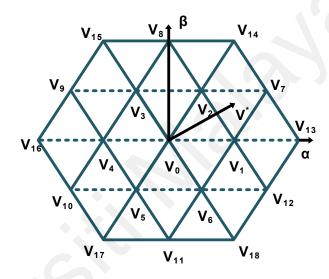

| Figure 2.54: SVM Method                                                                                                                                            |

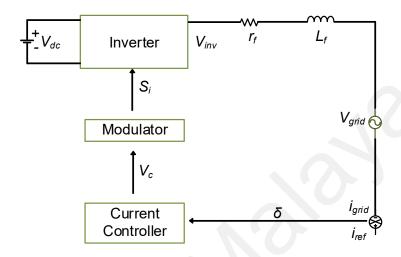

| Figure 2.55: Basic current control scheme54                                                                                                                        |

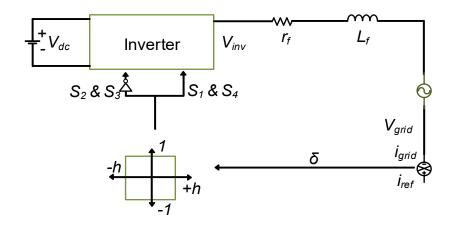

| Figure 2.56: HCC with single-band                                                                                                                                  |

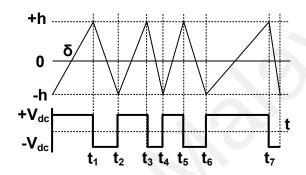

| Figure 2.57: Hysteresis modulator                                                                                                                                  |

| Figure 2.58: Ramp-comparison current-control scheme                                                                                                                |

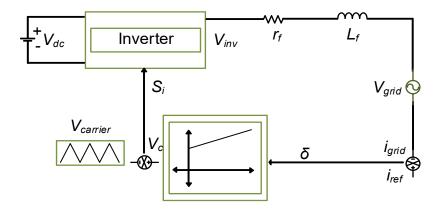

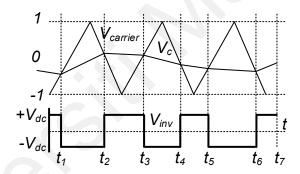

| Figure 2.59: Inverter output voltage achieved via comparison between control signal V and triangular carrier voltage V <sub>carrier</sub>                          |

| Figure 2.60: Basic structure of predictive current control                                                                                                         |

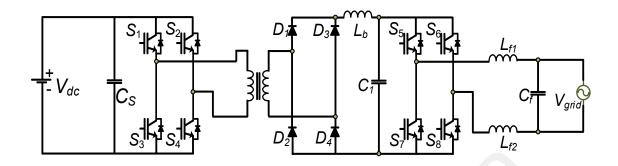

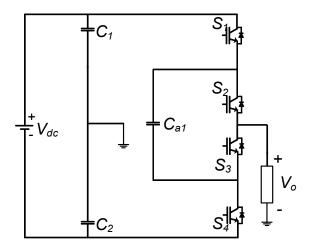

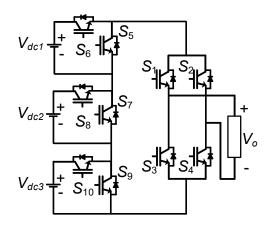

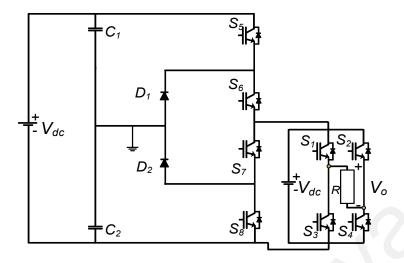

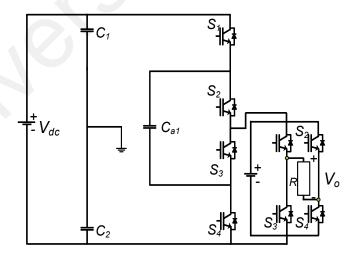

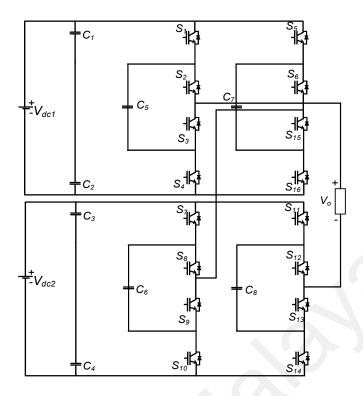

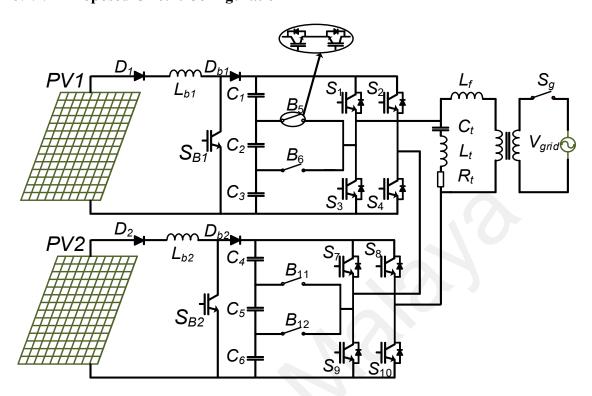

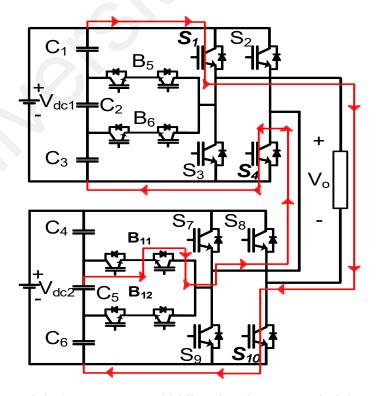

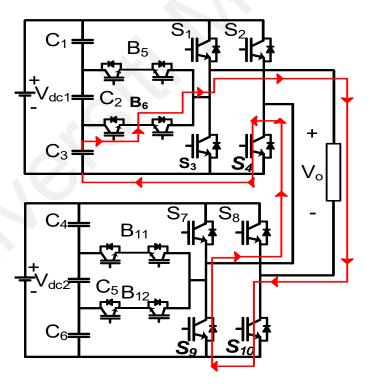

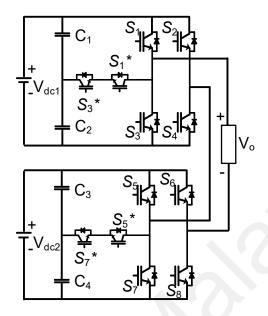

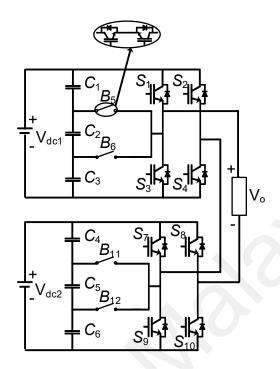

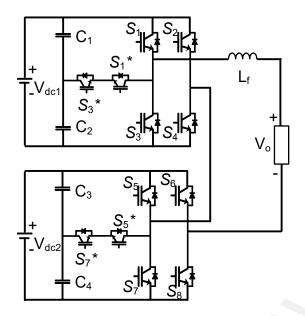

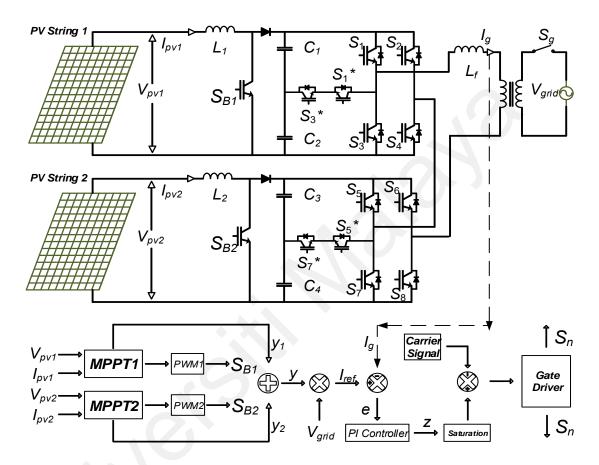

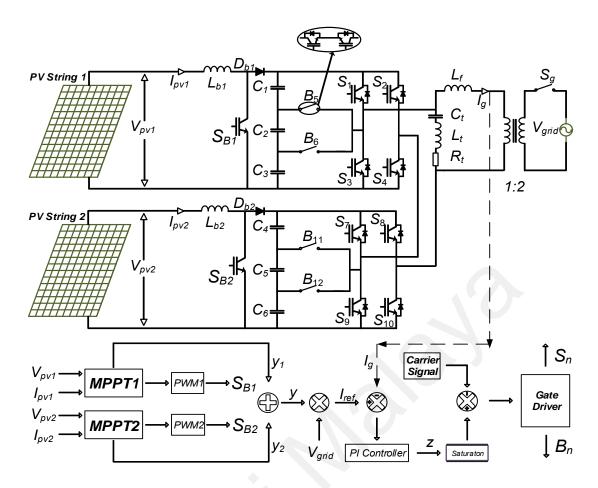

| Figure 3.1: Proposed single-phase TCHB grid-tied inverter topology                                                                                                 |

| Figure 3.2: Comparison of TCHB against SCHB and CCHB for a) <i>NIGBT</i> b) <i>Ndevice</i> c) <i>Vstand</i> , <i>i</i> d) CF and e) Range of α Vs b <sub>max</sub> |

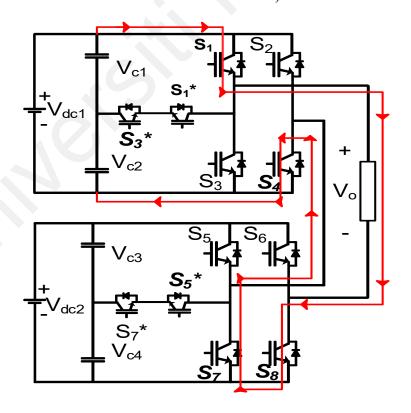

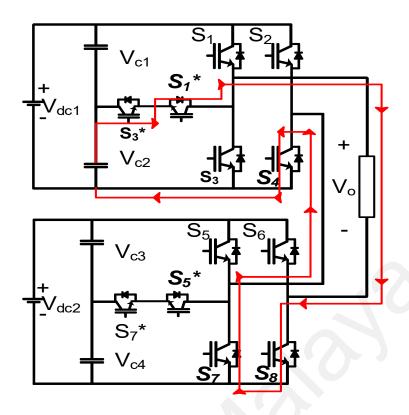

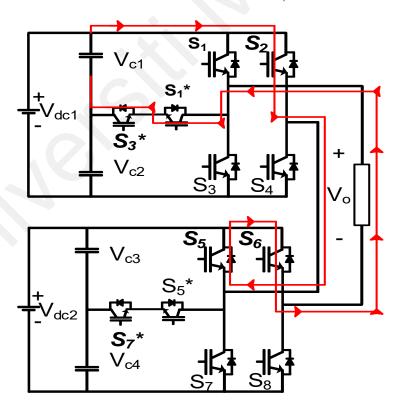

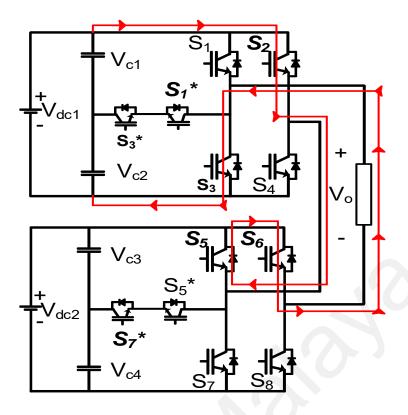

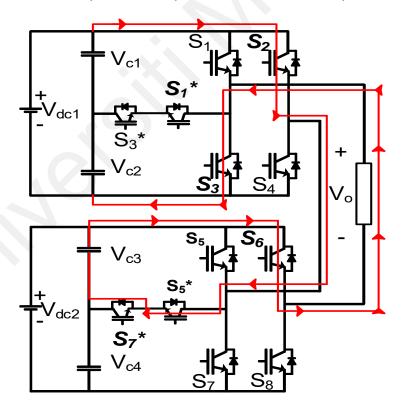

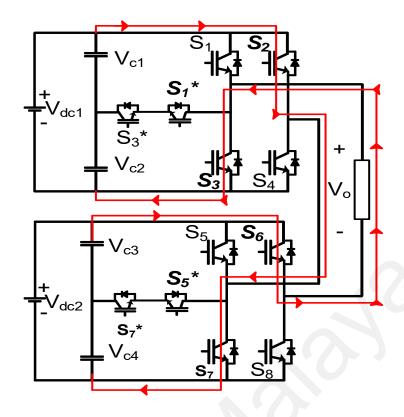

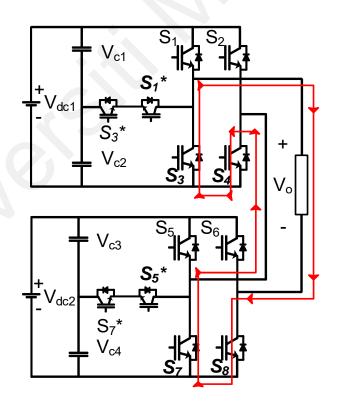

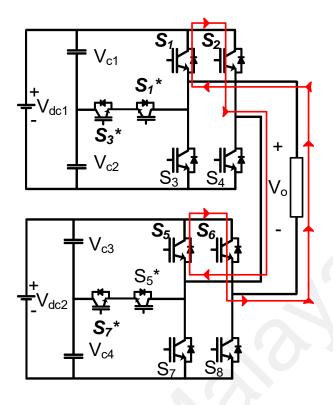

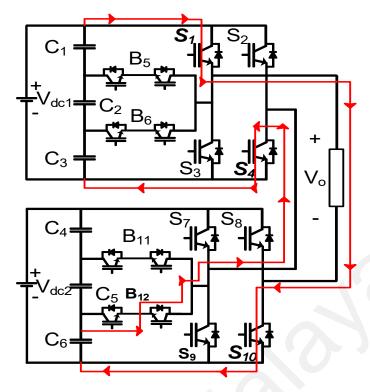

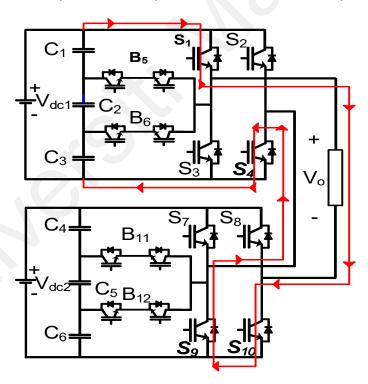

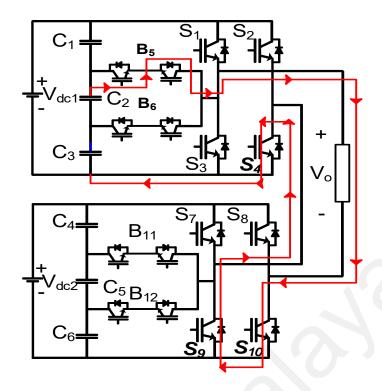

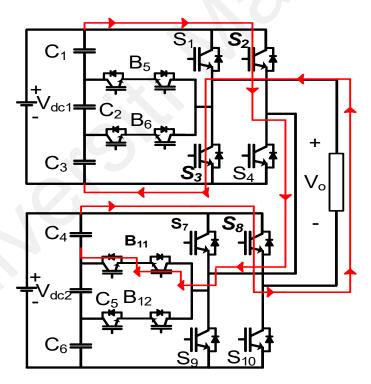

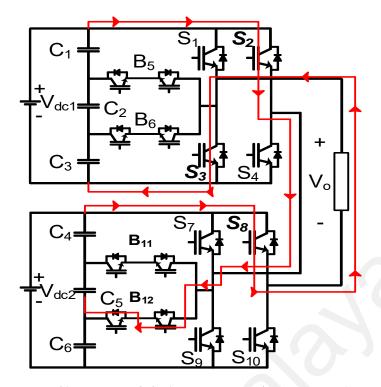

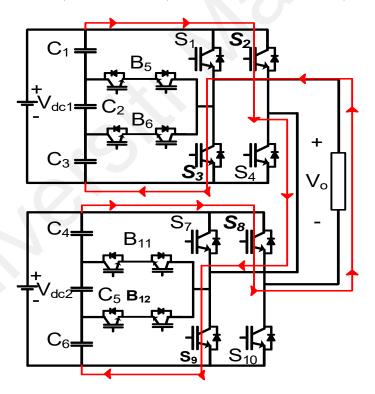

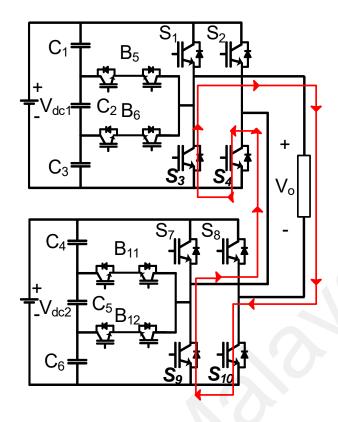

| Figure 3.3: (a-d) Modes of Operation for $Vout > 0$ , (e-h) Modes of Operation for $Vout < 0$ and (i-j) Modes of Operation for Zero and Zero*                      |

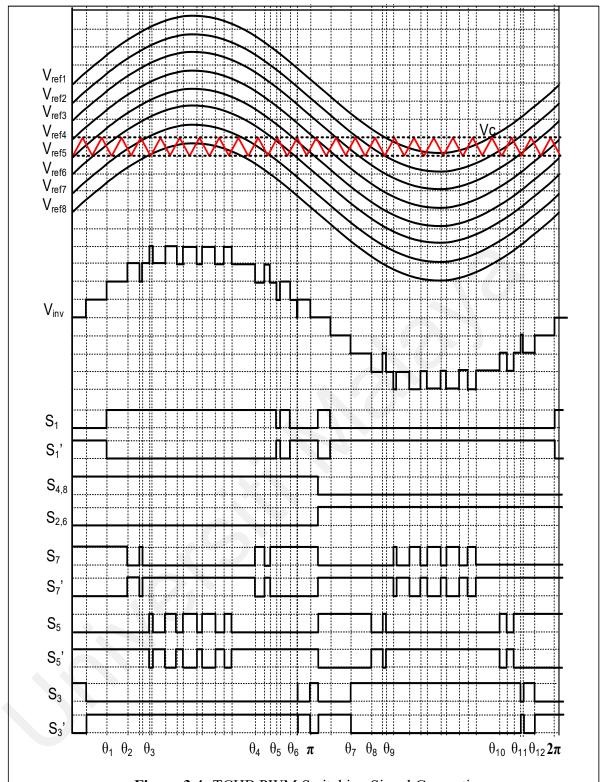

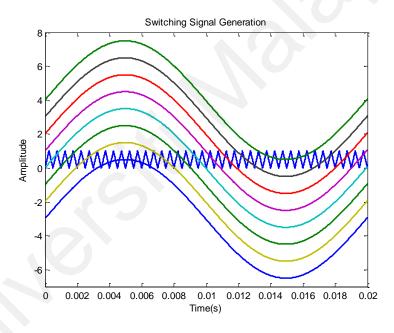

| Figure 3.4: TCHB PWM Switching Signal Generation                                                                                                                   |

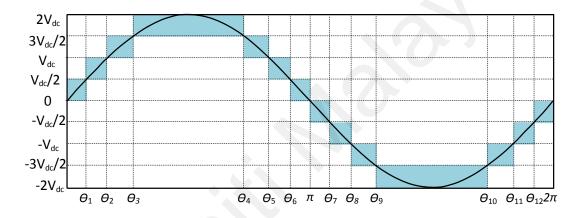

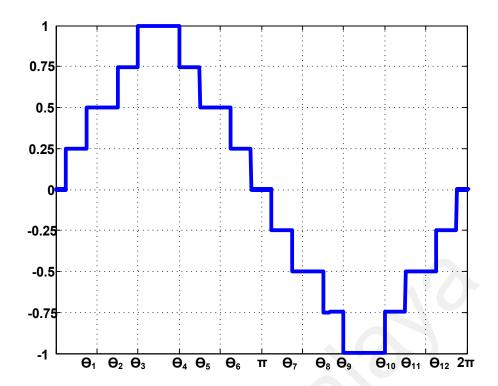

| Figure 3.5: Nine-level Inverter Voltage <i>Vinv</i>                                                                                                                |

| Figure 3.6: Nine-level output voltage with switching angles                                                                                                        |

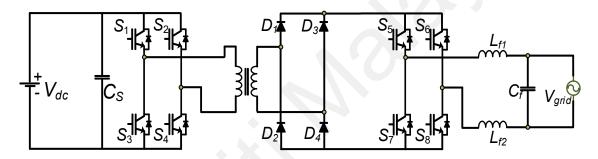

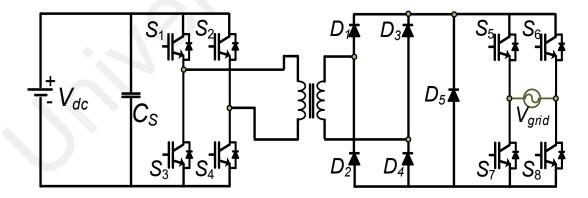

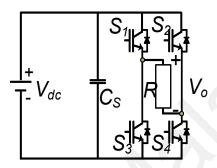

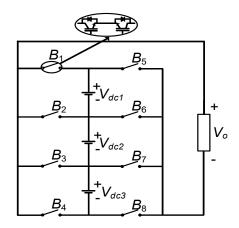

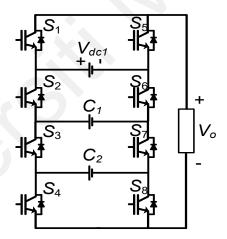

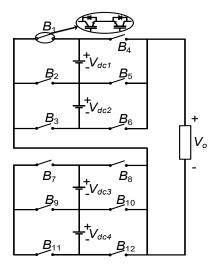

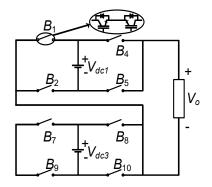

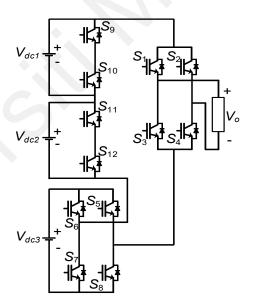

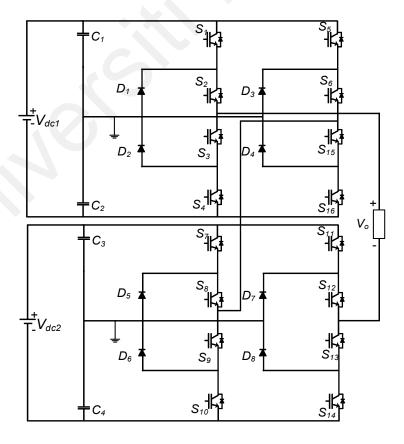

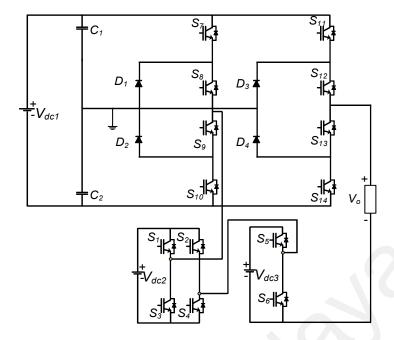

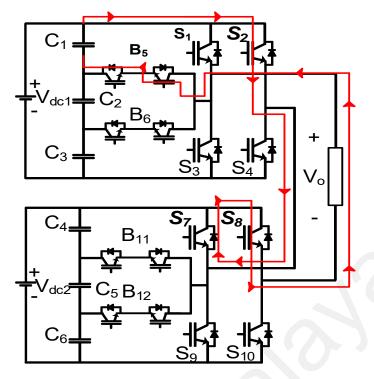

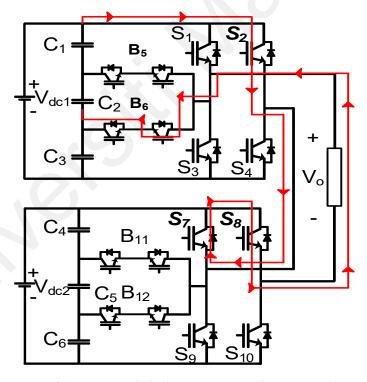

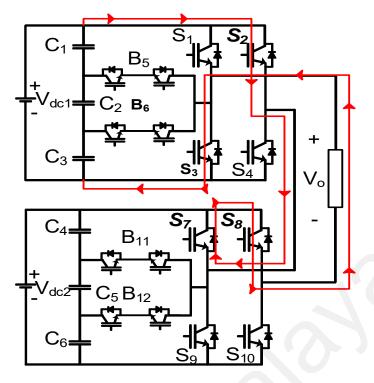

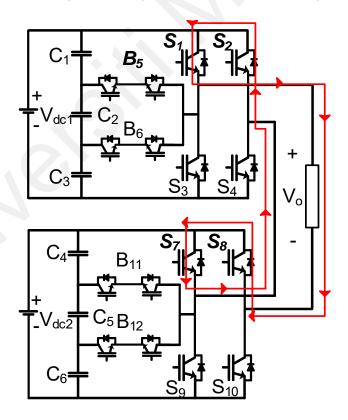

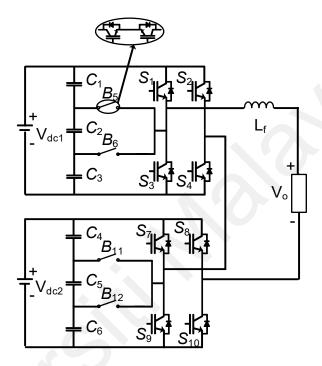

| Figure 3.7: Proposed single-phase PiCHB grid-tied multilevel inverter                                                                                              |

| Figure 3.8: Comparative Analysis for PiCHB against SCHB and CCHB for (a) <b>NIGBT</b> , (b) <b>Ndriver</b> , (c) <b>Ndevice</b> , (d) <b>Pcond</b> , (e) <b>Pswit</b> (f) <b>Vstand</b> , <b>i</b> (g) CF and (h) Range of weight factor Vs Maximum Number of Capacitors |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.9: (a-f) Modes of Operation for <i>Vout</i> > <b>0</b> , (g-l) Modes of Operation for <i>Vout</i> < <b>0</b> and (m-n) Modes of Operation for Zero and Zero*91                                                                                                  |

| Figure 3.10: Thirteen-level (a) Switching Signals and (b) Inverter Output-Voltage99                                                                                                                                                                                      |

| Figure 3.11: Inverter Output-voltage of the proposed PiCHB inverter                                                                                                                                                                                                      |

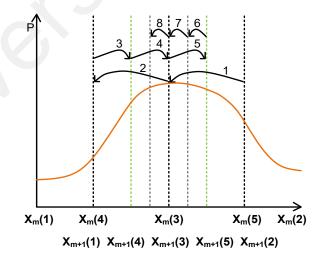

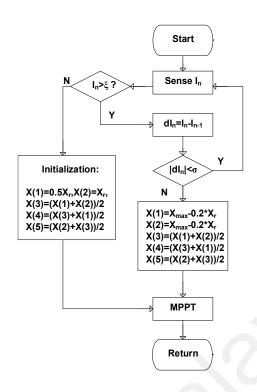

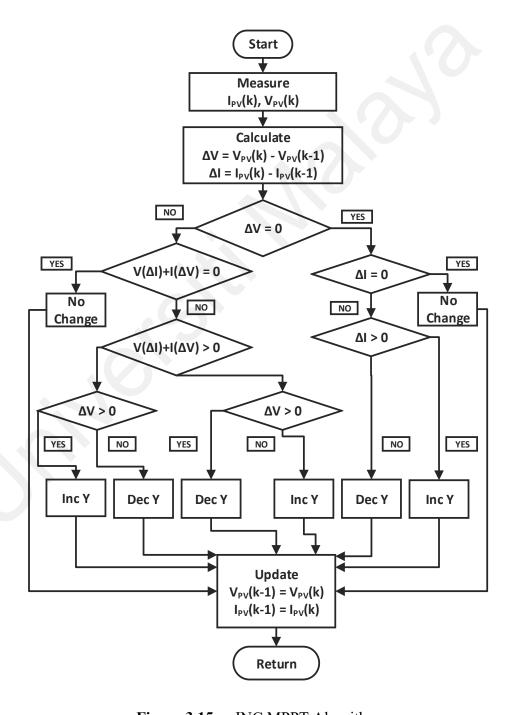

| Figure 3.12: mINC Flowchart                                                                                                                                                                                                                                              |

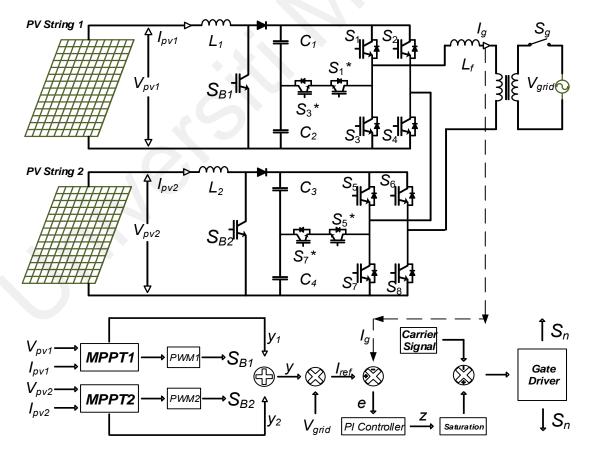

| Figure 3.13: Proposed closed-loop control for the single-phase nine-level grid connected inverter topology                                                                                                                                                               |

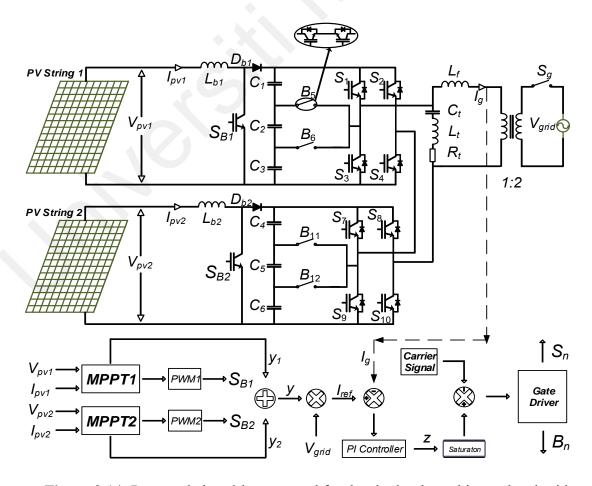

| Figure 3.14: Proposed closed-loop control for the single-phase thirteen-level grid connected inverter topology                                                                                                                                                           |

| Figure 3.15: mINC MPPT Algorithm                                                                                                                                                                                                                                         |

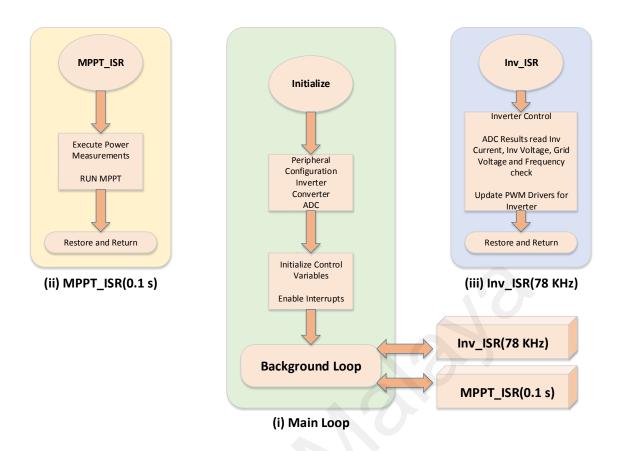

| Figure 3.16: PV Inverter Software Structure (i) Main Loop (ii) MPPT ISR (iii) Inverter ISR                                                                                                                                                                               |

| Figure 4.1: Setup of the proposed TCHB inverter in low-frequency-switching simulation                                                                                                                                                                                    |

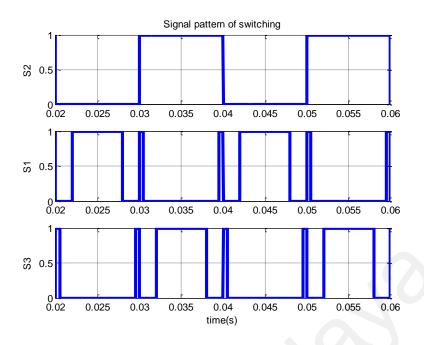

| Figure 4.2: Switching signals for switches S1, S2 and S3                                                                                                                                                                                                                 |

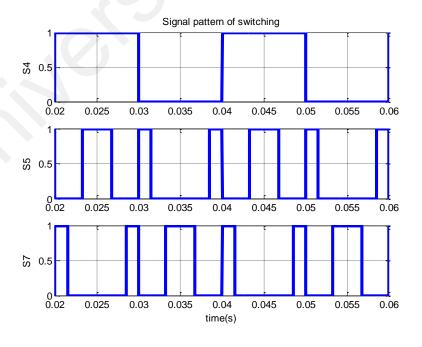

| Figure 4.3: Switching signals for switches S4, S5 and S7                                                                                                                                                                                                                 |

| Figure 4.4: Resulting Output-Voltage for the low-frequency switching signals116                                                                                                                                                                                          |

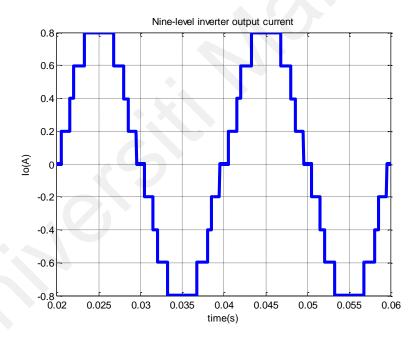

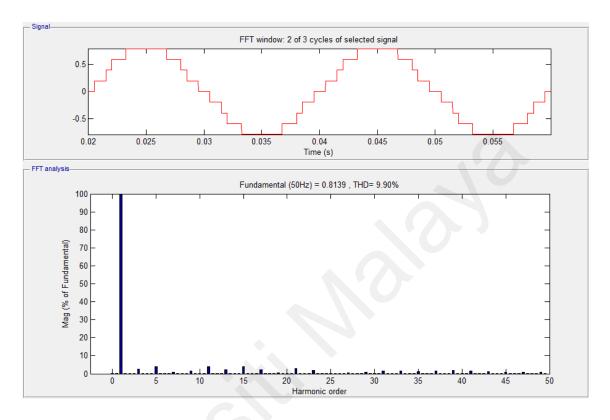

| Figure 4.5: Resulting Output-Current for the low-frequency switching signals116                                                                                                                                                                                          |

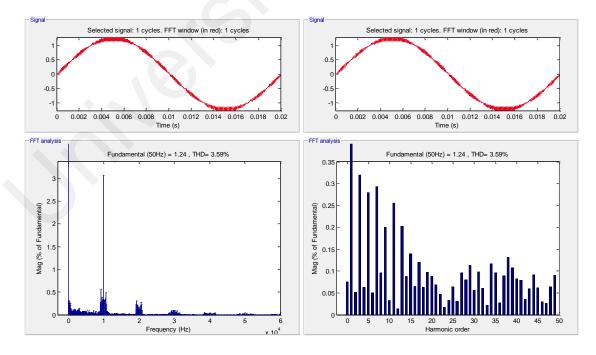

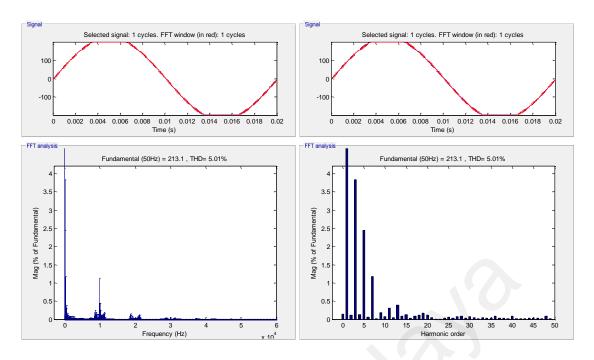

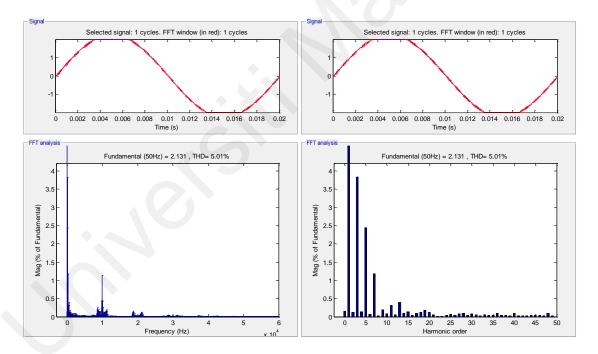

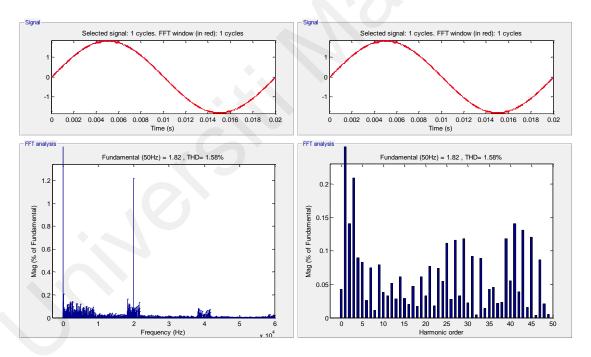

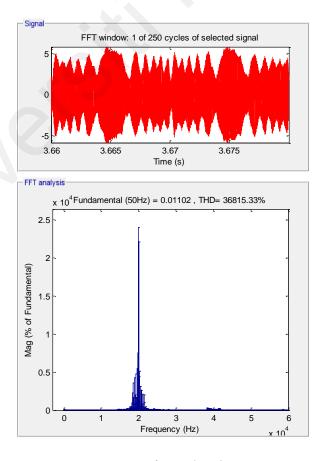

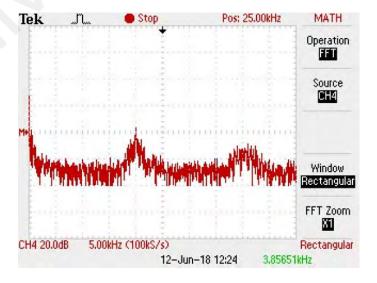

| Figure 4.6: FFT analysis of Output-Current                                                                                                                                                                                                                               |

| Figure 4.7: Setup of the proposed inverter in low-frequency-switching simulation118                                                                                                                                                                                      |

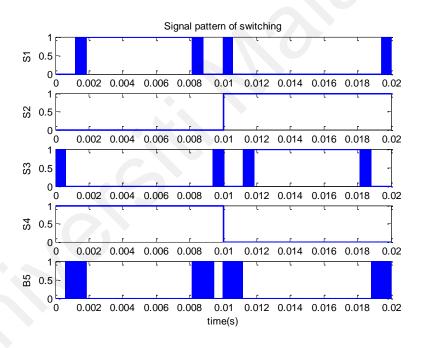

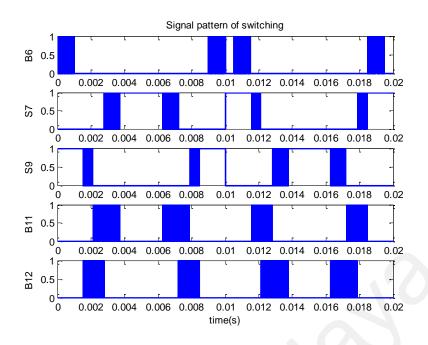

| Figure 4.8: Switching signals for the switches S1, S2, S3, B5 and B6118                                                                                                                                                                                                  |

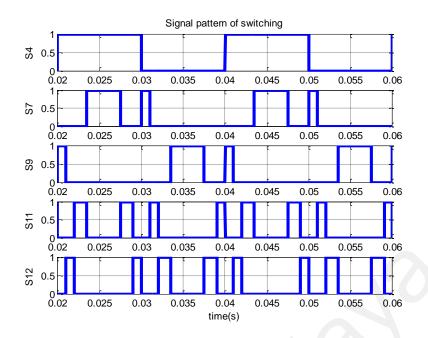

| Figure 4.9: Switching signals for the switches S4, S7, S9, B11 and B12119                                                                                                                                                                                                |

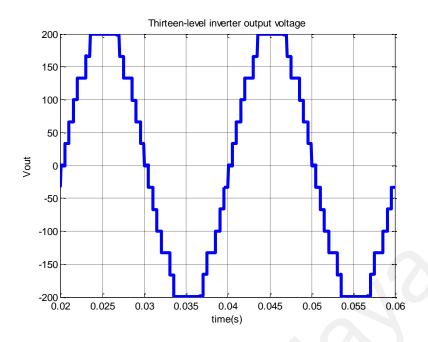

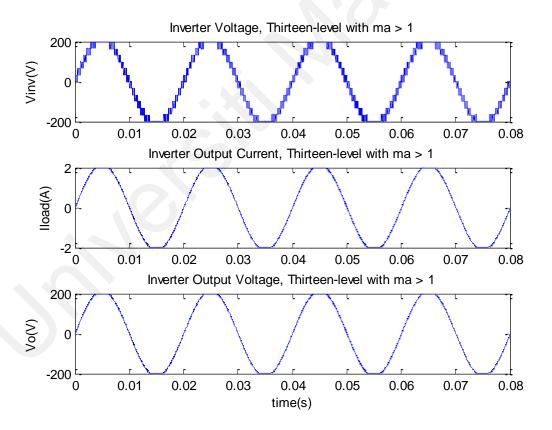

| Figure 4.10: Resulting Output-Voltage for the low-frequency switching signals 120                                                                                                                                                                                        |

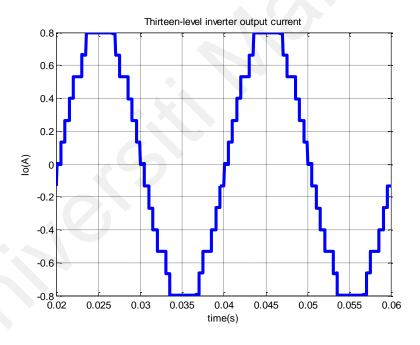

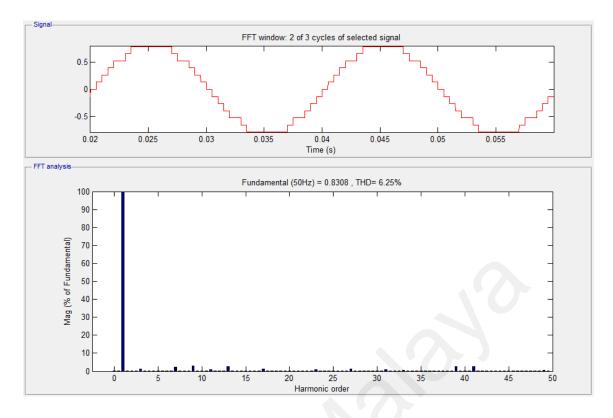

| Figure 4.11: Resulting Output-Current for the low-frequency switching signals120                                                                                                                                                                                         |

| Figure 4.12: FFT analysis of the Output-Current                                                                                                                                                                                                                          |

| Figure 4.13: Setup of the proposed TCHB inverter at high frequency switching                                                                                | 122 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

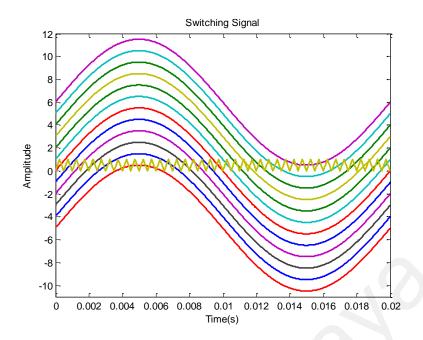

| Figure 4.14: Switching Signal Generation for high frequency switching                                                                                       | 122 |

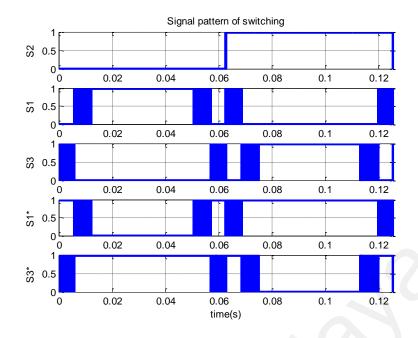

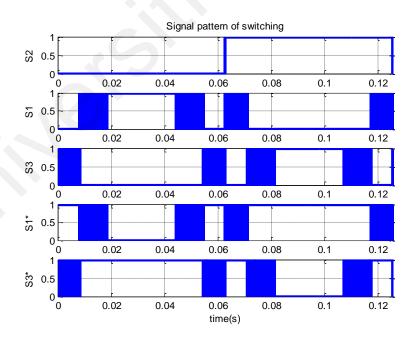

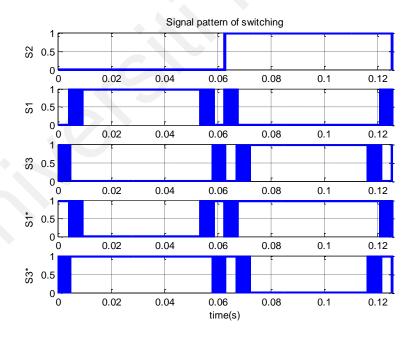

| Figure 4.15: Switching Signals for Switches S1, S1*, S3, S3*, & S2                                                                                          | 123 |

| Figure 4.16: Switching Signals for Switches S5, S5*, S7, S7* and S4                                                                                         | 123 |

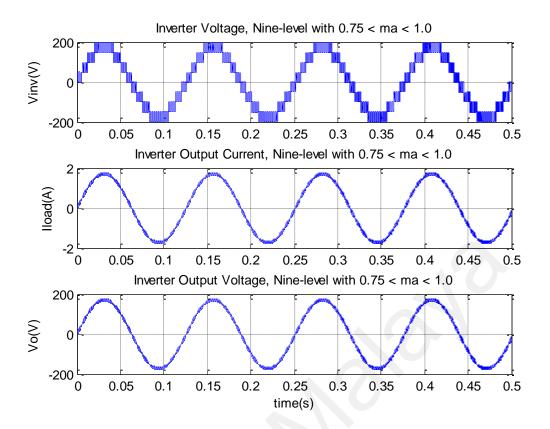

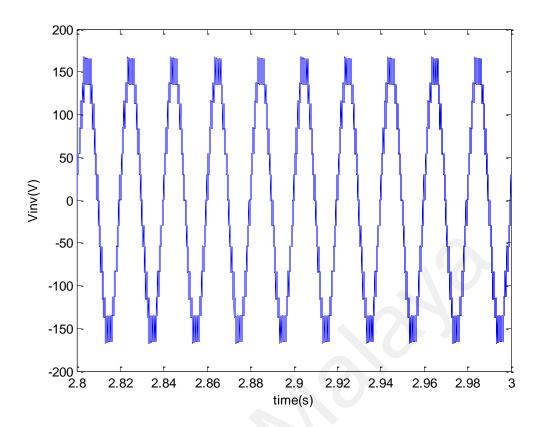

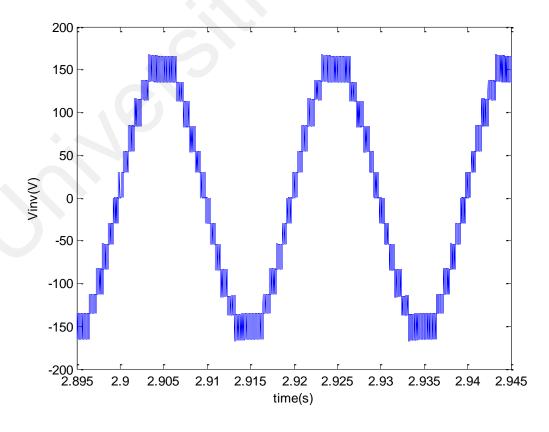

| Figure 4.17: Inverter-Voltage, Output-Current and Output-Voltage waveforms proposed TCHB inverter when $\mathbf{Ma} = 0.87$ was set between 0.75 and 1      |     |

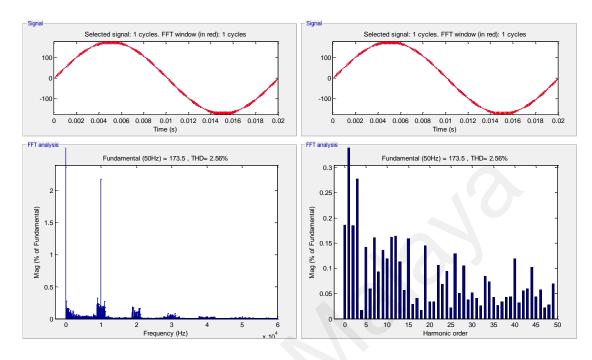

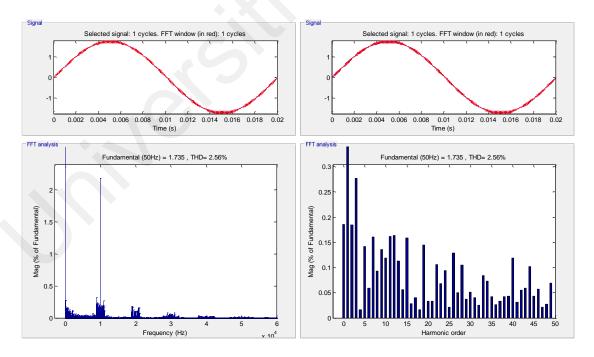

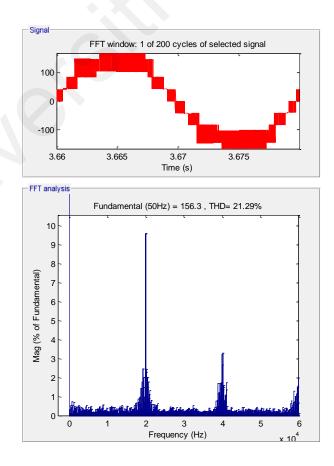

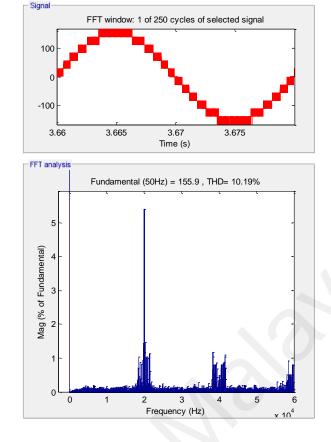

| Figure 4.18: FFT analysis of Output-Voltage waveforms of the proposed TCHB in when <i>Ma</i> was set between 0.75 and 1                                     |     |

| Figure 4.19: FFT analysis of Output-Current waveforms of the proposed TCHB in when <i>Ma</i> was set between 0.75 and 1                                     |     |

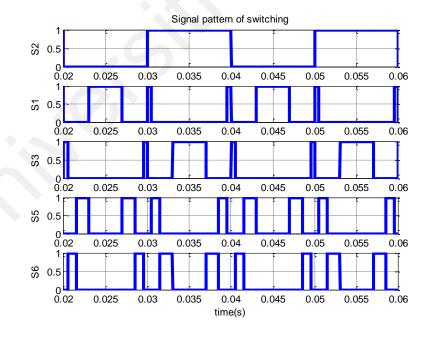

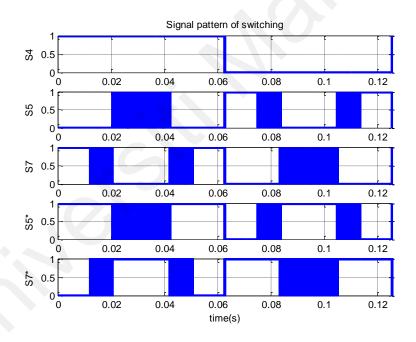

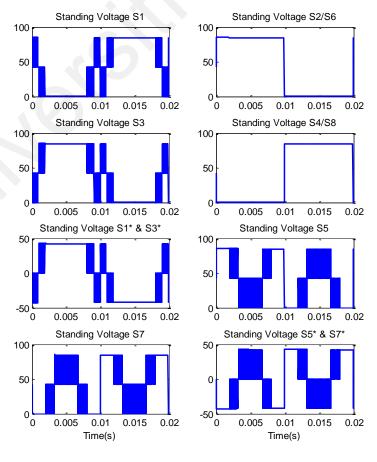

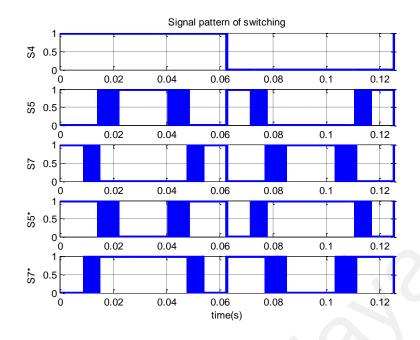

| Figure 4.20: Switching signals for all switches                                                                                                             | 126 |

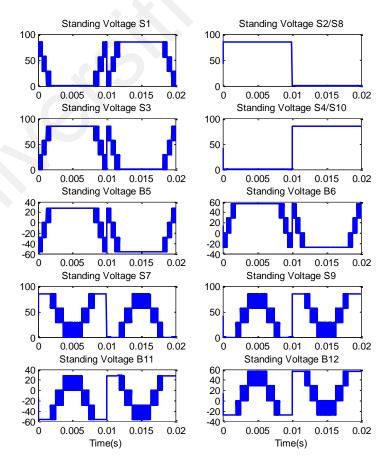

| Figure 4.21: Corresponding Standing-Voltages                                                                                                                | 126 |

| Figure 4.22: Switching signals for S1, S3, S1*, S3* and S2                                                                                                  | 127 |

| Figure 4.23: Switching signals for the switches S5, S7, S5*, S7* and S4                                                                                     | 128 |

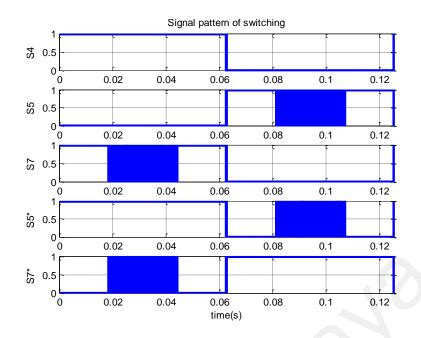

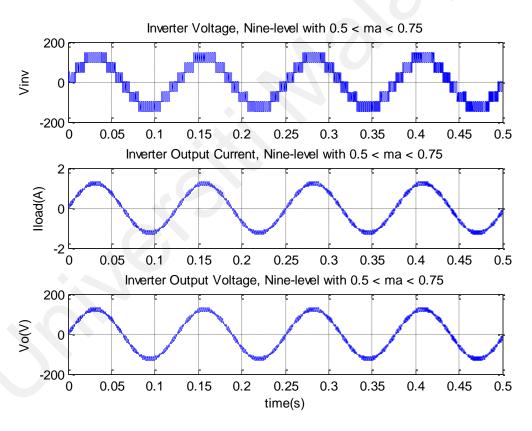

| Figure 4.24: Inverter-voltage, output-current and the output-voltage waveforms $\mathbf{Ma} = 0$ . 67 was set to be between 0.5 and 0.75                    |     |

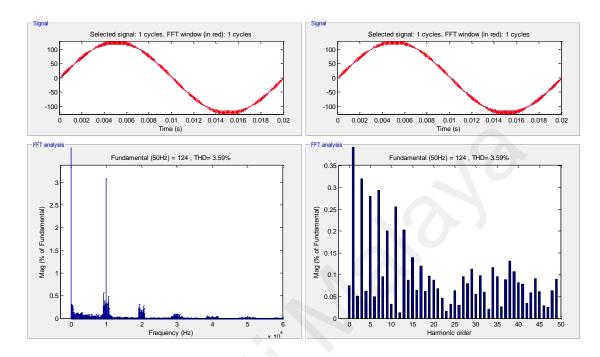

| Figure 4.25: FFT analysis of Output-Voltage waveforms of the proposed TCHB in when <i>Ma</i> was set between 0.5 and 0.75                                   |     |

| Figure 4.26: FFT analysis of Output-Current waveforms of the proposed TCHB in when <i>Ma</i> was set between 0.5 and 0.75                                   |     |

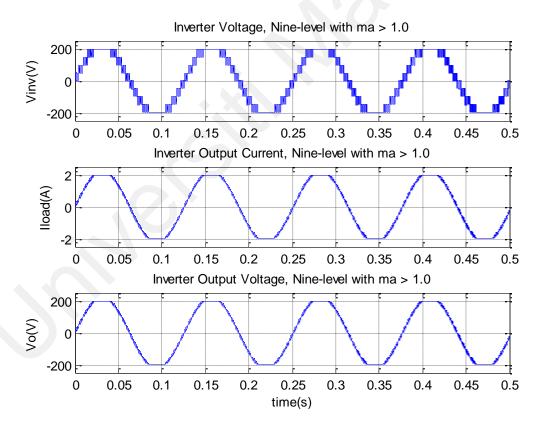

| Figure 4.27: Switching signals for the switches S1, S3, S1*, S3* and S2                                                                                     | 130 |

| Figure 4.28: Switching signals for the switches S5, S7, S5*, S7* and S4                                                                                     | 131 |

| Figure 4.29: Inverter-voltage, output-current and the output-voltage waveforms proposed TCHB inverter when the modulation index $M\alpha = 1.17$ exceeded 1 |     |

| Figure 4.30: FFT analysis of Output-Voltage waveforms of the proposed TCHB in when <i>Ma</i> was set to exceed 1                                            |     |

| Figure 4.31: FFT analysis of Output-Current waveforms of the proposed TCHB in when <i>Ma</i> was set to exceed 1                                            |     |

| Figure 4.32: Setup of the PiCHB inverter at high frequency switching                                                                                        | 133 |

| Figure 4.33: Switching Signal Generation                                                                                                                      | .134 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

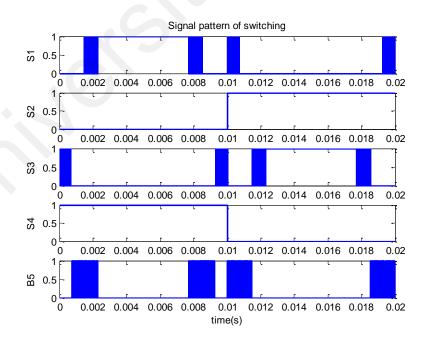

| Figure 4.34: Switching Signals for Switches S1, S2, S3, S4, & B5                                                                                              | .134 |

| Figure 4.35: Switching Signals for Switches B6, S7, S8, S9, & S4                                                                                              | .135 |

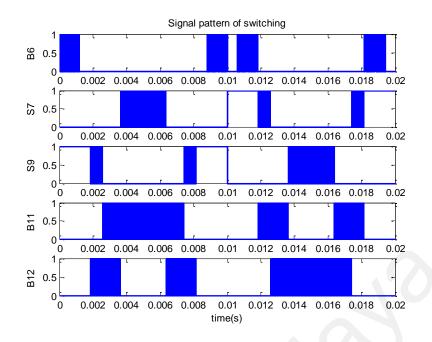

| Figure 4.36: Inverter-Voltage, Output-Current and Output-Voltage waveforms of proposed PiCHB inverter when $\mathbf{Ma} = 0.93$ was set between 0.83 and 1    |      |

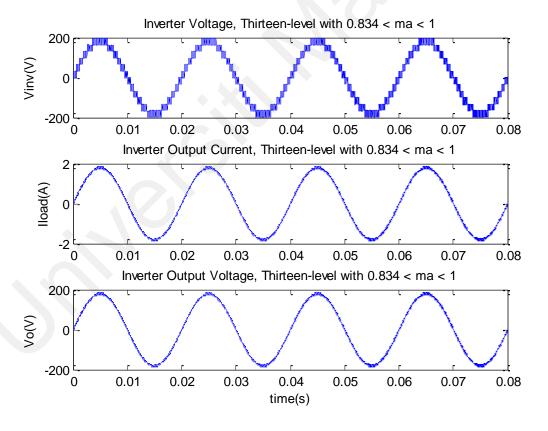

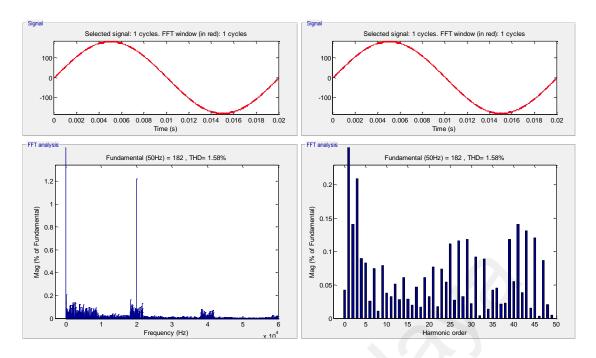

| Figure 4.37: FFT analysis of Output-Voltage waveforms of the proposed TCHB inv when <i>Ma</i> was set between 0.83 and 1                                      |      |

| Figure 4.38: FFT analysis of Output-Current waveforms of the proposed TCHB inv when <i>Ma</i> was set between 0.83 and 1                                      |      |

| Figure 4.39: Switching signals for all switches                                                                                                               | .137 |

| Figure 4.40: Corresponding standing-voltage on the Switches                                                                                                   | .137 |

| Figure 4.41: Switching Signals for Switches S1, S2, S3, S4, & B5                                                                                              | .138 |

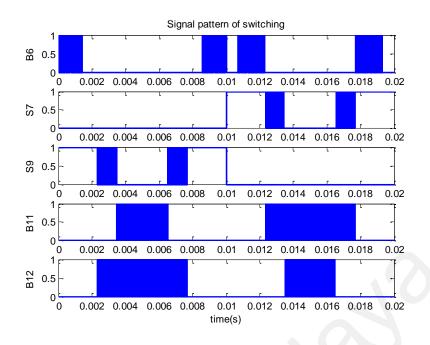

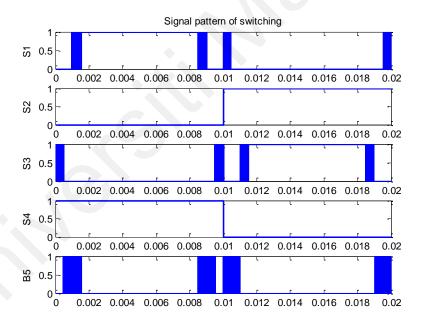

| Figure 4.42: Switching signals for switches B6, S7, S9, B11 and B12                                                                                           | .139 |

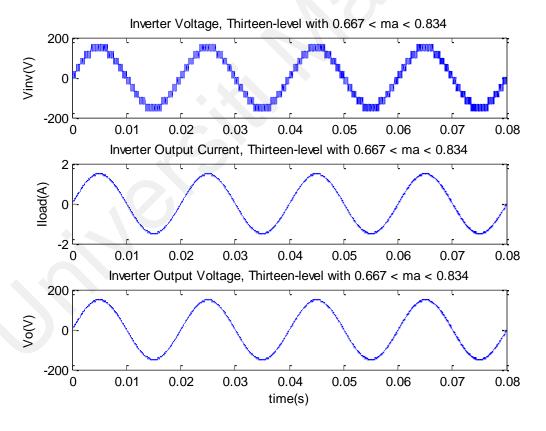

| Figure 4.43: Inverter-Voltage, Output-Current and Output-Voltage waveforms of proposed PiCHB inverter when $\mathbf{Ma} = 0.75$ was set between 0.67 and 0.83 |      |

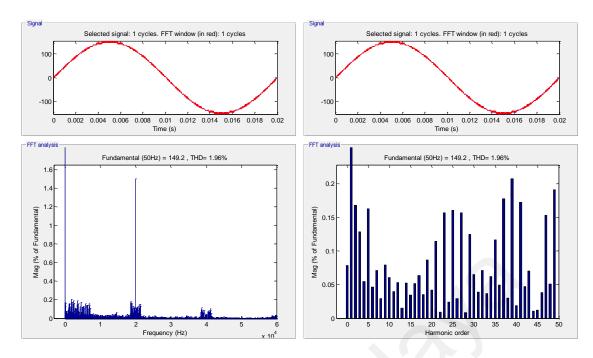

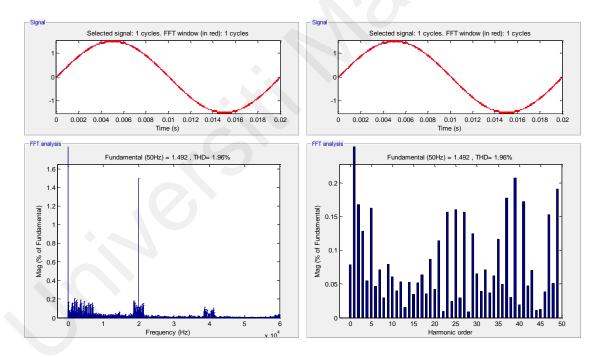

| Figure 4.44: FFT analysis of Output-Voltage waveforms of the proposed TCHB inv when <i>Ma</i> was set between 0.67 and 0.83                                   |      |

| Figure 4.45: FFT analysis of Output-Current waveforms of the proposed TCHB inv when <i>Ma</i> was set between 0.67 and 0.83                                   |      |

| Figure 4.46: Switching signals for switches S1,S2,S3 and S4                                                                                                   | .141 |

| Figure 4.47: Switching signals for switches B6, S7, S9, B11 and B12                                                                                           | .142 |

| Figure 4.48: Inverter-voltage, output-current and output-voltage waveforms of prop PiCHB inverter when modulation index $Ma = 1.17$ was set to exceed 1       |      |

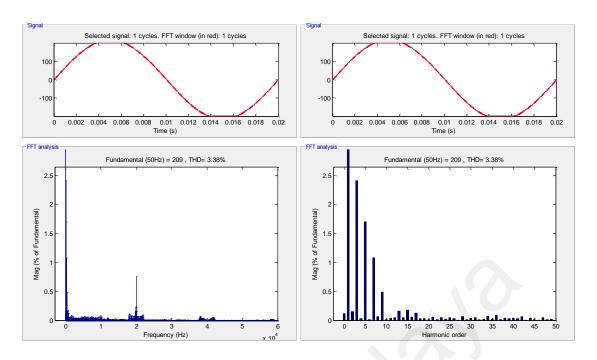

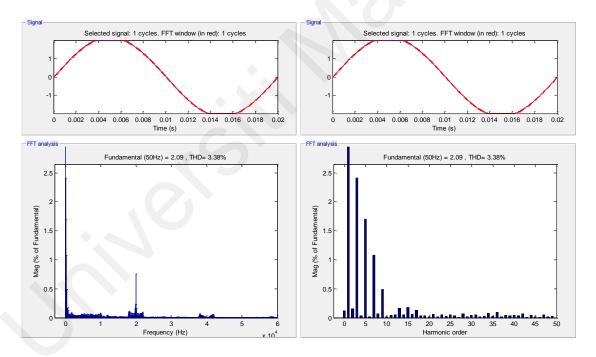

| Figure 4.49: FFT analysis of Output-Voltage waveforms of the proposed PiCHB inv when <i>Ma</i> was set exceed 1                                               |      |

| Figure 4.50: FFT analysis of Output-Current waveforms of the proposed PiCHB inv when <i>Ma</i> was set exceed 1                                               |      |

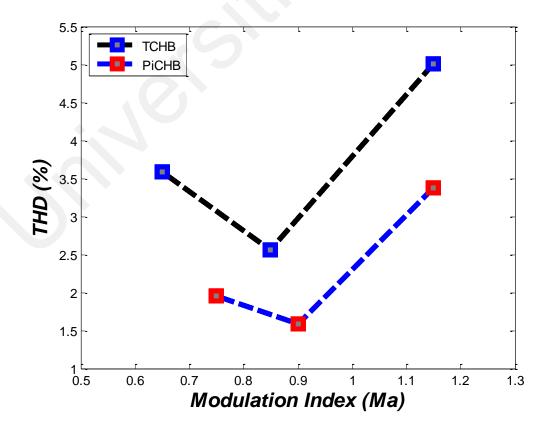

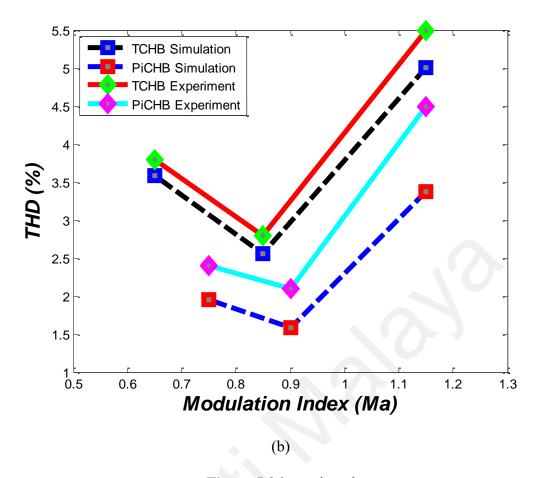

| Figure 4.51: Comparison of THD (%) Vs Modulation Index (Ma)                                                                                                   | .144 |

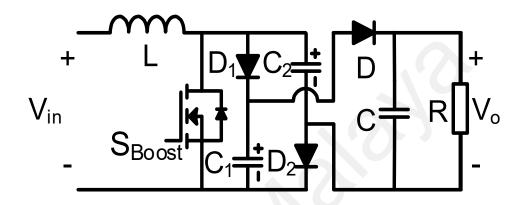

| Figure 4.52: Modified Boost Converter                                                                                                                         | .145 |

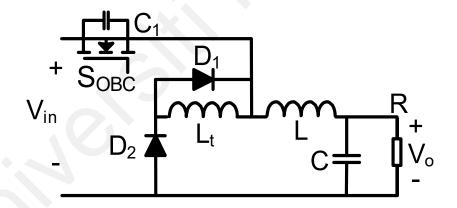

| Figure 4.53: Modified Buck Converter                                                | 145 |

|-------------------------------------------------------------------------------------|-----|

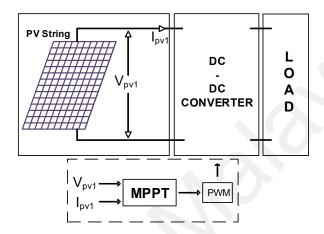

| Figure 4.54: PV system with proposed mINC MPPT                                      | 146 |

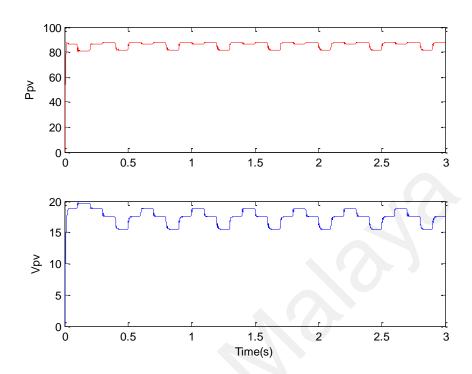

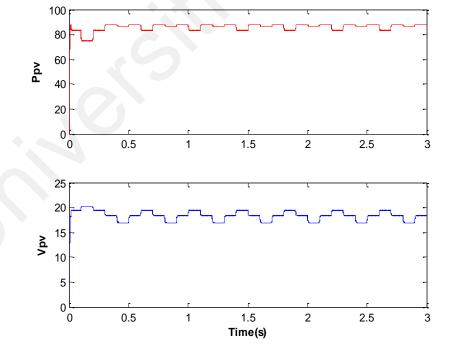

| Figure 4.55: Simulation results for MINC on Modified Boost Converter                | 147 |

| Figure 4.56: Simulation results for MINC on Modified Buck Converter                 | 147 |

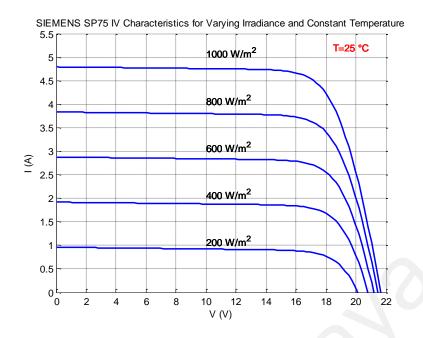

| Figure 4.57: I-V curves for various irradiances and constant temperature            | 149 |

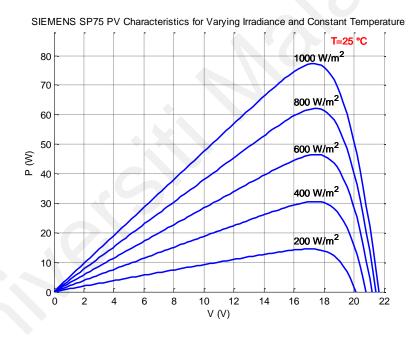

| Figure 4.58: P-V curves for various irradiances but constant temperature            | 149 |

| Figure 4.59: Simulation setup of the TCHB grid-connected PV inverter                | 150 |

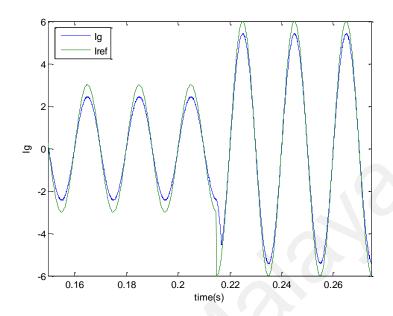

| Figure 4.60: Step response of PI current control scheme                             | 151 |

| Figure 4.61: Zoomed view of the reference tracking                                  | 151 |

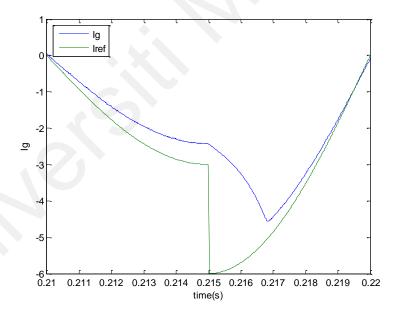

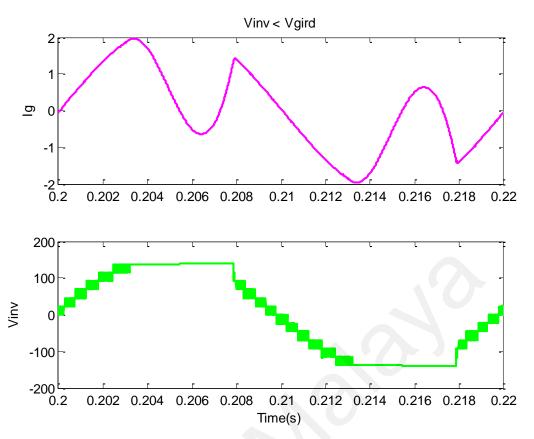

| Figure 4.62: Output-Current and Voltage when $\emph{Vinv} < \emph{Vg}$              | 152 |

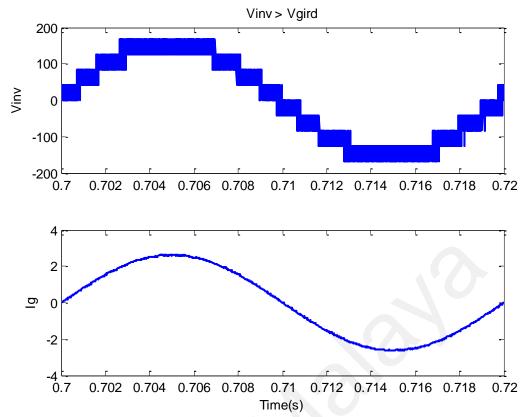

| Figure 4.63: Output-Current and Voltage when $Vinv > Vg$                            | 153 |

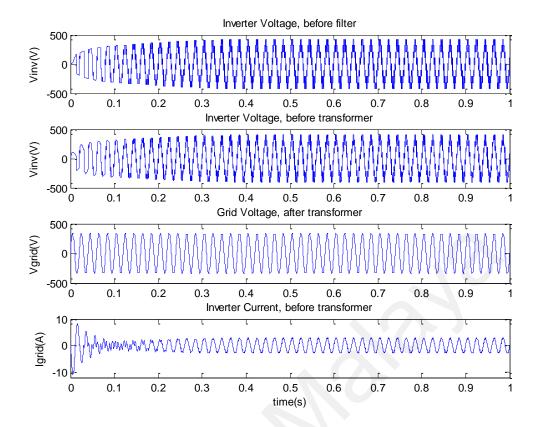

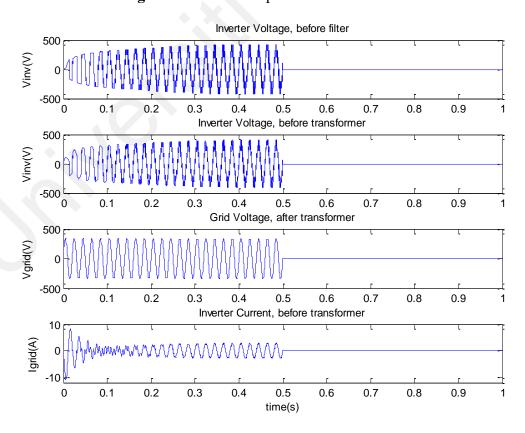

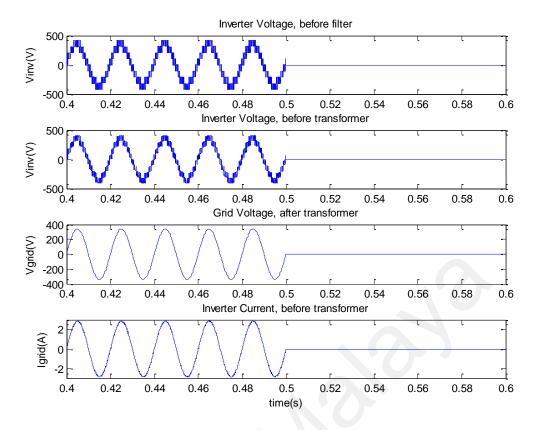

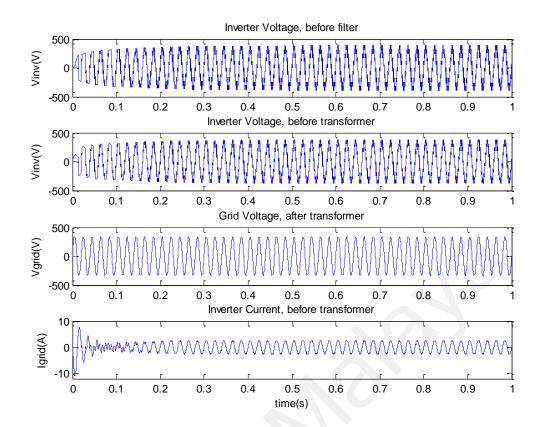

| Figure 4.64: Time response of TCHB inverter                                         | 154 |

| Figure 4.65: Time response of TCHB when grid is disconnected                        | 154 |

| Figure 4.66: Zoomed view for the time response when grid is disconnected            | 155 |

| Figure 4.67: Simulation setup of the PiCHB grid-connected PV inverter               | 156 |

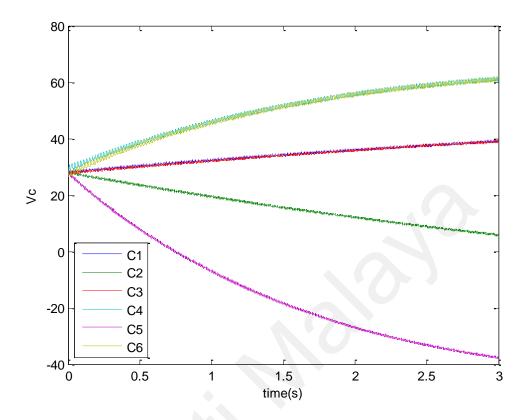

| Figure 4.68: RLC passive balancing circuit                                          | 157 |

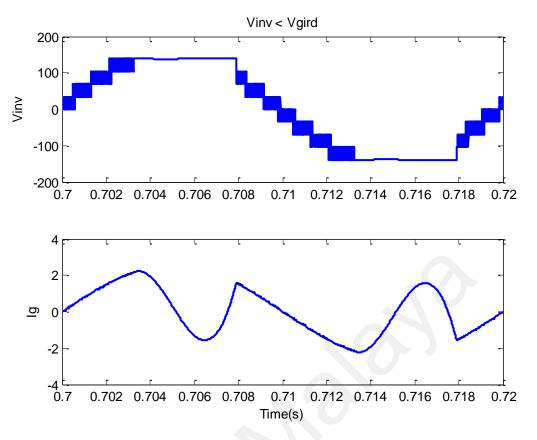

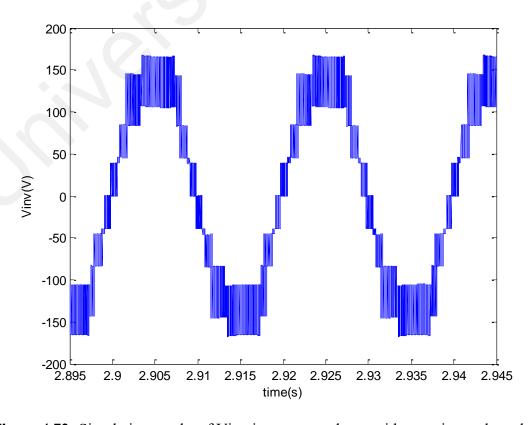

| Figure 4.69: Capacitor voltage levels in unbalanced case                            | 159 |

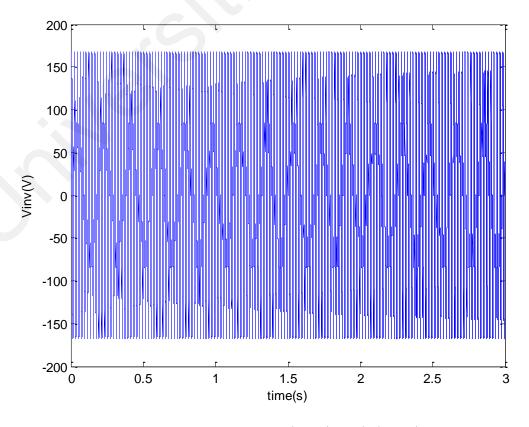

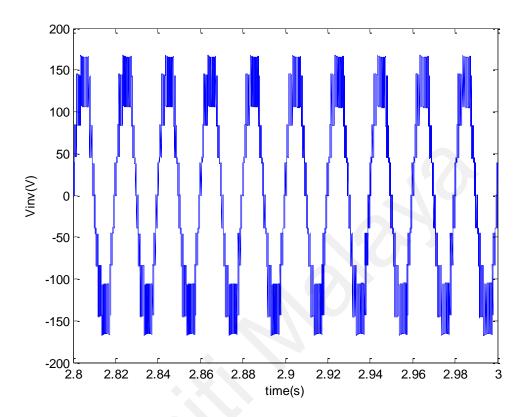

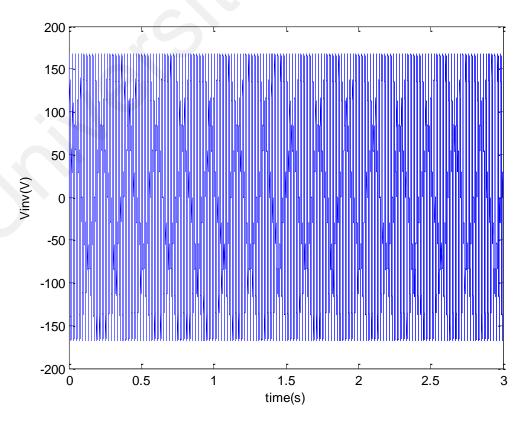

| Figure 4.70: Inverter Output Voltage in Unbalanced case                             | 159 |

| Figure 4.71: Zoomin view of the Inverter Output Voltage                             | 160 |

| Figure 4.72: Simulation results of Vinv in correspondence with experimental results | 160 |

| Figure 4.73: Capacitor voltage levels in balanced case                              | 162 |

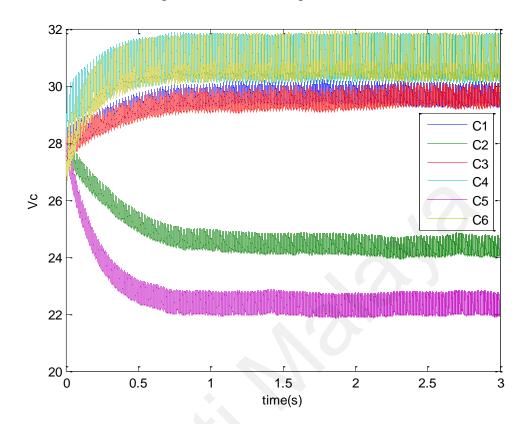

| Figure 4.74: Inverter Output Voltage in balanced case                               | 162 |

| Figure 4.75: Zoomin view of the Inverter Output Voltage in balanced case            | 163 |

| Figure 4.76: Simulation results of Viny in correspondence with experimental results | 163 |

| Figure 4.77: FFT for Unbalanced Output-Voltage                                                                                                                                       | 164 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.78: FFT for Balanced Output-Voltage                                                                                                                                         | 165 |

| Figure 4.79: FFT for Balancing Current                                                                                                                                               | 165 |

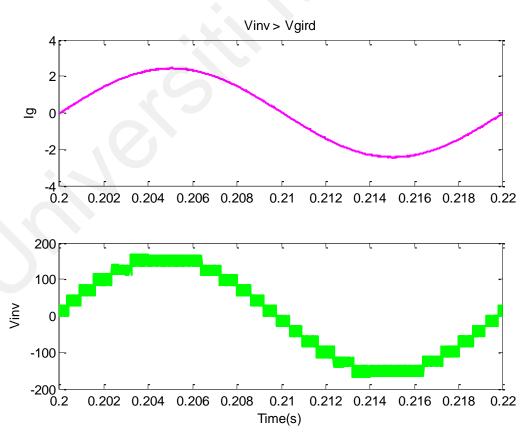

| Figure 4.80: Output-Current and Voltage when $\emph{Vinv} < \emph{Vg}$ for PiCHB                                                                                                     | 166 |

| Figure 4.81: Output-Current and Voltage when $Vinv > Vg$ for PiCHB                                                                                                                   | 166 |

| Figure 4.82: Time response of the PiCHB inverter with MPPT mode                                                                                                                      | 168 |

| Figure 4.83: Time response PiCHB with MPPT mode when grid is disconnected                                                                                                            | 168 |

| Figure 4.84: Zoomed view for time response when grid is disconnected                                                                                                                 | 169 |

| Figure 5.1: Hardware Prototype                                                                                                                                                       | 171 |

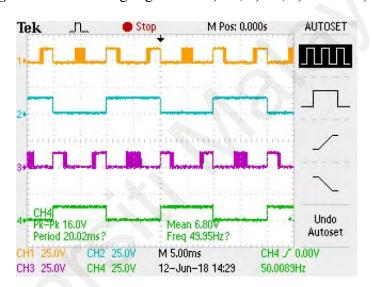

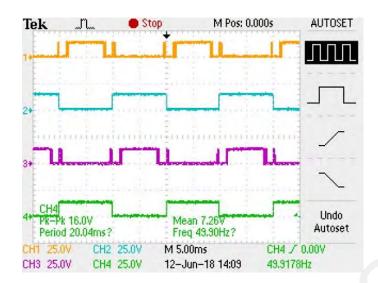

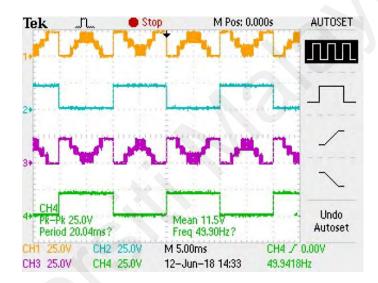

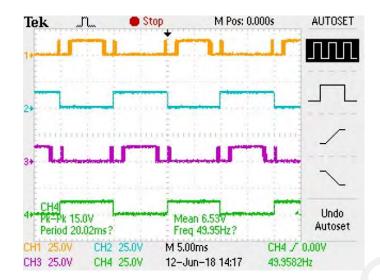

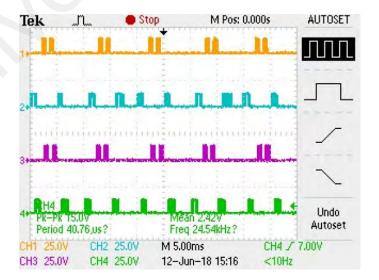

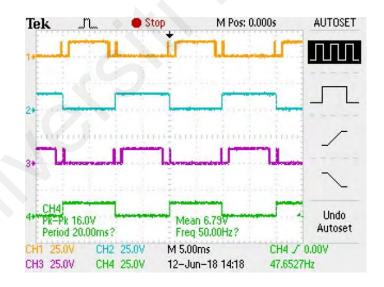

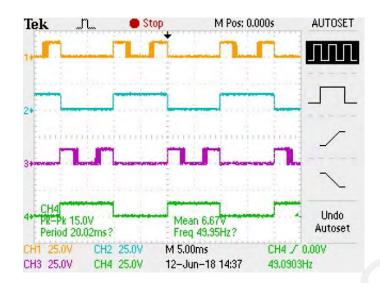

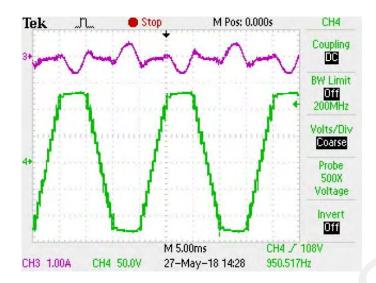

| Figure 5.2: Switching Signals for 1) S1, 2) S2, 3) S3 and 4) S4                                                                                                                      | 173 |

| Figure 5.3: Switching Signals for 1) S5, 2) S6, 3) S7 and 4) S8                                                                                                                      | 173 |

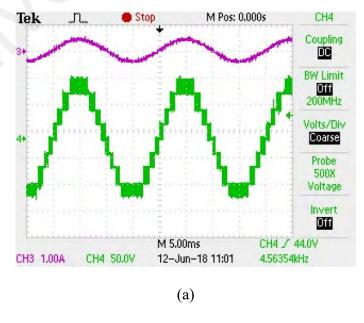

| Figure 5.4: Nine-Level Output (a) when $\mathbf{Ma} = 0.87$ was above 0.75 but below 1 $\mathbf{Ma}$ was above 0.5 but below 0.75 and (c) $\mathbf{Ma}$ was above 0.25 but below 0.5 | ` ' |

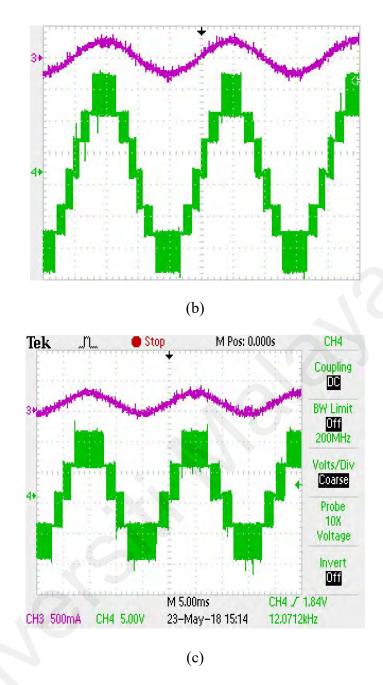

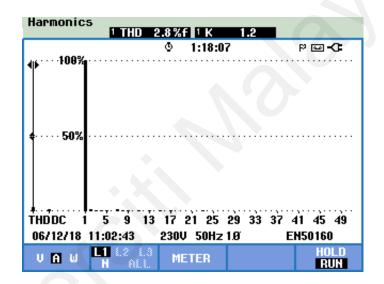

| Figure 5.5: Output-Voltage THD                                                                                                                                                       | 175 |

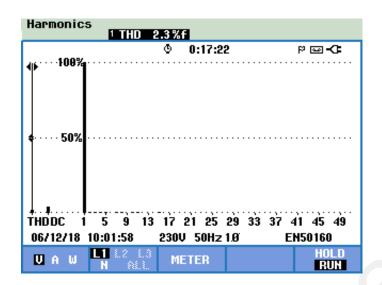

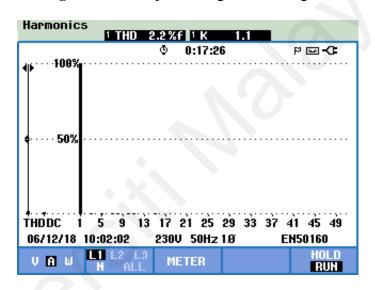

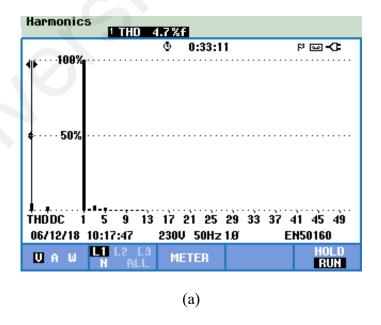

| Figure 5.6: Output-Current THD                                                                                                                                                       | 175 |

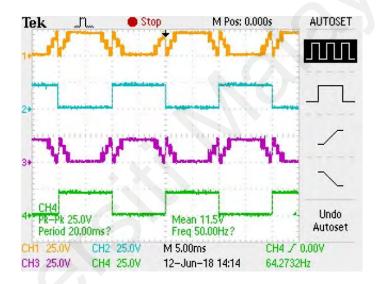

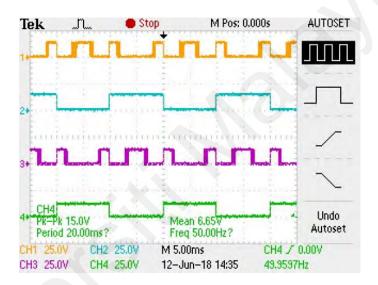

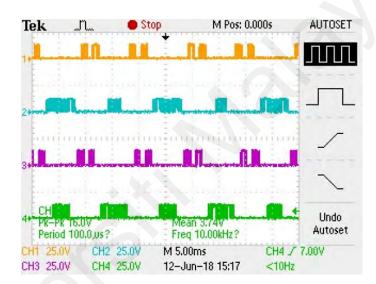

| Figure 5.7: Switching signals for S1, S2, S3 and S4                                                                                                                                  | 176 |

| Figure 5.8: Corresponding Standing-Voltages for S1, S2, S3 and S4                                                                                                                    | 176 |

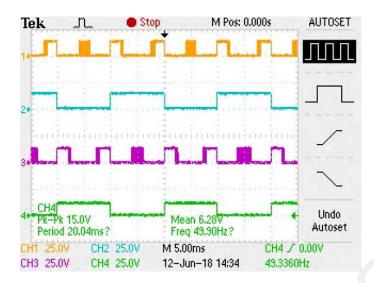

| Figure 5.9: Switching signals for S7, S8, S9 and S10                                                                                                                                 | 177 |

| Figure 5.10: Corresponding Standing-Voltages for S7, S8, S9 and S10                                                                                                                  | 177 |

| Figure 5.11: Switching signals for B5, B11, B6 and B12                                                                                                                               | 177 |

| Figure 5.12: Corresponding Standing-Voltages for B5, B11, B6 and B12                                                                                                                 | 178 |

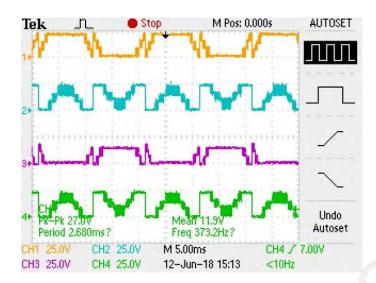

| Figure 5.13: Output-Voltage and Current with $Ma = 0.93$                                                                                                                             | 178 |

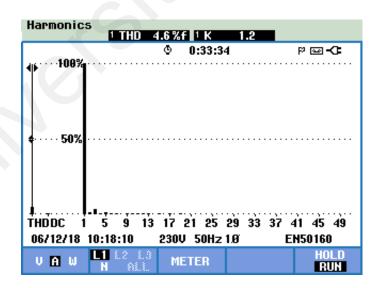

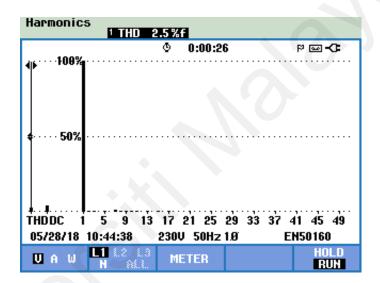

| Figure 5.14: Output-Voltage THD being 2.3 %                                                                                                                                          | 179 |

| Figure 5.15: Output-Current THD being 2.2 %                                                                                                                                          | 179 |

| Figure 5.16: Switching signals for S1, S2, S3 and S4                                                                                                                                 | 180 |

| Figure 5.17: Switching signals for S7, S8, S9 and S10                                                                         | 180   |

|-------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 5.18: Switching signals for B5, B11, B6 and B12                                                                        | .180  |

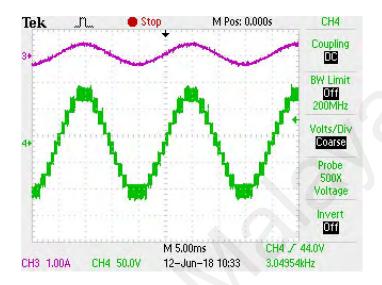

| Figure 5.19: Output-Voltage and current for PiCHB with $Ma = 0.75$ above 0.67 below 0.83                                      |       |

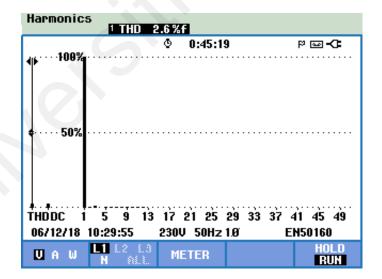

| Figure 5.20: Output-Voltage THD being 2.6 %                                                                                   | .181  |

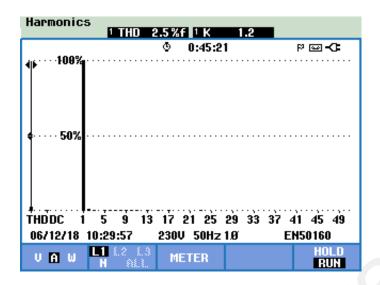

| Figure 5.21: Output-Current THD being 2.5 %                                                                                   | .182  |

| Figure 5.22: Switching signals for S1, S2, S3 and S4                                                                          | .182  |

| Figure 5.23: Switching signals for S7, S8, S9 and S10                                                                         | .183  |

| Figure 5.24: Switching signals for B5, B11, B6 and B12                                                                        | .183  |

| Figure 5.25: Output-Voltage and Current when $\mathbf{Ma} = 1.17$ exceeded 1                                                  | .184  |

| Figure 5.26: <b>Ma</b> >1 (a) Output-Voltage THD (b) Output-Voltage THD (4. comparison of simulation and experimental results |       |

| Figure 5.27: Output-Current THD being 4.6 %                                                                                   | 185   |

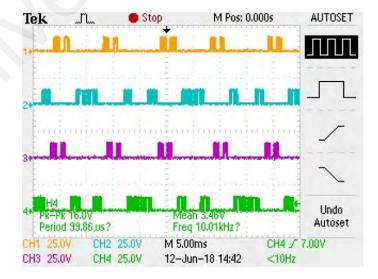

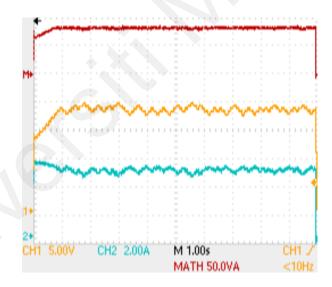

| Figure 5.28: Experimental Results for mINC on Modified Boost Converter                                                        | .186  |

| Figure 5.29: Experimental Results for mINC on Modified Buck Converter                                                         | .186  |

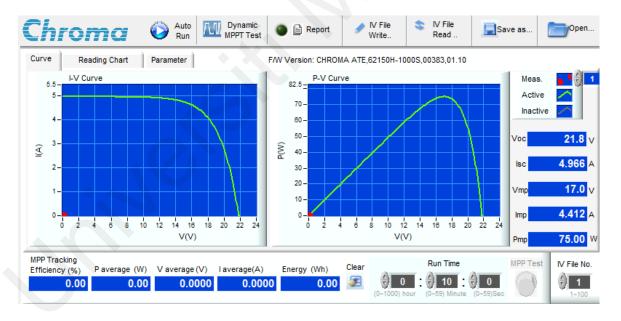

| Figure 5.30: PV module parameters for one SIEMENS SP75 module                                                                 | .188  |

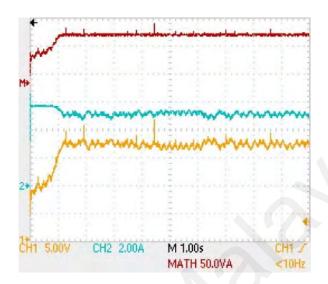

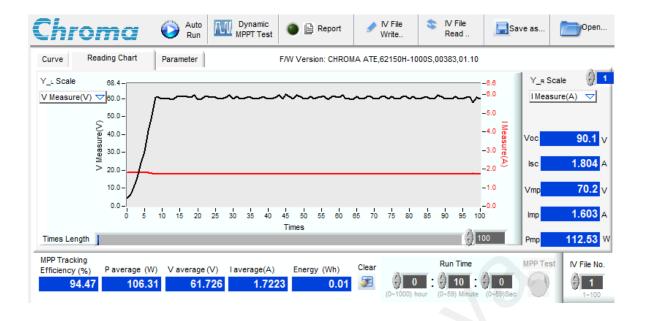

| Figure 5.31: mINC MPPT efficiency for one cascade in the PV system at 300 Wirradiance                                         |       |

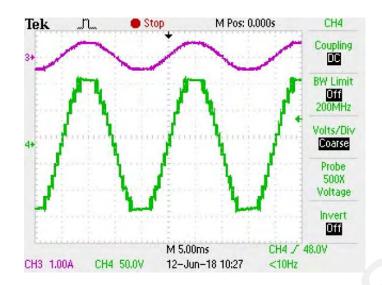

| Figure 5.32: Output-Voltage and Current for $Vinv < Vg$                                                                       | .190  |

| Figure 5.33: Output-Voltage and Current for $Vinv > Vg$                                                                       | .190  |

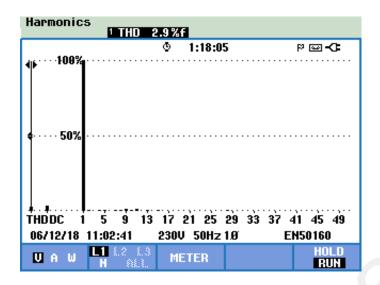

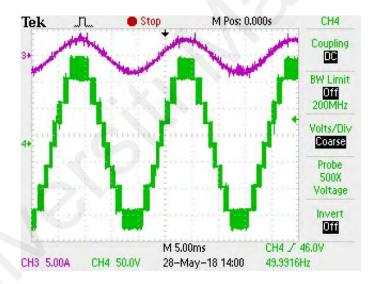

| Figure 5.34: Output-Voltage THD being 3.0 %                                                                                   | 191   |

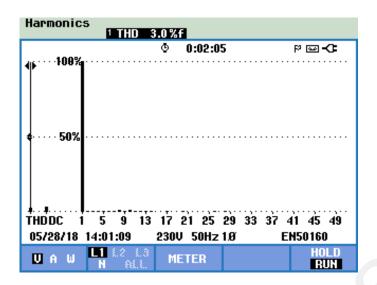

| Figure 5.35: Output-Current THD being 4.0 %                                                                                   | .191  |

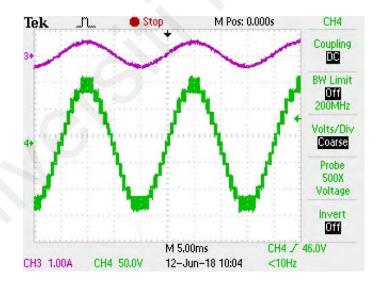

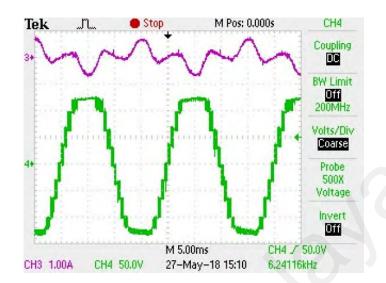

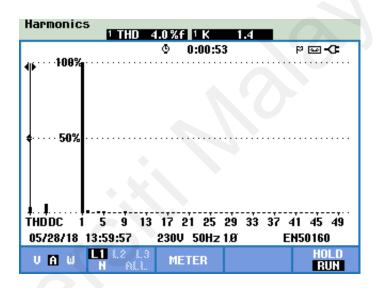

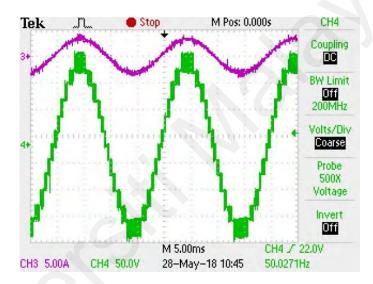

| Figure 5.36: Thirteen-level Unbalance                                                                                         | .192  |

| Figure 5.37: FFT of Output-Voltage for Unbalance condition                                                                    | .192  |

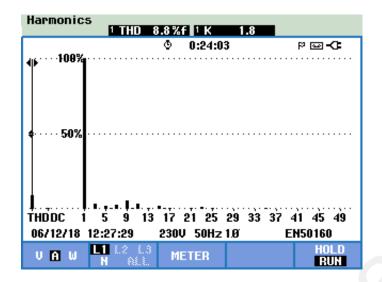

| Figure 5.38: Output-Current THD being 8.8 %                                                                                   | .193  |

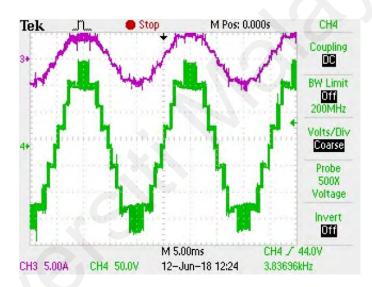

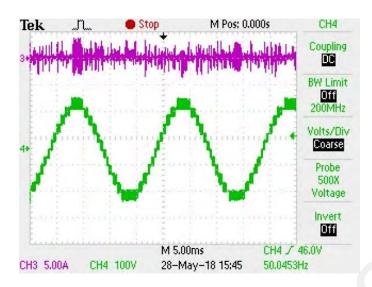

| Figure 5.39: Thirteen-level Balanced.                                                                                         | . 193 |

| Figure 5.40: FFT of Output-Voltage for Balanced condition          | 193 |

|--------------------------------------------------------------------|-----|

| Figure 5.41: Thirteen-level Balancing Current                      | 194 |

| Figure 5.42: FFT of Balancing Current                              | 194 |

| Figure 5.43: Output-Voltage and Current when $Vinv < Vg$           | 195 |

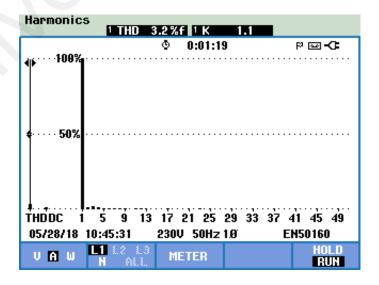

| Figure 5.44: Output-Voltage THD for Balanced Condition being 2.5 % | 195 |

| Figure 5.45: Output-Current THD for Balanced Condition being 3.2 % | 195 |

# LIST OF TABLES

| Table 2.1: Look-up table for rule base                                                                 |

|--------------------------------------------------------------------------------------------------------|

| Table 2.2: Anti-Islanding Standards                                                                    |

| Table 2.3: OVP/UVP and OFP/UFP allowed according to Malaysian Standard 59                              |

| Table 3.1: Input Capacitor Current, Linked with the Output Current, Against Switching States for TCHB  |

| Table 3.2: Range of Modulation Index and Phase Angle Displacement                                      |

| Table 3.3: Input Capacitor Current, Linked with the Output Current, Against Switching States for PiCHB |

| Table 4.1: THD Comparison of the proposed MLI                                                          |

| Table 4.2: System parameters for DC-DC Converters                                                      |

| Table 4.3: Parameters for Kyocera KC85T PV Panel                                                       |

| Table 4.4: Evaluation of mINC MPPT implemented on DC-DC Converters148                                  |

| Table 4.5: Characteristics of the PV module                                                            |

| Table 4.6: Characteristics of the five PV modules connected in series                                  |

| Table 4.7: System parameters for TCHB                                                                  |

| Table 4.8: Comparative analysis with RL load based on THD (%) and $\eta$ (%)                           |

| Table 4.9: System Parameters for PiCHB                                                                 |

### LIST OF SYMBOLS AND ABBREVIATIONS

# **Symbols**

A : Ampere

a : The number of cascades.

$\alpha$  : Weight factor

Ah : Ampere-hour

a : Ideality factor

b : Capacitors in each cascade

C : Capacity/Capacitance

*CF* : Cost function

$\Delta$  : Change

$D_{max}$ : Predefined maximum limit for the duty cycle

dI<sub>PV</sub> : Change of current

dD : Change in duty ratio

D : Duty Cycle

dP<sub>PV</sub> : Change in power

$dV_{PV}$  : Change of voltage

dP<sub>PV</sub>/dD : Change in power over change in duty ratio

dT: Temperature Change

dI<sub>PV</sub> : Change of current

dD : Change in duty ratio

e : Tolerance error

$E_g$ : Energy gap

G: Irradiance

$G_n$ : Nominal Irradiance

Hz : Hertz

$I_{pv,cell}$ : Current generated

$I_{o,cell}$ : Diode leakage current

$I_{MAX}$ : Maximum allowable current

$I_{pv}$  : Current produced by photons

I<sub>mpp</sub> : Current at MPP

I<sub>0</sub> : Reverse saturation current corresponding to the diode

I<sub>sh</sub> : Short circuit current

kW<sub>p</sub> : Kilowatt-peak

k : Boltzmann constant

$N_s$ : Number of cell in series

$N_p$ : Number of cell in parallel

$N_{level}$ : The number of output-voltage levels

$N_{IGBT}$ : Semiconductor switches employed

$N_{driver}$ : The number of gate drivers for the semiconductor switches

$\eta_{mppt}$ : MPPT efficiency

$P_{dc}(V_0)$ : Output power delivered

$P_{dc}(V_{mp})$ : Theoretical power at the MPP voltage

Q : Electron charge

R<sub>s</sub> : Series resistance

R<sub>sh</sub> : Shunt resistance

T : Temperature at p-n junction

$T_n$ : Nominal Temperature

$V_t$ : Thermal Voltage

$V_o$ : Output Voltage

$V_{in}$ : Input Voltage

$V_T$ : Thermal voltage of diode

$V_c$ : Voltage on each capacitor

$V_{stand}$ : Standing-Voltage on semiconductor switches

$V_{stand,i}$ : Total Standing-Voltage

V<sub>oc</sub> : Open circuit voltage

$W/m^2$ : Watt per meter square

### **Abbreviations**

AC Alternating Current

ACO : Ant Colony Optimization

ADC : Analog to Digital Converter

Ah : Ampere-hour

ANN : Artificial Neutral Network

BN : Bayesian Network

BNM : Brent Numerical Method

BS : Bidirectional Switch

BSs : Bidirectional Switches

BSM : Bisection Search Method

BVS : Balanced Voltage Sharing

CC : Constant Current

CHB : Cascaded H-Bridge

CNM : Classical Numerical Methods

CV : Constant Voltage

DC : Direct Current

DSP : Digital Signal Processor

EMC : Electromagnetic Compatibility

EMI : Electromagnetic Interference

FA : Firefly Algorithm

FC : Flying Capacitor

FL : Fuzzy Logic

FPGA : Field Programmable Gated Array

HC : Hill Climbing

HT : Hybrid Techniques

IGBT : Insulated Gate Bipolar Transistor

InC : Incremental Conductance

I-V : Current-Voltage

I2C : Inter-Integrated Circuit

LED : Light Emitting Diode

LVT : Lower Voltage Threshold

MLI : Multi-level Inverter

MPP : Maximum Power Point

mINC : Modified Incremental Conductance

MCNM : Modified Classical Numerical Methods

MBSM : Modified Bisection Search Method

MRFM : Modified Regula Falsi Method

MNRM : Modified Newton Raphson Method

MSM : Modified Secant Method

MBNM : Modified Brent Numerical Method

MOSFET : Metal-Oxide-Semiconductor Field-Effect Transistor

NN : Neural Network

NRM : Newton Raphson Method

NPC : Neutral-Point Clamped

OHESW : Optimized Harmonic Elimination Stepped Waveform

OCC : One-Cycle Control

OP : Operating Point

OVP : Over-Voltage Protection

OFP : Over-Frequency Protection

PiCHB :  $\pi$ -type Cascaded H-Bridge

PSO : Particle Swarm Optimization

PI : Proportional-Integral

PID : Proportional-Integral-Derivative

PV : Photovoltaic

PWM Pulse-Width Modulation

P&O : Perturb & Observe

P-V : Power-Voltage

PM : Predictor Method

PSO : Swarm Optimization

RCC : Ripple Correlation Control

RS Reduced Switch

RFM : Regula Falsi Method

SM : Secant Method

SMC : Slide Mode Control

SEPIC : Single Ended Primary Inductor Converter

STC : Standard Test Conditions

SVM : Space-Vector Modulation

TCHB : T-type Cascaded H-Bridge

THD : Total Harmonic Distortion

UVT : Upper Voltage Threshold

# LIST OF APPENDICES

| Appendix A:  | 2 | 1′ |

|--------------|---|----|

| ippendix 11. | _ | •  |

# **CHAPTER 1: INTRODUCTION**

## 1.1 Background

As technology rapidly develops, energy consumption across the globe is expected to increase and fossil energy is anticipated to be insufficient in the near future. This has called for an increase in extensive research on renewable energy these recent years (Chu & Majumdar, 2012). Solar energy, in particular, has received much attention because it is abundant, clean and reliable. According to (Kabir, Kumar, Kumar, Adelodun, & Kim, 2018), amongst the highest electricity generation in renewable energies field, solar energy yield is expected to grow continuously in near future.

Solar energy is clean and reliable. However, the PV array output is dependent on environmental variations. Therefore, harnessing maximum output from the solar PV array by MPPT techniques has been an advancing topic of research. A digital and analog classification of such techniques is presented in (A. Amir, Amir, Selvaraj, & Rahim, 2016). Most of these techniques are applicable to different PV systems. The PV system is classified into three types namely the grid-tied, stand-alone, and the hybrid PV system.

Figure 1.1: Block diagram for stand-alone PV system with battery pack

Stand-alone PV system uses solar energy as the only power source while grid-connected PV system and hybrid PV system use solar energy together with other types of energy. In remote and rural areas, standalone PV system is used where PV panels act as the only power source (Arricibita, Sanchis, González, & Marroyo, 2017). Figure 1.1

shows standard configuration of a stand-alone solar energy system consisting of an energy storage, charger controller and inverter.

By the application of a grid-tied PV system, power generated from the PV panels can be injected into the grid. In this configuration, PV panels act as a secondary power generator, which produce DC. However, before being fed to the grid, there remains a necessity for DC conversion into AC. Such systems can be used for residential (B. Liu et al., 2018), and industrial (Wu et al., 2017) applications.

Hybrid by definition is a combination of two different sources or methods, used together to achieve a common goal. Two or more sources of power merged together in a system to realize a hybrid power system in order to provide uninterrupted power supply to load (Halabi, Mekhilef, Olatomiwa, & Hazelton, 2017). A typical configuration of the hybrid battery-diesel generator system has been presented in Figure 1.2. The system also uses battery as energy storage to store excessive energy generated by PV panels.

Figure 1.2: Block diagram for hybrid PV system

Considerable focus remains on grid connected systems. As most electrical loads take AC, whereas PV energy is DC, so a power converter is required to convert the DC power produced from the PV panels into AC power for electrical loads, known as PV inverter.

PV inverter classification is based on its output voltage waveform type. There are square wave, quasi-square wave, quasi-sine (multilevel) wave, and sine wave, inverters.

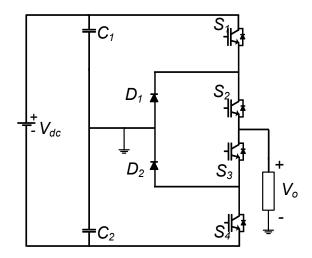

Most inverters for stand-alone PV systems are square wave, quasi square wave, or multilevel inverters (MLI) and use low frequency switching, whereas for grid-connected systems the inverters are sine wave or multilevel and use high frequency switching. Researchers have suggested various single-phase inverter topologies, yet the MLI acquire a prominent position (Malinowski, Gopakumar, Rodriguez, & Perez, 2010; Prabaharan & Palanisamy, 2017). Multilevel Stand-alone (Daher, Schmid, & Antunes, 2008) and Grid-tied inverters are favorable; as such topologies offer reduced standing voltages on the semiconductor devices, reduced switching losses, electromagnetic interference (EMI), filter size, better harmonic profile of output-current and voltage; resulting into a compact, economical and effective design (Prabaharan & Palanisamy, 2017). Considering the fundamental structure, MLI have been classified into three assemblies. Neutral-Point Clamped (NPC) (Busquets-Monge, Filba-Martinez, Alepuz, & Calle-Prado, 2017), flying capacitor (FC) or multicell (Farivar, Ghias, Hredzak, Pou, & Agelidis, 2017), and cascaded H-bridge (CHB) (Fuentes et al., 2017).

Owing to its structural requirements, the capacitor voltage balancing in the FC remains complex as it needs a higher amount capacitors for increased levels of the output voltage. Moreover, for synthesizing higher output-voltage levels, NPC requires a greater amount of clamping diodes. In addition, the balanced voltage at the input capacitors remains a shortcoming of the NPC. In contrast, CHB converters offer a nominal standing voltage, quality output and simpler DC-link voltage balancing. Considering symmetric CHB converters, balanced DC-link voltage sharing is required. As unbalanced state of operation can increase voltage stress on the switches damaging the entire system.

Improving quality of electricity to be injected into the grid requires the improvement in Total Harmonic Distortion (THD) for the output-voltage and current of the inverter.

Reduced THD is acquired by increasing the levels produced by the inverter at the output

for voltage. As, increased EMI, THD and switching losses offered by three-level inverter make it less effective for Grid-Integration. Therefore, to reduce the switching losses, THD and EMI, MLI design configuration has been employed with a stand-alone and grid-tied PV system.

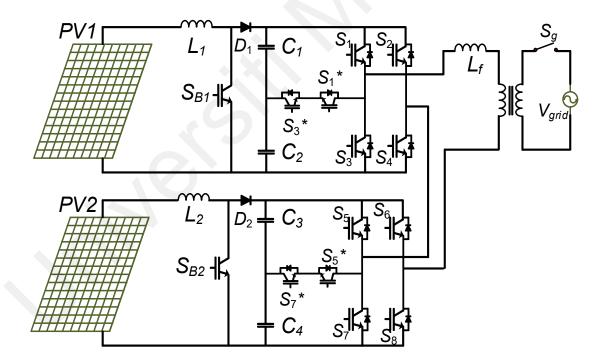

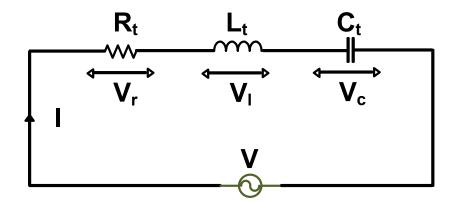

In this thesis, the development of a symmetric cascaded H-bridge single-phase MLI has been recounted with T and  $\pi$ -type bidirectional switches providing the TCHB and PiCHB topologies, respectively. These topological designs with high frequency switching were applied to a grid-tied PV system. Here, a self-voltage balancing PWM scheme has been provided for the TCHB topology and a passive balancing circuit comprised of an RLC branch had been utilized for the balanced voltage sharing (BVS) of the DC-link capacitors for the PiCHB design. Moreover, algorithms for MPPT based on mINC algorithm, linear current control based on a PI controller, and anti-islanding protection were also developed utilizing a TMS320F28335 DSP board.

# 1.2 Research Questions

Study of the grid-tied PV inverters and how they are beneficial, sparked interest for the following research questions:

- i. Why is solar energy one of the best renewable energy options to tackle increasing energy demands?

- ii. How to improve the Maximum Power Point Tracking technique to harness photovoltaic energy?

- iii. What improvements can be made to the conventional PV inverters in terms of AC waveform quality, number of devices, number of switches, number of gate drivers, power losses, standing voltages and cost function?

- iv. What is the necessity of an improved grid-tied PV system?

### 1.3 Research Objectives

Research objectives of this thesis are listed as follows:

- 1. To develop novel TCHB and PiCHB grid-connected PV inverters with PWM control schemes utilizing eight and twelve identical reference signals.

- To compare the proposed TCHB and PiCHB configuration against various symmetric cascaded MLI topologies.

- To verify and validate the self-balancing PWM scheme for the TCHB MLI topology and passive balancing circuit for PiCHB.

- 4. To simulate and develop a hardware prototype implementing the proposed PWM switching scheme for the TCHB and PiCHB grid-connected MLI.

- 5. To develop a control system for grid-connection employing algorithms for MPPT based on mINC, PI-based current control and anti-islanding protection.

# 1.4 Overview of the Chapters

This thesis is written in six chapters and each chapter can be briefly explained as follows:

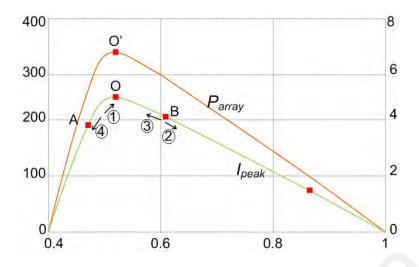

Chapter 2: An overview of the solar energy system has been presented in this chapter. First, the fundamentals of PV panel characteristics, under various ambient irradiance levels and changing temperatures, are focused. In addition, theoretical analysis of the current-voltage (I-V) and power-voltage (P-V) graphical plots has been provided, followed by a comprehensive review on several analog and digital MPPT techniques employed for PV systems. Second, the chapter presents a novel mINC MPPT technique and compares its effective performance with the conventional MPPT techniques. Further, various single-phase inverter topologies have been surveyed, particularly focusing MLI design topologies. Here, different modulation schemes of operation and current-control techniques, feeding power to the grid, have also been explored.

Chapter 3: describes the proposed configuration for the single-phase TCHB nine-level and PiCHB thirteen-level inverters with capacitor voltage balancing. A comparative analysis has been presented of the proposed inverter topologies against various symmetric CHB topologies. Further, the chapter details the inverter operating principles, design considerations, proposed PWM schemes and offers theoretical analysis to validate the requirement of balanced voltage sharing at the DC-Link capacitors to attain a better harmonic profile for the output-voltage and current for grid-connection.

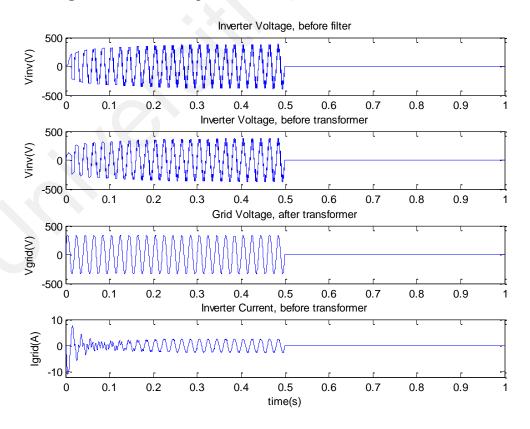

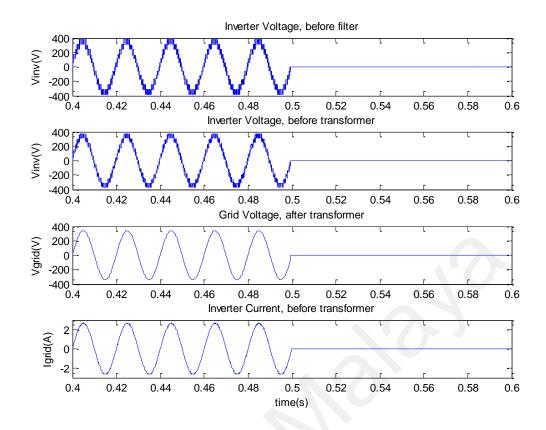

**Chapter 4:** Simulation results for the proposed TCHB and PiCHB inverters for low switching frequency, high switching frequency, and the PV application have been presented in this chapter. This chapter also recounts simulation of the current-voltage (I-V) and power-voltage (P-V) curves under varying environmental conditions.

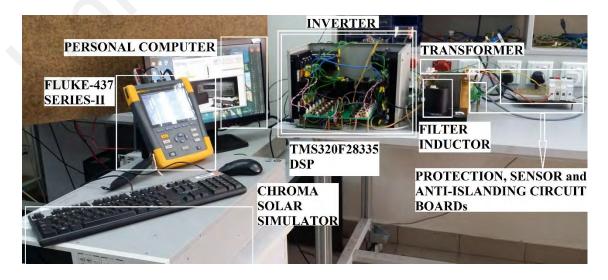

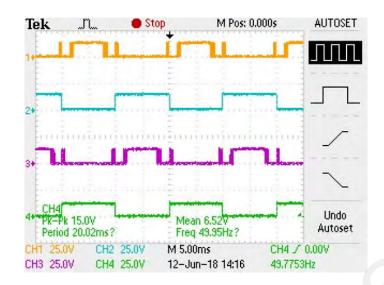

**Chapter 5:** presents the hardware implementation, which comprises of hardware configuration, experimental results for high switching frequency, for the TCHB PWM scheme, PiCHB PWM scheme, operation of the passive balancing circuit for balanced voltage sharing and the PV application. Results for both stand-alone and grid-connected PV application with the proposed control algorithms implemented on DSP TMS320F28335 have been displayed.

**Chapter 6:** concludes with a summary, a listing of the author's contributions, and recommendations for possible future work.

#### **CHAPTER 2: OVERVIEW OF SOLAR ENERGY SYSTEM**

#### 2.1 Introduction