## DESIGN OF ULTRA LOW VOLTAGE, HIGH EFFICIENCY CMOS RADIO FREQUENCY ENERGY HARVESTING SYSTEM

YONG JACK KEE

## FACULTY OF ENGINEERING UNIVERSITI MALAYA KUALA LUMPUR

2024

# DESIGN OF ULTRA LOW VOLTAGE, HIGH EFFICIENCY CMOS RADIO FREQUENCY ENERGY HARVESTING SYSTEM

YONG JACK KEE

# THESIS SUBMITTED IN FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

FACULTY OF ENGINEERING UNIVERSITI MALAYA KUALA LUMPUR

2024

## UNIVERSITI MALAYA ORIGINAL LITERARY WORK DECLARATION

Name of Candidate: YONG JACK KEE

Matric No: S2028558/1

Name of Degree: **Doctor of Philosophy**

Title of Project Paper/Research Report/Dissertation/Thesis ("this Work"):

Design Of Ultra Low Voltage, High Efficiency CMOS Radio Frequency

**Energy Harvesting System**

Field of Study: Electronics (Engineering & Engineering Trades)

I do solemnly and sincerely declare that:

- (1) I am the sole author/writer of this Work;

- (2) This Work is original;

- (3) Any use of any work in which copyright exists was done by way of fair dealing and for permitted purposes and any excerpt or extract from, or reference to or reproduction of any copyright work has been disclosed expressly and sufficiently and the title of the Work and its authorship have been acknowledged in this Work;

- (4) I do not have any actual knowledge nor do I ought reasonably to know that the making of this work constitutes an infringement of any copyright work;

- (5) I hereby assign all and every rights in the copyright to this Work to the Universiti Malaya ("UM"), who henceforth shall be owner of the copyright in this Work and that any reproduction or use in any form or by any means whatsoever is prohibited without the written consent of UM having been first had and obtained;

- (6) I am fully aware that if in the course of making this Work I have infringed any copyright whether intentionally or otherwise, I may be subject to legal action or any other action as may be determined by UM.

Candidate's Signature

Date: 23 June 2024

Subscribed and solemnly declared before,

Witness's Signature

Date: 25 June 2024

Name:

Designation:

# DESIGN OF ULTRA LOW VOLTAGE, HIGH EFFICIENCY CMOS RADIO FREQUENCY ENERGY HARVESTING SYSTEM

#### ABSTRACT

Wireless Sensor Networks (WSNs) have emerged as a pivotal technology for various IoT applications, driven by advancements in 5G (5th Generation) technology and cloud computing. For stable and continuous operation, Radio Frequency Energy Harvesting (RFEH) is considered an optimal energy source for WSNs to achieve self-power capabilities, alleviating the need for a battery. The rectifier and charge pump (CP) plays a crucial role within the Radio Frequency Energy Harvesting (RFEH) system. However, the performance is significantly impacted by high conduction and reversion loss in subthreshold operation. Despite the existence of dynamic gate biasing (DGB) techniques that aim to mitigate both conduction and reversion losses, these losses cannot be entirely eliminated, resulting in the low performance of the rectifier and CP circuit. Furthermore, the broad range of scavenged input power from the RFEH system can result in elevated output voltage levels that may pose a risk of damaging the WSN load. This thesis presents a comprehensive review of recent rectifier and CP improvement techniques and provides a thorough analysis of the characteristics of the state-of-the-art rectifier and CP circuit. By considering the trade-offs, several enhancements are proposed to optimize these components specifically for subthreshold operation, aiming to improve its power conversion efficiency (PCE). This work proposes a novel advance dynamic gate-biasing technique that focuses on reducing forward conduction loss and reverse current leakage loss in the rectifier and CP. Specifically, the advanced DGB is combined with an NMOS-PMOS dual-switch transistor pair which acts as a secondary switch to further reduce the losses. By implementing this combination, the proposed architecture achieved an ultralow-voltage input (0.1 V) subthreshold operation CP with a PCE of 43.4 %. Additionally, a novel reconfigurable series-parallel CP employing a dynamic source-fed oscillator with 62 % PCE is introduced. Finally, an integrated RFEH featuring a low-power voltage monitoring unit with 3.3 V bounded output cater is designed to cater to WSN applications. The research contributes to the understanding and advancement of rectifiers and CPs, and the design of a fully integrated RFEH system, enabling more efficient energy utilization in WSNs.

**Keywords:** radio frequency energy harvesting, CMOS charge pump, DC-DC converter, power conversion efficiency, subthreshold operation

# REKA BENTUK SISTEM PENUAIAN TENAGA RADIO CMOS VOLTAN ULTRA RENDAH DAN KECEKAPAN TINGGI

#### ABSTRAK

Rangkaian Penderia Tanpa Wayar (WSN) telah muncul sebagai teknologi penting untuk pelbagai aplikasi IoT, didorong oleh kemajuan dalam teknologi 5G (Generasi Ke-5) dan pengkomputeran awan. Untuk operasi yang stabil dan berterusan, Penuaian Tenaga Frekuensi Radio (RFEH) dianggap sebagai sumber tenaga optimum untuk WSN untuk mencapai keupayaan kuasa diri, mengurangkan keperluan untuk bateri. Pam penerus dan pengecas (CP) memainkan peranan penting dalam sistem Penuaian Tenaga Frekuensi Radio (RFEH). Walau bagaimanapun, prestasi terjejas dengan ketara oleh kehilangan pengaliran dan pengembalian yang tinggi dalam operasi subambang. Walaupun wujudnya teknik pincang get dinamik (DGB) yang bertujuan untuk mengurangkan kedua-dua kehilangan pengaliran dan penbalikan, kerugian ini tidak dapat dihapuskan sepenuhnya, mengakibatkan prestasi rendah penerus dan litar CP. Tambahan pula, julat luas kuasa input terkumpul daripada sistem RFEH boleh mengakibatkan paras voltan keluaran tinggi yang mungkin menimbulkan risiko merosakkan beban WSN. Tesis ini membentangkan ulasan komprehensif mengenai teknik penerus dan penambahbaikan CP terkini dan menyediakan analisis menyeluruh tentang ciri-ciri penerus terkini dan litar CP. Dengan peningkatan mempertimbangkan pertukaran, beberapa dicadangkan untuk mengoptimumkan komponen ini khusus untuk operasi subambang, bertujuan untuk meningkatkan kecekapan penukaran kuasa (PCE). Kerja ini mencadangkan teknik pincang pintu dinamik maju baru yang memfokuskan pada mengurangkan kehilangan pengaliran hadapan dan kehilangan kebocoran arus songsang dalam penerus dan CP. Khususnya, DGB pendahuluan digabungkan dengan pasangan transistor dwi-suis NMOS-PMOS yang bertindak sebagai suis sekunder untuk mengurangkan lagi kerugian. Dengan melaksanakan gabungan ini, seni bina yang dicadangkan mencapai CP operasi subambang input ultra-rendah (0.1 V) dengan PCE sebanyak 43.4 %. Selain itu, CP selari siri yang boleh dikonfigurasikan semula menggunakan pengayun disuap sumber dinamik dengan 62 % PCE diperkenalkan. Akhir sekali, RFEH bersepadu yang menampilkan unit pemantauan voltan kuasa rendah dengan kater keluaran sempadan 3.3 V direka bentuk untuk memenuhi aplikasi WSN. Penyelidikan ini menyumbang kepada pemahaman dan kemajuan penerus dan CP, dan reka bentuk sistem RFEH bersepadu sepenuhnya, membolehkan penggunaan tenaga yang lebih cekap dalam WSNs.

Kata Kunci: penuaian tenaga frekuensi radio, pam caj CMOS, penukar DC-DC,

kecekapan penukaran kuasa, operasi subambang

#### ACKNOWLEDGEMENTS

I would like to express my heartfelt gratitude to my supervisor, Prof. Ir. Dr. Harikrishnan Ramiah, for his unwavering guidance, support, and invaluable insights throughout my research journey. I am also grateful for the autonomy and flexibility provided during the research process. Your dedication and expertise have been instrumental in shaping this work.

I am also deeply thankful to my co-supervisor, Prof. Dr. Saad Mekhilef, for his valuable contributions and constructive feedback, which have greatly enriched the quality of this research.

I extend my appreciation to my senior colleagues, Dr. Kishore Kumar and Dr. Gabriel Chong, for their mentorship and for sharing their knowledge, which significantly contributed to the success of this project.

I would also like to thank all my lab mates for their camaraderie, collaborative spirit, and countless discussions that have made our research environment both productive and enjoyable.

This work would not have been possible without the collective efforts and support of my academic family. Thank you all for being a crucial part of this journey.

## TABLE OF CONTENTS

| ABSTRACT                                | iii        |

|-----------------------------------------|------------|

| ABSTRAK                                 | v          |

| ACKNOWLEDGEMENTS                        | vii        |

| TABLE OF CONTENTS                       | viii       |

| LIST OF FIGURES                         | xi         |

| LIST OF TABLES                          | xvi        |

| LIST OF SYMBOLS AND ABBREVIATIONS       | xvii       |

| CHAPTER 1 : INTRODUCTION                | 1          |

| 1.1 Background Study and Motivation     | 1          |

| 1.2 Problem Statement                   |            |

| 1.3 Research Objectives                 | 6          |

| 1.4 Research Methodology                | 7          |

| 1.5 Contributions of the Research Work  | 9          |

| 1.6 Scope of Work                       | 10         |

| 1.7 Thesis Outline                      | 10         |

| CHAPTER 2 : LITERATURE REVIEW           | 12         |

| 2.1 Chapter Overview                    | 12         |

| 2.2 RF Energy                           | 12         |

| 2.2.1 Background                        | 12         |

| 2.2.2 RF Availability                   | 13         |

| 2.3 RFEH Circuit                        | 15         |

| 2.3.1 RFEH Front-End Circuit            | 15         |

| 2.3.2 RFEH Back-End Circuit             |            |

| 2.3.3 Performance Evaluation Parameters |            |

| 2.3.4 Subthreshold Operation            | 21<br>viii |

| 2.3.5 Types of Power Losses in Rectifier and CP                        | 21      |

|------------------------------------------------------------------------|---------|

| 2.4 Conventional Rectifier and CP Topologies                           | 23      |

| 2.5 Rectifier and CP Topologies Improvement Method                     |         |

| 2.5.1 Gate Biasing Technique                                           | 28      |

| 2.5.2 Gate Boosting Technique                                          | 32      |

| 2.5.3 Dynamic Gate Biasing Technique                                   | 35      |

| 2.5.4 Bulk Biasing Technique                                           | 37      |

| 2.5.5 Parallel Architecture                                            |         |

| 2.5.6 Clock Boosting Technique                                         |         |

| 2.5.7 Adiabatic Clock Scheme                                           | 41      |

| 2.6 Comparative Recent Research Evaluation of Low Input Voltage Charge | Pumps42 |

| 2.7 Effect of Fluctuating Input Power on RFEH System                   | 43      |

| 2.7.1 Conventional Reconfigurable CP                                   | 47      |

| 2.7.2 Frequency Modulation                                             | 48      |

| 2.7.3 Output Voltage Monitoring                                        | 50      |

| 2.8 Summary                                                            | 51      |

| CHAPTER 3 : ADVANCED DYNAMIC GATE BIASING                              |         |

| 3.1 Chapter Overview                                                   | 53      |

| 3.2 Proposed Subthreshold Operation Charge Pump                        | 53      |

| 3.2.1 Related Work on Dynamic Gate Biasing                             | 53      |

| 3.2.2 Proposed CP circuit                                              | 58      |

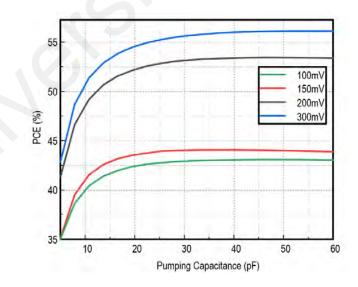

| 3.3 Capacitance Optimization                                           | 61      |

| 3.3.1 Effect of Pumping Capacitance on Charge Pump                     | 61      |

| 3.4 Experimental Set Up and Result                                     | 67      |

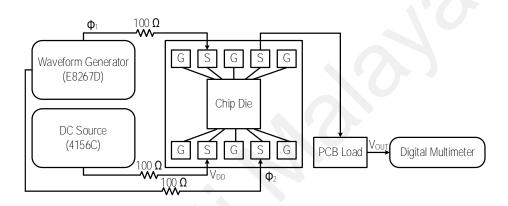

| 3.4.1 Experimental and Measurement Set Up                              | 67      |

| 3.4.2 Experimental Results                                             | 69      |

| 3.5 Discussion                                                         | 72      |

| 3.6 Summary                                            | 75  |

|--------------------------------------------------------|-----|

| CHAPTER 4 : RECONFIGURABLE SERIES-PARALLEL CHARGE PUMI | •77 |

| 4.1 Chapter Overview                                   | 77  |

| 4.2 Proposed Reconfigurable Charge Pump                | 77  |

| 4.2.1 CP Reconfiguration Concept                       | 77  |

| 4.2.2 Proposed Series-Parallel Reconfigurable CP       | 78  |

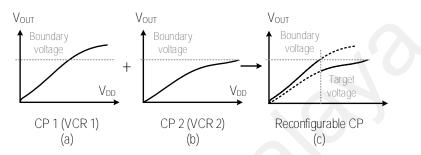

| 4.2.4 Logic Control Unit                               | 81  |

| 4.2.5 Dynamic Source-Fed Oscillator                    | 83  |

| 4.3 Experimental Result                                | 86  |

| 4.4 Discussion                                         | 91  |

| 4.5 Summary                                            | 93  |

| CHAPTER 5 : FULLY INTEGRATED CMOS AMBIENT RFEH SYSTEM  | 95  |

| 5.1 Chapter Overview                                   | 95  |

| 5.2 Proposed RFEH System with Output Voltage Limiter   | 95  |

| 5.2.1 RF-DC Rectifier                                  | 96  |

| 5.2.2 Voltage Monitor                                  | 97  |

| 5.3 Experimental Result                                | 106 |

| 5.4 Discussion                                         | 112 |

| 5.5 Summary                                            | 113 |

| CHAPTER 6 : CONCLUSION                                 | 114 |

| 6.1 Conclusion                                         | 114 |

| 6.2 Future Work                                        | 116 |

| REFERENCES                                             | 118 |

|                                                        |     |

## **LIST OF FIGURES**

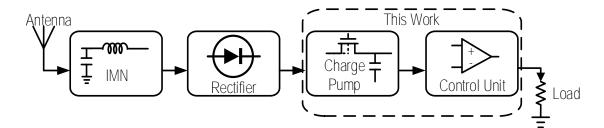

| Figure 1.1: General System Diagram of an RF-Based Energy Harvesting System5                       |

|---------------------------------------------------------------------------------------------------|

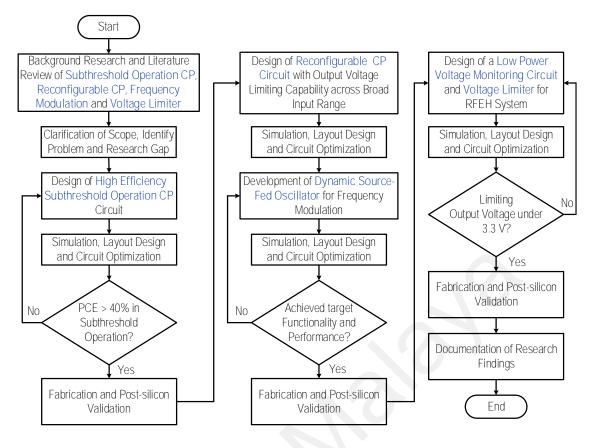

| Figure 1.2: Research Methodology Flow Chart                                                       |

| Figure 2.1: Block Diagram of an RF-DC Energy Harvester15                                          |

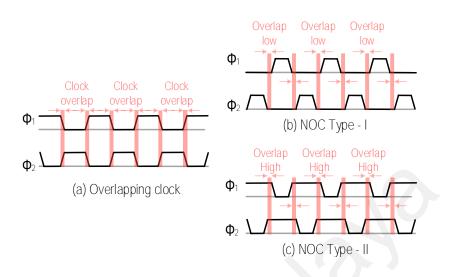

| Figure 2.2: Different Types of Complementary Clock Signals for CP Operation (a)                   |

| Conventional Overlapping Clock Scheme (b) Non-Overlap Type-I Clock Scheme (c)                     |

| Non-Overlap Type-II Clock Scheme                                                                  |

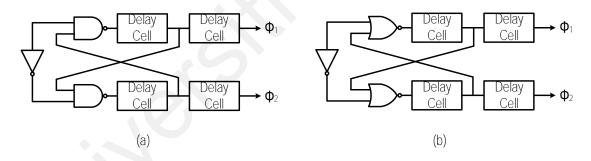

| Figure 2.3: Schematic Block Diagram of Non-Overlap Clock Generator using (a)                      |

| NAND Gates and (b) NOR gate                                                                       |

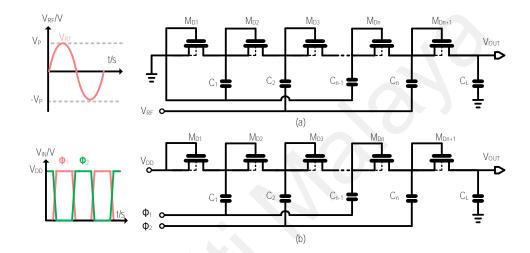

| Figure 2.4: Conventional Dickson Topology of (a) Rectifier and (b) Charge Pump24                  |

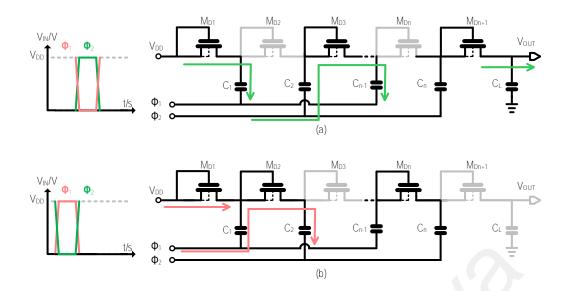

| Figure 2.5: The Operation of Dickson CP at (a) The Second-Half Clock Cycle and (b)                |

| the First-Half Clock Cycle                                                                        |

| Figure 2.6: Conventional Cross-Coupled Topology of (a) Rectifier and (b) Charge                   |

| Pump                                                                                              |

| Figure 2.7: The Operation of Cross-coupled CP at (a) The Second-Half Clock Cycle and              |

| (b) The First-Half Clock Cycle                                                                    |

| Figure 2.8: Floating Gate Threshold Voltage Compensation Technique (Le et al., 2008)              |

|                                                                                                   |

| Figure 2.9: A Bootstrap CP's (a) Schematic Diagram (b) Conventional Clock Scheme                  |

| (c) Gate-Boosted Clock Scheme (Fuketa et al., 2017)                                               |

| Figure 2.10: A Schematic Diagram of the $V_{\text{TH}}$ Cancellation Unit (Umeda et al., 2006) 30 |

| Figure 2.11: Self-Bias Technique with (a) Forward-Compensation using NMOS (b)                     |

| Back-Compensation using PMOS (Hameed & Moez, 2013)                                                |

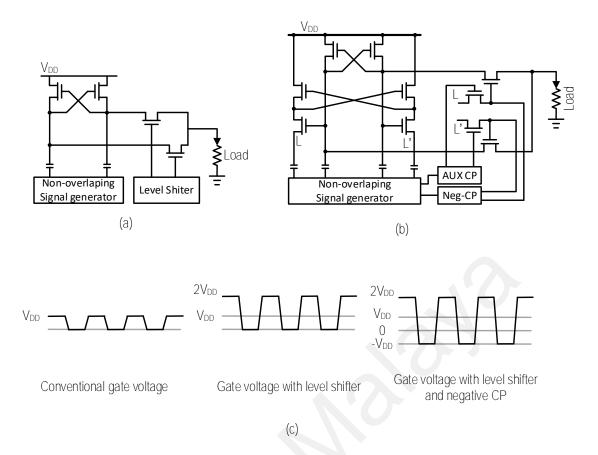

| Figure 2.12: Schematic of a Voltage Doubler with (a) Level Shifter (b) Level Shifter |

|--------------------------------------------------------------------------------------|

| and a Negative CP and (c) Different Gate Voltage Signals for the Charge Transferring |

| Transistor                                                                           |

| Figure 2.13: The Schematic of (a) Level-Shifter for the NMOS and PMOS in CCCP and    |

| (b) its Equivalent Block Diagram                                                     |

| Figure 2.14: Conventional Dynamic Gate Biasing Technique on CTS CP (Chi-Chang &      |

| Jiin-Chuan, 1997)                                                                    |

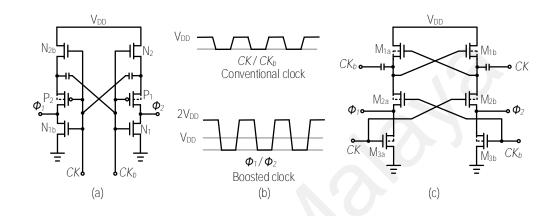

| Figure 2.15: Clock Booster: (a) Conventional Circuit Schematic (b) Conventional and  |

| Boosted Clock Amplitude (c) All-NMOS Configuration                                   |

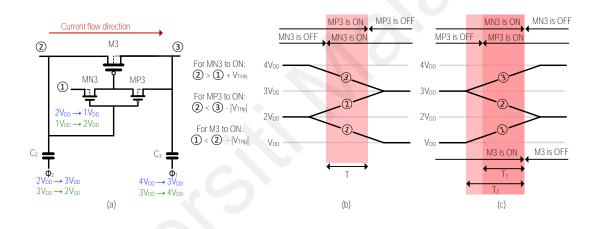

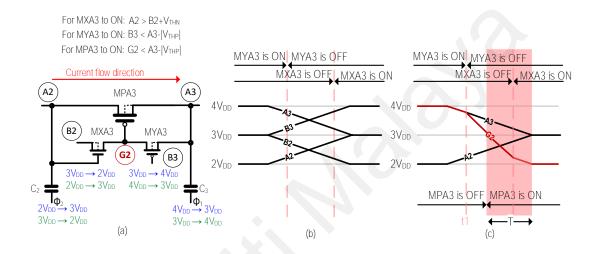

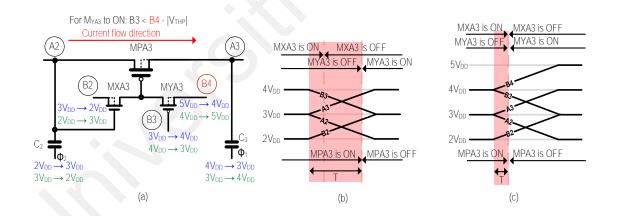

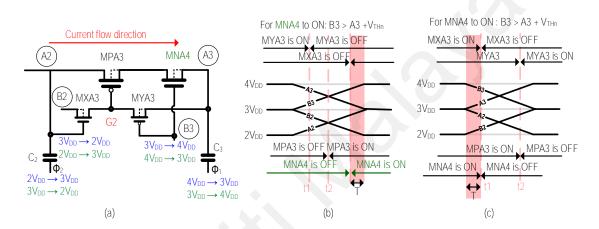

| Figure 3.1: The Third Stage of a Conventional DGB's (a) Node Voltage Behavior and    |

| its Switching Waveforms at (b) Forward Conduction Phase (c) Reverse Conduction       |

| Phase                                                                                |

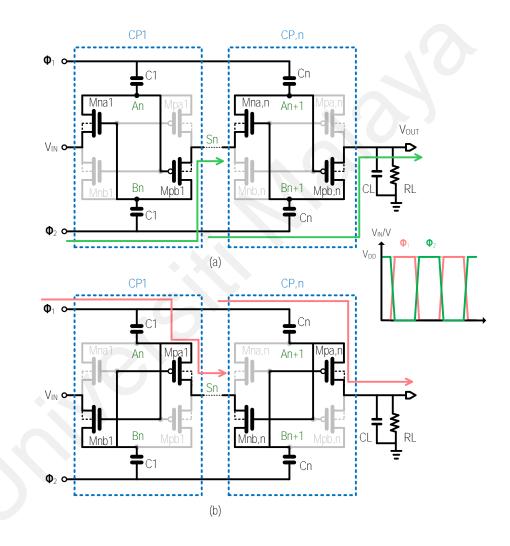

| Figure 3.2: Dual branch CP employing advanced dynamic gate biasing technique (Jiang  |

| et al., 2018)55                                                                      |

| Figure 3.3: Forward Conduction Phase of the Third Stage of Advanced DGB CP-1's (a)   |

| Node Voltage Behavior (b) Switching Waveforms (c) Switching Waveform of MPA3's       |

| Gate Terminal                                                                        |

| Figure 3.4: The Improved Advance DGB's (a) Schematic Diagram of CP-2's (b)           |

| Switching Waveform of CP-1 (c) Switching Waveform of CP-257                          |

| Figure 3.5: Proposed 3-stage CCCP Topology with Advanced DGB                         |

| Figure 3.6: The Third Stage Proposed CP's (a) Schematic Representation (b) Switching |

| Waveform During Forward Conduction Phase (c) Switching Waveform During Reverse       |

| Conduction Phase60                                                                   |

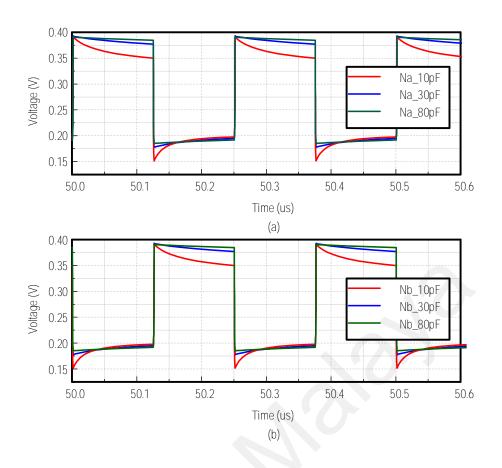

| Figure 3.7: Node Voltage of CCCP at (a) First Pumping Branch (CLK) (b) Second        |

| Pumping Branch (CLKB) with Different Pumping Capacitance                             |

| Figure 3.8: PCE of Single-Stage CCCP with Different Pumping Capacitance at              |

|-----------------------------------------------------------------------------------------|

| Different Input Voltage Levels                                                          |

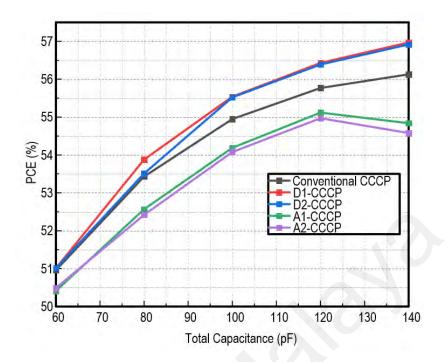

| Figure 3.9: PCE of Different Capacitor Size Combinations                                |

| Figure 3.10: Schematic of the Measurement Set Up for the Proposed CP68                  |

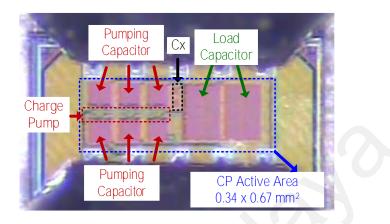

| Figure 3.11: Chip Micrograph of the Fabricated Charge Pump Circuit                      |

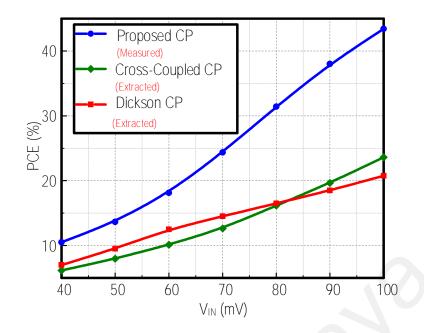

| Figure 3.12: The Measured Power Conversion Efficiency of the Proposed CP Across         |

| Input Voltage Under 150 kΩ Load Condition70                                             |

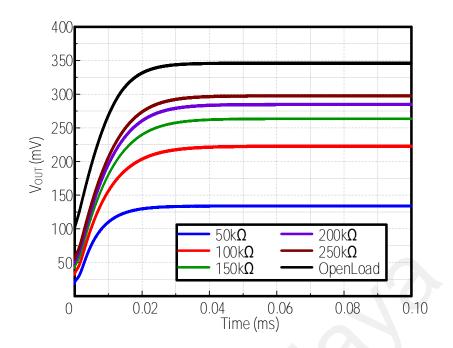

| Figure 3.13: Transient Behaviour of Proposed CP Under Various Load Conditions at        |

| $V_{\rm IN} = 0.1 \ {\rm V}.$                                                           |

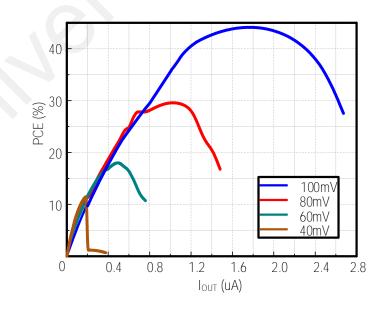

| Figure 3.14: The Plot of Measured Power Conversion Efficiency Versus Output Current     |

| of the Proposed Charge Pump71                                                           |

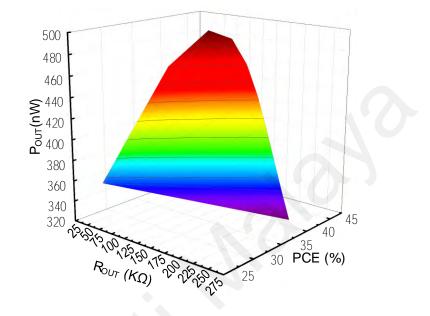

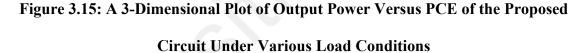

| Figure 3.15: A 3-Dimensional Plot of Output Power Versus PCE of the Proposed            |

| Circuit Under Various Load Conditions                                                   |

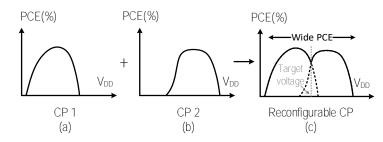

| Figure 4.1: The PCE vs Input Voltage Curve of (a) Individual CP1 (b) Individual CP2     |

| (c) Reconfigurable CP by Combining CP1 and CP278                                        |

| Figure 4.2: The Output Voltage of (a) Individual CP1 (b) Individual CP2 (c)             |

| Reconfigurable CP by Combining CP1 and CP278                                            |

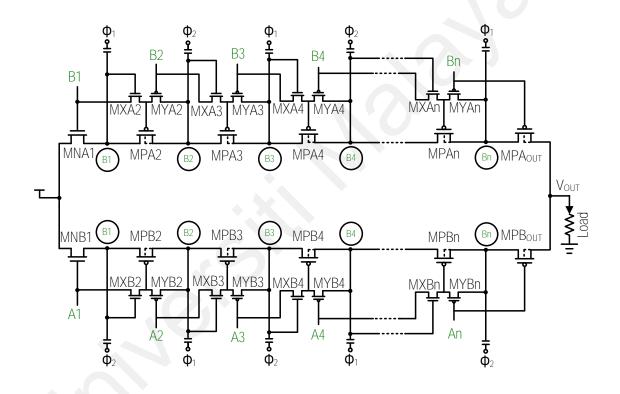

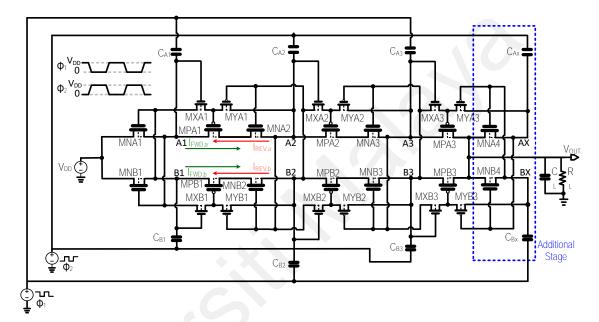

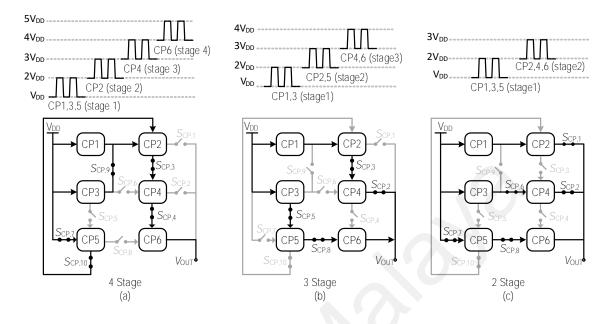

| Figure 4.3: Top Architecture of the Proposed Series-Parallel Reconfigurable CP79        |

| Figure 4.4: Proposed Reconfigurable CP (a) Scenario I, 4 Stages (b) Scenario II, 3      |

| Stages (c) Scenario III, 2 Stages                                                       |

| Figure 4.5: Proposed Oscillator's Voltage Controller Unit: (a) Schematic Diagram (b)    |

| Equivalent Resistant Model (c) Block Diagram of a Non-Overlap Clock Generator. The      |

| Size of the Inverters Represents the Transistors' Width                                 |

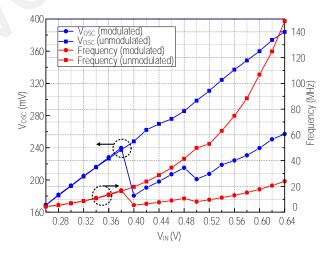

| Figure 4.6: Plots of the Relationship Between Input Voltage, Oscillator Source Voltage, |

| and the Modulated and Unmodulated Oscillating Frequencies                               |

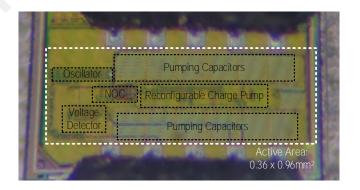

| Figure 4.7: Photomicrograph of the Proposed Reconfigurable CP                           |

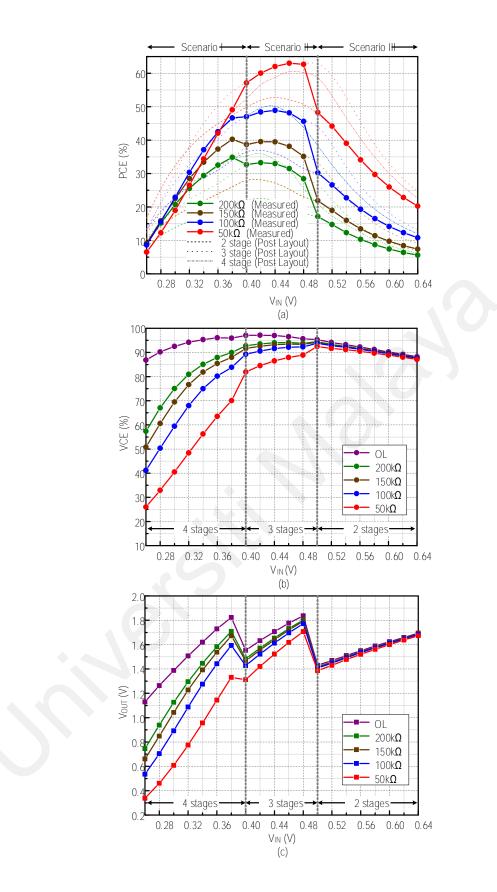

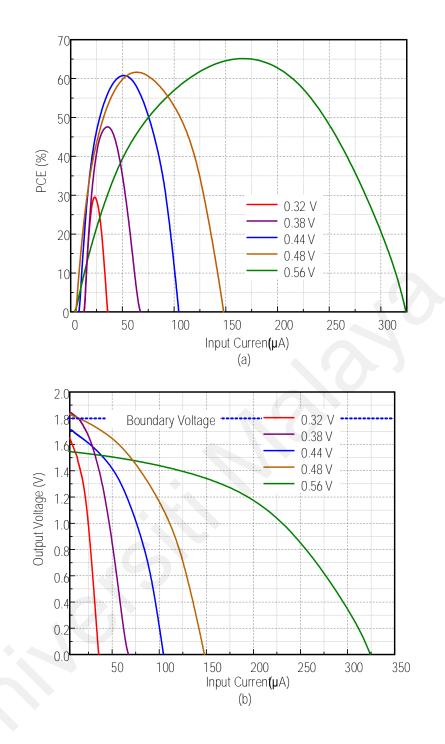

| Figure 4.8: Measured Performance of (a) PCE vs $V_{IN}$ (b) VCE vs                     |

|----------------------------------------------------------------------------------------|

| Figure 4.9: (a) Graph of PCE vs Input Current (b) Graph of Output Voltage vs Input     |

| Current at Various Input Voltage Under 100 kΩ Condition                                |

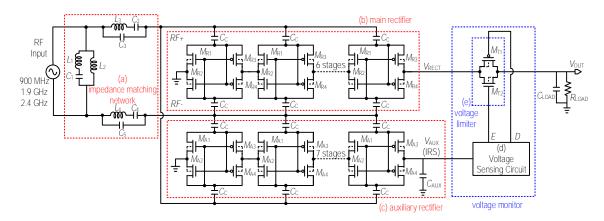

| Figure 5.1: The Schematic of RF-DC Energy Harvesting Circuit with Output Limiting      |

| Capabilities: (a) IMN (b) Main Rectifier (c) Auxiliary Rectifier (d) Voltage Sensing   |

| Circuit (e) Voltage Limiter                                                            |

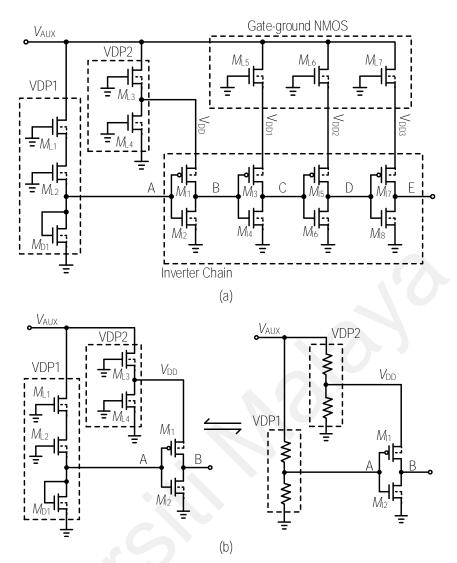

| Figure 5.2: The Schematic Diagram of (a) The Proposed Voltage Sensing Circuit. (b)     |

| The Voltage Divider Path for the CMOS Inverter Voltage Sensing Unit and its            |

| Equivalent Resistance Ratio Model                                                      |

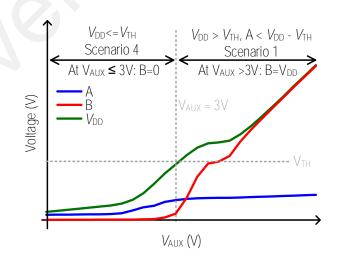

| Figure 5.3: The Two-Operating Region of a CMOS Inverter Voltage Sensing Unit           |

| (Scenario 1 and 4) with Voltage Divider Paths Detecting a Target Voltage of 3 V 100    |

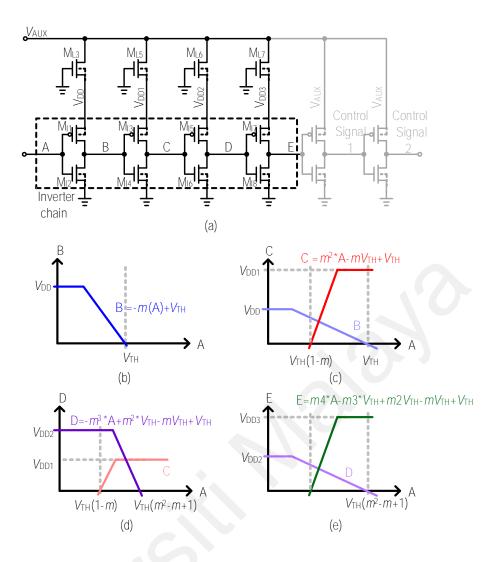

| Figure 5.4: Inverter Chain's (a) Schematic Diagram and the Output Hysteresis of (b)    |

| First Inverter (c) Second Inverter (d) Third Inverter (e) Fourth Inverter102           |

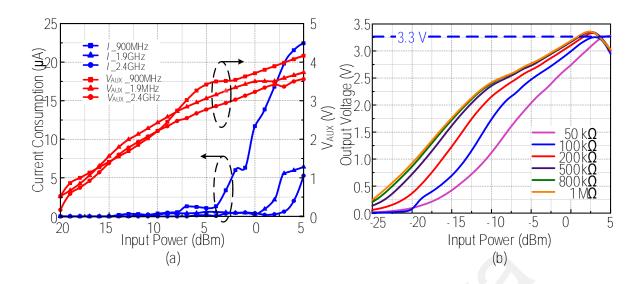

| Figure 5.5: Graph of (a) Current Consumption of the Proposed Low Power Voltage         |

| Sensing Circuit under Different Voltages (b) Output Voltage of the Proposed Circuit    |

| under Various Load Conditions at 2.4 GHz104                                            |

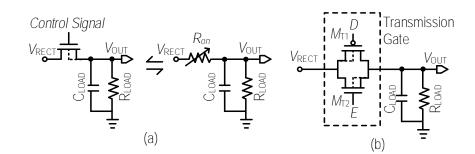

| Figure 5.6: The Schematic of a Switch-Resistance Modulation Technique using (a) a      |

| Pass Transistor and its Equivalent Variable Resistor Model and (b) Transmission Gate.  |

|                                                                                        |

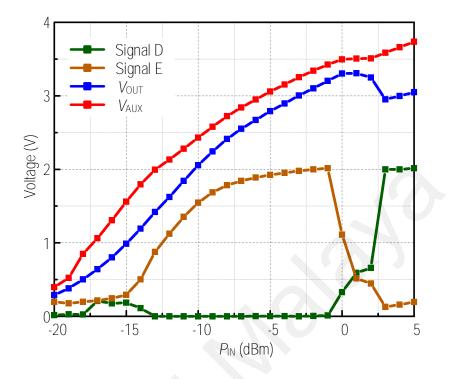

| Figure 5.7: The Bounded Output Voltage of the Main Rectifier under 3.3 V by Control    |

| Signals D and E                                                                        |

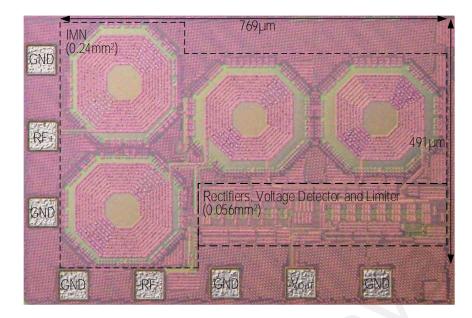

| Figure 5.8: Chip Micrograph of Proposed Tri-band RFEH System                           |

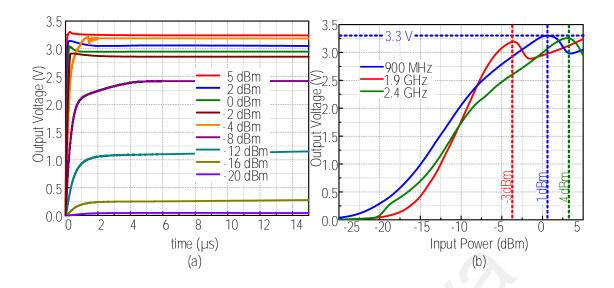

| Figure 5.9: The Graph of (a) Transient Output Voltage Bounded below 3.3 V under        |

| Various Input Power at 100 k $\Omega$ , 1.9 GHz, and (b) Output Voltage vs Input Power |

| Showing the Switching Point of the Voltage Monitor108                                  |

| Figure 5.10: The Performance of Proposed RFEH System: (a) The Plot of $P_{OUT}$ vs $P_{IN}$ at |

|------------------------------------------------------------------------------------------------|

| 100 k $\Omega$ Load Condition and the Contour Plots of the Proposed RFEH System under          |

| Various Load Conditions and Input Power at (b) 900 MHz (c) 1.9 GHz and (d) 2.4 GHz             |

|                                                                                                |

## LIST OF TABLES

| Table 1.1: Application of WSN in Recent Work (Ali et al., 2017)                 |

|---------------------------------------------------------------------------------|

| Table 2.1: Measured RF Power Density at Different Frequency Bands from Various  |

| Locations14                                                                     |

| Table 2.2: Performance Overview of Recent Subthreshold Operation Charge Pumps44 |

| Table 3.1: Capacitance Scaling Configuration for Capacitive Optimization        |

| Table 3.2: Performance Comparison with the State-of-art Charge Pump    74       |

| Table 4.1: Control Logic High Signal for Stage Reconfigurable CP                |

| Table 4.2: Truth Table for Reconfigurable CP's Control Signals    82            |

| Table 4.3: Performance Summary and the State-of-art Comparison of the           |

| Reconfigurable Charge Pump                                                      |

| Table 5.1: Operation Mode of a Conventional Inverter    99                      |

| Table 5.2: Performance Comparison with the State-of-Art Output Voltage110       |

| Table 5.3: Performance Comparison with the State-of-art RFEH System             |

### LIST OF SYMBOLS AND ABBREVIATIONS

| AC   | : | Alternating Current                                   |

|------|---|-------------------------------------------------------|

| AM   | : | Amplitude Modulation                                  |

| BTRO | : | Bootstrapped Ring-Voltage Controlled Oscillator       |

| CCCP | : | Cross-Coupled Charge Pump                             |

| CCDD | : | Cross-Couple Differential Drive                       |

| CMOS | : | Complementary Metal-Oxide-Semiconductor               |

| СР   | : | Charge Pump                                           |

| CTS  | : | Charge Transfer Switch                                |

| dBm  | : | decibel-milliwatts                                    |

| DC   | : | Direct Current                                        |

| DGB  | : | Dynamic Gate Biasing                                  |

| DRC  | : | Design Rule Check                                     |

| EM   | : | Electromagnetic                                       |

| F    | : | Farad                                                 |

| FCC  | : | Federal Communications Commission                     |

| FM   | : | Frequency Modulation                                  |

| GSM  | : | Global Systems for Mobile                             |

| IC   | : | Integrated Circuit                                    |

| IMN  | ÷ | Impedance Matching Network                            |

| IoT  | : | Internet Of Things                                    |

| IRS  | : | Input-Representing-Signal                             |

| LVS  | : | Layout Vs. Schematic                                  |

| LVT  | : | Low-Voltage-Threshold                                 |

| MCMC | : | Malaysian Communications and Multimedia<br>Commission |

| MIM  | : | Metal-Insulator-Metal                                 |

| MOM  | : | Metal-Oxide-Metal                                     |

| MOS  | : | Metal-Oxide-Semiconductor                             |

| NMOS | : | N-Channel Metal-Oxide Semiconductor                   |

| NOC             | : | Non-Overlapping Clocks                     |

|-----------------|---|--------------------------------------------|

| OVC             | : | Oscillator Voltage Controller              |

| PCE             | : | Power Conversion Efficiency                |

| PEX             | : | Parasitic Extraction                       |

| PFM             | : | Pulse Frequency Modulation                 |

| PMOS            | : | P-Channel Metal-Oxide Semiconductor        |

| PMU             | : | Power Management Unit                      |

| PWM             | : | Pulse Width Modulation                     |

| RF              | : | Radio Frequency                            |

| RFEH            | : | RF Energy Harvesting                       |

| R <sub>ON</sub> | : | on-Resistance                              |

| RVCO            | : | Ring Voltage Controlled Oscillator         |

| SoC             | : | System-on-A-Chip                           |

| TSMC            | : | Taiwan Semiconductor Manufacturing Company |

| V               | : | Volt                                       |

| VCE             | : | Voltage Conversion Efficiency              |

| VCO             | : | Voltage Controlled Oscillator              |

| VCR             | : | Voltage Conversion Ratio                   |

| V <sub>DS</sub> | : | Drain-To-Source Voltage                    |

| V <sub>GS</sub> | : | Gate-To-Source Voltage                     |

| VOSC            | : | Oscillator's Input Voltage                 |

| V <sub>TH</sub> | : | Threshold Voltage                          |

| W               | : | Watt                                       |

| WSN             | : | Wireless Sensor Network                    |

| WTP             | : | Wireless Power Transfer                    |

| Φ               | : | Clock Signal                               |

| Ω               | : | Ohm                                        |

#### **CHAPTER 1 : INTRODUCTION**

This chapter of the thesis introduces the research work, including a comprehensive background study and an overview of the topic. It identifies and discusses the problem statement and motivation behind the research and sets out the research objectives as well as the research methodology employed in the study. The chapter concludes by highlighting the contributions of the work and presenting the overall thesis outline.

#### 1.1 Background Study and Motivation

Wireless Sensor Networks (WSN) have emerged as a key technology for monitoring and collecting physical environmental conditions through wireless links in recent years due to the advancement in Internet of Things (IoT) and cloud computing technology. Based on Morgan Stanley Research (Stanley, 2016), WSN is anticipated to be the highest number count of electronic gadgets within the IoT infrastructure due to the explosive growth of electronic devices and its wide use of applications. WSN is a type of network that consists of numerous wireless sensors distributed in a particular area or environment. It is designed to collect and transmit data from the sensors to a central location or server for processing and analysis. Due to its versatile nature, WSN finds ubiquitous use in various applications throughout modern society. Some of its broad range of applications include healthcare monitoring, environment monitoring, industrial monitoring and pandemic monitoring (Ali et al., 2017; Xu et al., 2014). Table 1.1 delineated the detail WSN application and the type of sensors used.

| Application                          | References                   | Uses                                                          | Sensors                                                                                           | City Deployed in              |

|--------------------------------------|------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------|

| Environmental monitoring             | (Jiang et al., 2016)         | Air Quality                                                   | NO2 Sensors                                                                                       | Amsterdam, The<br>Netherlands |

|                                      | (Hasenfratz et al.,<br>2015) | Air Pollution Maps                                            | Particles (UFPs),<br>Temperature,<br>Humidity                                                     | Zurich,<br>Switzerland        |

|                                      | (Mao et al., 2012)           | CO2 Monitoring                                                | CO2,<br>Temperature,<br>Light Sensors                                                             | Wuxi, China                   |

|                                      | (Boustani et al.,<br>2011)   | Waste Removal                                                 | Global System for<br>Mobile (GSM)<br>Tracking Sensors                                             | New York, Seattle             |

| Biomedical                           | (Hii & Chung,<br>2011)       | Ubiquitous<br>Healthcare<br>Solution                          | Electrocardiogram<br>(ECG) Sensor<br>Node, 3G, Code<br>Division Multiple<br>Access (CDMA),<br>GSM | Busan, Korea                  |

|                                      | (Kakria et al.,<br>2015)     | Real time health<br>monitoring System                         | Wearable<br>Biosensors,<br>Android Device,<br>Smart Phone                                         | Pathum Thani,<br>Thailand     |

|                                      | (Yan et al., 2017)           | Structural Health<br>Monitoring System                        | Wireless Smart<br>Aggregate sensor,<br>RF Module,<br>Sampling Module,<br>Gateway                  | Shenyang, China               |

| Wireless Body<br>Area Network        | (Wu et al., 2017)            | Monitoring of<br>Body Temperature,<br>Heartbeat               | Internet of Things                                                                                | -                             |

| 10                                   | (Kantoch et al.,<br>2014)    | Monitoring of<br>Temperature,<br>Heart Rate, Skin<br>Humidity | Computer,<br>Bluetooth                                                                            | -                             |

|                                      | (Woon-Sung et al.,<br>2013)  | Fall detection                                                | Accelerometer,<br>gyroscope, video<br>camera, Infrared<br>sensor                                  | -                             |

| Vehicle and<br>traffic<br>monitoring | (Dagher et al.,<br>2014)     | UNS—Ubiquitous<br>Navigation System                           | RF based, Google<br>Maps                                                                          | Lille, France                 |

| montoring                            | (Srinivasan et al.,<br>2016) | FWI—Fire<br>Weather Index                                     | Internet of Things,<br>GPS Sensors                                                                | Oman                          |

Table 1.1: Application of WSN in Recent Work (Ali et al., 2017)

At present, batteries serve as the primary power source for WSNs. However, the currently available battery in the market (Sudevalayam & Kulkarni, 2011) poses several limitations such as size, weight, and the need for frequent replacements and maintenance. The labour-intensive nature of frequent replacing and maintaining bulky batteries for sensor nodes deployed over a wide region renders it impractical to use them as the primary energy source for WSNs in IoT applications. Therefore, there is a pressing need to explore alternative energy sources such as energy harvesting to extend their functionality.

Energy harvesting is a process of capturing and storing energy from various sources, such as light, heat, motion, or vibration, and converting it into electrical power to sustain the operations of electronic devices or systems. Harvesting energy source is categorized into different categories based on their controllability and predictability (Kansal et al., 2007). As WSNs require a constant energy source 24/7 to operate, uncontrollable energy such as solar energy is not suitable due to its unavailability at night. Unpredictable energy such as kinetic and wind are also deemed to be impractical for their inconsistent availability. Ambient radio frequency (RF) energy is a viable and sustainable solution for powering WSNs (Soyata et al., 2016). It is available through Electromagnetic (EM) wave transmission by Television towers, Global systems for mobile (GSM) towers, Radio networks, Wi-fi, etc. Despite having a lower power density than other sources such as solar and kinetic energy, recent surveys conducted between 2016 and 2021 have shown that the power density of RF energy ranges between 0.06 to 0.57  $\mu$ W/cm<sup>2</sup> globally, thus confirming the feasibility of harvesting ambient RF energy for WSN applications (Ho et al., 2022). As WSN requires a constant cellular internet connection to operate for IoT applications, the presence of RF energy for harvesting is assured. Hence, RF energy harvesting (RFEH) is the ideal energy solution for powering WSNs.

Furthermore, the cost-effective nature of complementary metal-oxide-semiconductor (CMOS) technology enables a system-on-a-chip (SoC) design solution for RFEH systems, facilitating the creation of fully integrated, small form factor RF-powered WSNs. Previous works on RFEH have demonstrated the generation of stable direct current (DC) power through RF energy harvesting (Abouzied et al., 2017; Ramalingam et al., 2021). However, these RFEH circuits experience significant power losses, particularly when transistors operate in the subthreshold region due to the low operational voltage obtained from the harvested RF energy. This study aims to enhance the efficiency of RFEH systems, specifically in the design of the charge pump (CP) block, in order to minimize power losses in RFEH systems with low input voltages.

#### **1.2 Problem Statement**

Figure 1.1 shows the general RFEH system block diagram. It consists of an RF antenna to harvest ambient RF energy, an Impedance Matching Network (IMN) to match the impedance of the antenna and the RFEH system for maximum power transfer, a rectifier to convert the scavenged alternating current (AC) power to a usable DC power, a CP to step-up the rectified power and a control unit to manage the output voltage to ensure the compatibility with the WSN application. Designing an RFEH system poses a significant challenge primarily due to the low voltage obtained from the scavenged RF, which causes high conduction and reversion losses in the rectifier and charge pump blocks, ultimately leading to a low-efficiency RFEH system. The primary focus of this work is to improve the design topology of a low-voltage CP for WSN application.

Figure 1.1: General System Diagram of an RF-Based Energy Harvesting System

The two most common CP architectures are Dickson and cross-coupled topology. The diode-connection transistor in Dickson topology offers the advantage of zero reverse current leakage at the cost of high threshold voltage ( $V_{TH}$ ) drop.

In the recently published works, many have explored a variety of techniques and architecture to improve the CP performance. Yet, only a few works focus on the low input voltage scenarios that are relevant to the RFEH application. The power harvested from ambient RF is relatively low compared to other energy harvesters such as solar and piezoelectric. Conventional CP architectures are not suitable for RFEH applications due to their low scavenged input voltage. This is because the transistors in the CP are working in the subthreshold region and are not able to be fully turned ON/OFF. This leads to a massive forward conduction and reversion-leakage loss which greatly deteriorates the RFEH performance. Therefore, a novel CP and rectifier architecture that aims to reduce the forward conduction and reverse-leakage loss is required to design a high-efficiency RFEH system at low input voltage.

Another challenge in RFEH systems is the fluctuating input voltage. Existing CP topologies are typically designed and optimized for a specific voltage level. However, in energy harvesting applications, the input voltage can vary significantly, ranging from 0.2 V to 0.6 V. This wide voltage fluctuation makes it difficult for conventional CPs to maintain high efficiency across the wide input voltage range. To address this limitation, a reconfigurable CP that can adapt to these input voltage variations is crucial.

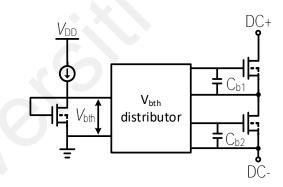

Furthermore, a notable challenge arises in maintaining a consistent output voltage within the RFEH system due to the inherent fluctuations in the harvested input power. Presently, state-of-the-art voltage limiters rely on external power sources to establish a voltage reference or to drive the control switches, rendering them ill-suited for selfsustaining energy harvesters. Additionally, the existing batteryless voltage limiter works consume substantial power, rendering them unsuitable for application in low-power RFEH systems.

#### **1.3 Research Objectives**

The objective of this research is to develop a novel highly efficient subthreshold operation CP topology and a fully integrated RFEH system with an output voltage monitoring unit tailored for WSN applications. The existing state-of-the-art CMOS CP topologies are geared toward high-voltage applications that are not suitable for RFEH systems (Feng et al., 2006; Shin et al., 2010; Yu et al., 2017). Furthermore, the-state-ofthe-art improvement in low-voltage CP designs continue to grapple with high conduction and reversion losses, hindering their power conversion efficiency (PCE) from surpassing the 40% barrier (A. Ballo et al., 2020b; Chen et al., 2012; Fuketa et al., 2017). Besides that, the high unregulated scavenged output voltage poses the risk of damaging the WSN load (Wang & Kose, 2018). Therefore, this research seeks to develop innovative techniques and investigate novel topologies to enhance the performance of ultra-low voltage CP for RF energy harvesting with output voltage limiting capability.

The objectives of this research are listed below.

To design and develop a novel high-efficiency (> 40 %) subthreshold operation

CMOS DC-DC converter for low input voltage energy harvesting application.

- **ii.** To engineer and fabricate a reconfigurable CP with output voltage limiting capability across a broad input voltage spectrum spanning from 0.26 V to 0.64 V.

- iii. To design and develop a novel dynamic source-fed oscillator to achieve frequency modulation for reconfigurable CP, accommodating a wide input voltage variation.

- iv. To design and implement a novel low-power voltage monitor and voltage limiter to effectively constrain the output voltage of the RFEH system under a boundary threshold of 3.3 V, catering specifically towards WSN applications.

#### 1.4 Research Methodology

Figure 1.2 illustrates the comprehensive research methodology of this thesis. The process commences with an extensive background study and literature review of conventional subthreshold operation rectifiers and CP topologies, reconfigurable CP, frequency modulation, and the voltage limiter for RFEH systems. Subsequently, the process advances to the identification of problems and research gaps, as well as the delineation of the research scope drawing from the earlier literature review. Following this, the methodology proceeds with the development of an innovative CP design that leverages the dynamic gate biasing (DGB) technique to achieve high PCE during subthreshold operation. A rigorous simulation process is conducted to validate the circuit's performance, ensuring its effectiveness under subthreshold conditions. Upon completion of circuit optimization, the design will proceed to fabrication if it attains the target performance threshold of over 40 % PCE. In case the target is not met, a redesign of the circuit will be initiated.

Figure 1.2: Research Methodology Flow Chart

Subsequently, a series-parallel reconfigurable CP circuit with output-limiting capability is designed using an ideal clock with a fixed frequency. Following an iterative simulation and testing phase, the work enters the next design phase to develop a dynamic source-fed oscillator to perform frequency modulation to accommodate the fluctuating wide input voltage. The iterative simulation and testing of the reconfigurable CP circuit are once again performed with the inclusion of the dynamic source-fed oscillator. The design advances to the fabrication stage once satisfactory results have been attained.

Next, the project explores an alternative output voltage limiting technique with the design of a novel low-power voltage monitoring unit and a voltage limiter calibrated to maintain a consistent output voltage under 3.3 V. Extensive design and layout simulations are conducted, and the design will be sent for fabrication once it satisfies the predefined design constraints.

The circuit layout of the designed circuits is constructed based on the circuit schematics. The layout undergoes two essential rule checks: the Design Rule Check (DRC) to ensure compliance with fabrication requirements and the Layout vs. Schematic (LVS) check to verify layout consistency with the schematic. Following the successful completion of these checks, a Parasitic Extraction (PEX) is performed to account for parasitic losses, enabling post-layout verification.

All the designed circuits are realized using Cadence software and fabricated under Taiwan Semiconductor Manufacturing Company's (TSMC) 65 nm CMOS technology. Upon fabrication, post-silicon validations are conducted to obtain the measurement result of the designs' performance. The acquired results are meticulously analyzed and compared with recently published works to emphasize the research contributions. Finally, the research findings are compiled and thoroughly documented for research publications.

#### 1.5 Contributions of the Research Work

The contributions of this work are highlighted as shown below.

- i. A novel CP architecture for low-power RFEH system with high Power Conversion Efficiency (PCE) in subthreshold operation with chip verification.

- A reconfigurable series-parallel CP with output voltage limiting capability across a broad input voltage spectrum spanning from 0.26 V to 0.64 V.

- iii. A novel dynamic source-fed oscillator with frequency modulation ability to adapt to a wide input voltage range.

- iv. SoC solution capabilities of the CCCP topology for system integration for ambient RFEH and WSN application.

- A novel low-power voltage monitoring circuit and voltage limiter to maintain a boundary voltage of 3.3 V for IoT WSN applications.

#### 1.6 Scope of Work

The primary focus of this study is to design a highly efficient RFEH system. As illustrated in Figure 1.1, the RFEH system comprises an IMN, rectifier, CP, and logic control unit. However, this investigation is solely centred on the design of the RFEH backend system, which is the CP and the output voltage control unit. To simulate the frontend section of the RFEH, a DC source with a series resistor is employed to supply the Thevenin voltage to the CP, allowing for an accurate evaluation of its performance. A comprehensive outline of the experimental setup will be presented in Chapter 3.4.1. It is noteworthy that since the CP and rectifier share the same topology, all the enhancement methods outlined in this work can be implemented on the rectifier unless otherwise specified.

#### 1.7 Thesis Outline

This thesis comprises five chapters that cover various aspects of the research. Chapter 1 introduces the research background and presents the problem statement and motivation behind the study. It also outlines the research objectives and highlights the contributions of the research work. Chapter 2 provides a comprehensive literature review, focusing on RF power availability, CMOS RFEH circuit overview, and the latest advancements in rectifier and charge pump improvement techniques for high-efficiency operation. This review serves as a foundation for the subsequent chapters. In Chapter 3, the thesis delves into the proposed advanced DGB technique for CP design. The chapter also includes a comparison of the research findings with recent publications, highlighting the novelty and effectiveness of the proposed technique. Chapter 4 presents a novel reconfigurable seriesparallel CP with output-limiting capabilities featuring a novel dynamic source-fed oscillator for frequency modulation. Chapter 5 delves into the design of an integrated RFEH system with a novel low-power voltage monitoring unit capable of limiting the output voltage under a boundary level of 3.3 V for WSN applications. Finally, Chapter 6 concludes the thesis and explores the future work for the research.

#### **CHAPTER 2 : LITERATURE REVIEW**

#### 2.1 Chapter Overview

This chapter delves into a comprehensive literature review of the RFEH system, starting with an investigation of the RF power availability for energy harvesting. It is followed by an in-depth overview of the conventional CMOS rectifier and CP architecture, providing valuable insights into the existing designs and their operation principles. Furthermore, it provides a comprehensive literature review on the state-of-the-art rectifier and CP improvement techniques with a discussion of their strengths and limitations. The chapter concludes with a summary of the key findings and contributions of the literature review.

#### 2.2 RF Energy

#### 2.2.1 Background

RF energy is an electromagnetic wave propagating in a free space medium for information transformation (Visser & Vullers, 2013; Vullers et al., 2009). The RFEH system can be classified into two categories, namely Near-field and Far-field, based on the propagation distance. The boundary between these two types of RFEH is determined by the Fraunhofer distance (Selvan & Janaswamy, 2017). A Near-field RFEH is commonly known as Wireless Power Transfer (WTP). It is achieved by transmitting energy through two magnetic-coupled coils placed in close proximity (S. Kim et al., 2014). In contrast, a Far-field RFEH system is designed to collect residual electromagnetic RF energy that is propagated through the air. This form of energy is generated by radio transmission antennas found in devices such as base stations, Wi-Fi routers, and Bluetooth-enabled devices. The power density harvested by a Far-field RFEH system is comparatively lower than that of a Near-field RFEH system due to the increased propagation distance, which is explained by the Friis transmission equation, showing in the equation (2.1) below. (Friis, 1946).

$$P_{ANT} = \frac{P_T G_T G_R c^2}{(4\pi D f)^2}$$

(2.1)

where  $P_{ANT}$  is the received power,  $P_T$  is the transmitted power,  $G_T$  is the antenna gain of the transmit antenna,  $G_R$  is the antenna gain of the receive antenna, c is the speed of light, f is the RF wave frequency and D is the distance of RF transmission between the transmit and receive antennas.

The scope of this thesis is centered around Far-field RFEH systems, with a specific focus on the application in low-power WSN. It is important to note that the term RFEH as denoted in this thesis exclusively refers to Far-field RFEH systems.

#### 2.2.2 RF Availability

Ambient RF energy is widely available as it is designated for specific uses in data transmission in telecommunication, such as Amplitude Modulation (AM) radio, Frequency Modulation (FM) radio, television, cellular communications, Wi-Fi, and Bluetooth. These RF bands are allocated by the International Telecommunication Union and are regulated by the regulatory bodies, such as the Federal Communications Commission (FCC) in the United States, and Malaysian Communications and Multimedia Commission (MCMC) to avoid interference and ensure efficient use of the radio spectrum (Hesser & Hamburg, 1995).

Table 2.1 tabulates the measured RF power density at different frequency bands from various locations (Adam et al., 2017; Pinuela et al., 2013; Roy et al., 2021; Zeng et al., 2017). From Table 2.1, it is evident that the prospect of harvesting RF energy from ambient sources, including TV, GSM, and WLAN base stations, holds great promise, as these signals are omnipresent in urban environments. Nevertheless, it is important to

## Table 2.1: Measured RF Power Density at Different Frequency Bands from

| Band             | Frequency               | Location                                | Average Power           | Peak Power              |

|------------------|-------------------------|-----------------------------------------|-------------------------|-------------------------|

| Digital<br>TV    | 470 MHz - 610 MHz       | <sup>a</sup> Underground<br>Station     | 0.89 nW/cm <sup>2</sup> | 460 nW/cm <sup>2</sup>  |

| GSM 900<br>(2G)  | 800 MHz – 915 MHz       | <sup>a</sup> Underground<br>Station     | 36 nW/cm <sup>2</sup>   | 1930 nW/cm <sup>2</sup> |

|                  | 880 MHz – 960 MHz       | <sup>c</sup> Semi-urban/<br>urban Areas | -34.9/-26.65<br>dBm     | -22.66/-7.65<br>dBm     |

|                  | 925 MHz – 960 MHz       | <sup>d</sup> University                 | n.a.                    | -22.5 dBm               |

|                  | 935 MHz – 960 MHz       | <sup>b</sup> Shopping<br>Center         | -50/-56 dBm             | -45/-52 dBm             |

| GSM<br>1800 (2G) | 1.805 GHz – 1.88<br>GHz | <sup>a</sup> Underground<br>Station     | 84 nW/cm <sup>2</sup>   | 6390 nW/cm <sup>2</sup> |

|                  |                         | <sup>d</sup> University                 | n.a.                    | -17.8 dBm               |

|                  | 1.805 GHz – 1.85<br>GHz | <sup>b</sup> Shopping<br>Center         | -55/-48 dBm             | -54.9/-39 dBm           |

| UMTS<br>(3G)     | 1.92 GHz – 2.2 GHz      | <sup>c</sup> Semi-urban/<br>urban Areas | -43.27/-13.33<br>dBm    | -29.09/-10.65<br>dBm    |

|                  | 2.11 GHz – 2.17 GHz     | <sup>a</sup> Underground<br>Station     | 12 nW/cm <sup>2</sup>   | 240 nW/cm <sup>2</sup>  |

|                  | 2.11 GHz – 2.23 GHz     | <sup>d</sup> University                 | n.a.                    | -23 dBm                 |

| WiFi             | 2.32 GHz – 2.575<br>GHz | <sup>b</sup> Shopping<br>Center         | -70/-65 dBm             | -61/-60 dBm             |

|                  | 2.39 GHz – 2.4 GHz      | <sup>d</sup> University                 | n.a.                    | -25.6 dBm               |

|                  | 2.4 GHz – 2.5 GHz       | <sup>a</sup> Underground<br>Station     | 0.18 nW/cm <sup>2</sup> | 6 nW/cm <sup>2</sup>    |

|                  |                         | <sup>c</sup> Semi-urban/<br>urban Areas | -43.19/-24.8<br>dBm     | -29.92/-15.56<br>dBm    |

| LTE (4G)         | 2.5 GHz – 2.7 GHz       | <sup>d</sup> University                 | n.a.                    | -26.5 dBm               |

### **Various Locations**

<sup>a</sup>London Underground stations, UK; <sup>b</sup>Shunde shopping center/ residential area, China; <sup>c</sup>Kedah and Perlis (semi-urban area)/ Penang (urban area), Malaysia; <sup>d</sup>Multimedia University, Selangor, Malaysia

acknowledge that the harvested RF power is relatively lower compared to the other renewable energy sources such as solar, wind, and kinetic energy. As a result, its feasibility is confined to a restricted range of WSN applications. There has been a notable surge in research interest surrounding the development of high-efficiency RFEH systems specifically tailored for low-power operations to resolve the mentioned issue.

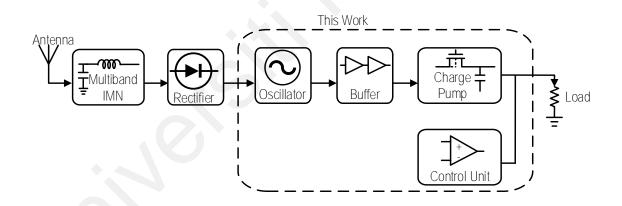

#### 2.3 RFEH Circuit

Figure 2.1 illustrates the block diagram of an RFEH system, compromising two distinct components. The front-end circuit serves the purpose of harvesting ambient RF energy and converting it into DC power. On the other hand, the back-end circuit is responsible for the management and step-up of the harvested DC power to a higher voltage level suitable for the intended output WSN application.

Figure 2.1: Block Diagram of an RF-DC Energy Harvester

#### 2.3.1 RFEH Front-End Circuit

The front-end circuit consists of a receiving antenna, an IMN, and a rectifier. The antenna captures the ambient and transfers it to the rectifier for voltage rectification. The IMN resides between the antenna and the rectifier to resonate the impedance of the antenna to the RFEH system for maximum power transfer.

Conventionally, a 50  $\Omega$  antenna is widely utilized in RF applications to correlate a balance between low loss and power handling capabilities, particularly for coaxial connections (Gilmour, 1986). The harvested RF voltage from the antenna can be determined by equation (2.2) (Karthaus & Fischer, 2003):

$$\boldsymbol{V}_{ANT} = \sqrt{\boldsymbol{8} \times \boldsymbol{R}_{ANT} \times \boldsymbol{P}_{ANT}} \tag{2.2}$$

where  $V_{ANT}$  is the receive antenna's peak input voltage,  $R_{ANT}$  is the receive antenna's radiation resistance, and  $P_{ANT}$  is the harvested ambient RF power from the antenna.

The scavenged voltage from the antenna is particularly low, in the range of milli-Volts due to the lower ambient RF power as mentioned in section 2.2.2 previously. The lower voltage will deteriorate the performance of the subsequent RFEH block. Therefore, many RFEH works have proposed techniques and topologies to improve the rectifier and CP performance in low input voltage applications.

The RF-DC rectifier serves as the central component within the front-end RFEH system. Its primary role involves the conversion of harvested RF power into usable DC power, which is then transmitted to the back-end circuit for subsequent management and processing. The utilization of CMOS-based rectifiers is widely preferred in RFEH systems, primarily due to their ability to be implemented on-chip. These rectifiers consist of a series of rectifying transistors and flying capacitors that work in tandem to ensure the conversion of AC into a unidirectional current flow, thereby achieving the desired rectification effect. Multiple stages of rectifiers can be cascaded in series to increase the voltage gain for voltage multiplication.

#### 2.3.2 RFEH Back-End Circuit

The RFEH back-end circuit is further divided into two parts, the DC-DC converter for voltage boosting and the Power Management Unit (PMU) for ensuring a stable and reliable output voltage is delivered to the load. Although the rectifier can achieve voltage boosting by cascading multiple rectifier stages, the high switching frequency inherent in the RF waves can result in substantial switching losses within the rectifying transistors. To mitigate these losses, numerous prior RFEH designs have incorporated a dedicated DC-DC converter (Colella et al., 2016; Seong et al., 2016; You et al., 2011; Zhang & Lee, 2010). The utilization of a DC-DC converter offers flexibility in frequency operation and enables output voltage regulation using techniques such as Pulse Width Modulation (PWM) and Pulse Frequency Modulation (PFM). By operating at a lower frequency than the RF wave, the DC-DC converter allows for precise control over the output voltage while minimizing switching losses. This enhances the overall performance and efficiency of the energy harvesting system.

There are two basic types of DC-DC converter namely inductive boost converter and switch capacitor converter. While inductor-based boost converter exhibits superior performance in power conversion and can achieve high efficiencies at very low input voltages (Goeppert & Manoli, 2016; Ramadass & Chandrakasan, 2010; Wens et al., 2007), the necessity of bulky off-chip inductor hinders its implementation in monolithic design (Shih & Otis, 2011). Consequently, a capacitive DC-DC converter emerges as the preferred choice in an integrated RFEH system for WSN application.

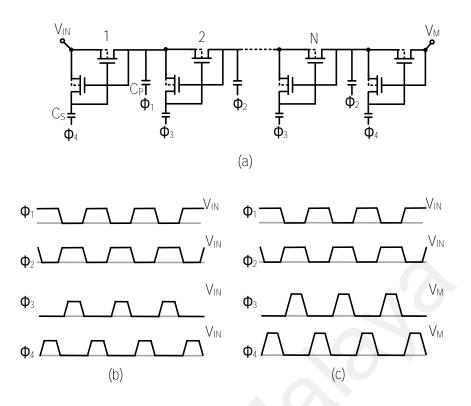

A switch capacitor converter, commonly referred to as a CP, operates on the fundamental principles of charge transfer and charge conservation (Rodriguez et al., 2016). The switch capacitor converter stores charge in a flying capacitor during the initial

pumping cycle and transfer them to the subsequent stages of the CP to achieve voltage boosting. The pumping operation is governed by two complementary clocks generated by the ring oscillator and the buffer circuit.

Ring oscillators are widely used in CP operations as clock signal generators due to their compact design and ease of implementation. It compromises a series of cascading inverters in an odd number of stages. The sinusoidal waveform generated by the oscillator will subsequently be directed into a buffer circuit to shape it into a square wave clock signal. Generally, the buffer circuit will generate two complementary clock signals for the CP operation.

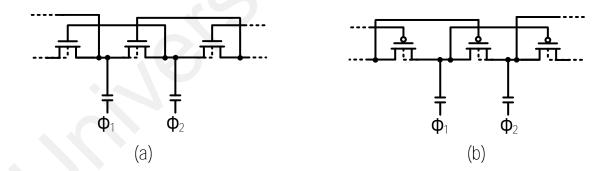

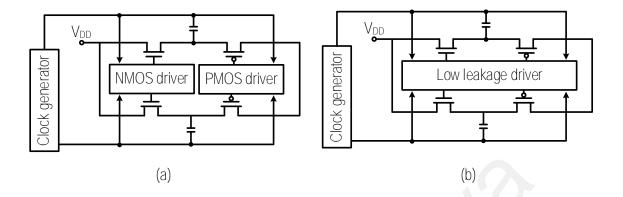

There are different types of complementary clock signals for CP as depicted in Figure 2.2. According to the research conducted by Feng et al. (2006), non-overlapping clocks (NOC) have been identified as the optimal choice for CP operations, primarily due to the ability to reduce reversion loss across the pumping transistors. The type-I clock scheme is typically preferable for N-channel Metal-Oxide Semiconductor (NMOS) transistors in charge pump circuits because it includes a period where both clocks are low. This ensures that the NMOS transistors are turned off before a significant potential difference is established, thus preventing reversion loss and undesired charge transfer. Conversely, the non-overlap type-II clock scheme is more suitable for P-channel Metal-Oxide Semiconductor (PMOS) transistors in charge pump circuits, as it provides a period where both clocks are high, effectively preventing reversion loss by ensuring that the PMOS transistors remain turned off during that time.

The NOC generator can be constructed using either NAND gates (Bose et al., 2019; Kim et al., 2015) or NOR gates (Yu et al., 2017; Zhang & Lee, 2013) as shown in Figure 2.3. It consists of two components: the logic gate, which ensures the generation of nonoverlapping clock signals, and the buffer series, which facilitates the generation of square wave clock signals.

Conventional Overlapping Clock Scheme (b) Non-Overlap Type-I Clock Scheme

(c) Non-Overlap Type-II Clock Scheme

Figure 2.3: Schematic Block Diagram of Non-Overlap Clock Generator using (a)

NAND Gates and (b) NOR gate.

# 2.3.3 Performance Evaluation Parameters

In assessing the performance of RFEH systems, several indicators are utilized to evaluate their effectiveness. Key indicators commonly employed for RFEH performance evaluation include: Sensitivity refers to the ability of an RFEH system to capture and convert RF energy. It is the measure of the minimum input power required for the RFEH system to produce a 1 V DC output voltage at the desired condition. The representation of the RFEH sensitivity is given in equation (2.3) below (Chong et al., 2018):

$$P_{dBm} = 10 \log_{10}(P_{mW})$$

(2.3)

Where  $P_{mW}$  is the input power in milli-Watt. The sensitivity is evaluated in dBm as the RF power received is in the range of milli or micro-watts.

b) Power Conversion Efficiency

Power Conversion Efficiency or PCE, is an indicator that measures the ability of the RFEH system to convert harvested RF power into usable DC power. The PCE is calculated by dividing the output DC power by the input RF power, expressing the efficiency of energy conversion shown in equation (2.4) (Poo et al., 2021):

$$PCE_{RFEH} = \frac{P_{OUT}}{P_{IN}} = \frac{V^2_{OUT} \times R_{LOAD}}{P_{IN}}$$

(2.4)

where  $P_{OUT}$  and  $P_{IN}$  is the output power of the RFEH respectively,  $V_{OUT}$  is the output voltage and  $R_{LOAD}$  is the load resistance.

PCE is also an important indicator to evaluate the DC-to-DC power conversion efficiency for the back-end RFEH circuit. It is a measure of the ratio of the boosted DC output power to the input DC power as in equation (2.5) (Churchill et al., 2020):

$$PCE_{CP} = \frac{P_{OUT,CP}}{P_{IN,CP} + P_{PERI}}$$

(2.5)

where  $P_{OUT,CP}$  is the output power of CP,  $P_{IN,CP}$  is the input power of CP and  $P_{PERI}$  is the power consumption of the peripheral circuits.

c) Voltage Conversion Efficiency

The voltage conversion efficiency, VCE, is an indicator for the RFEH backend evaluation parameter which measures the ability of the DC-DC converter to amplify the harvested DC voltage to a higher output voltage level (Churchill et al., 2020):

$$VCE_{CP} = \frac{V_{OUT,CP(actual)}}{V_{OUT,CP(ideal)}}$$

(2.6)

where  $V_{OUT,CP(actual)}$  is the actual measured output voltage of CP while  $V_{OUT,CP(ideal)}$  is the ideal output voltage of CP without losses.

#### 2.3.4 Subthreshold Operation

# 2.3.5 Types of Power Losses in Rectifier and CP

Efficient identification and mitigation of power losses in transistors play a crucial role in optimizing the performance of RFEH systems. These losses, encompassing forward conduction losses, reverse current losses, and switching losses, are typically observed in key components such as the rectifier and the DC-DC converter, necessitating careful attention for improving overall system efficiency.

#### a) Forward Conduction Loss

Forward conduction loss refers to the power dissipated when current flows through a transistor during the forward conduction phase due to the internal resistance of the transistor as shown in equation (2.7) (Jung et al., 2014):

$$\boldsymbol{P_{conduction}} = \boldsymbol{C} \times \boldsymbol{\Delta}^2 \times \boldsymbol{f_{SW}}$$

(2.7)

where *C* is the pumping capacitance,  $f_{SW}$  is the switching frequency and  $\Delta$  is the voltage drop due to the on-resistance of the transistor. The forward conduction loss can also be expressed in terms of current loss as in equation (2.8) (Ling & Dongsheng, 2008):

$$P_{conduction} = R_{ON} \times f_s \int_0^{DT} i^2(t) dt$$

(2.8)

where the on-resistance ( $R_{ON}$ ), which is the internal resistance of a conducting transistor given by equation (2.9) (Churchill et al., 2020):

$$R_{ON} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}$$

(2.9)

The parameter  $\mu$  represents the mobility of electrons or holes in a semiconductor material, while  $C_{ox}$  denotes the oxide capacitance, which is a technology-dependent parameter related to the capacitance of the insulating oxide layer. It is evident from the expression that increasing the gate-to-source voltage ( $V_{GS}$ ) and the width of the transistor (W) can help reduce the on-resistance and, consequently, minimize conduction losses.

#### b) Switching Loss

Switching loss is the total dynamic power loss due to the switching transitions of a transistor. It occurs when the device undergoes rapid changes in its conducting or non-conducting state. During switching, there is a brief period where the device is neither fully OFF nor fully ON, resulting in a temporary overlap between the current flows. The expression of switching loss is given by equation (2.10) (Prado et al., 2022):

$$P_{Switching} = \frac{1}{2} (t_{ON} V_{DS} I_{ON} + t_{OFF} V_{DS} I_{OFF}) \times f_{SW}$$

(2.10)

where  $V_{DS}$  is the drain-to-source voltage of the CMOS transistor, and  $I_{ON}$ ,  $I_{OFF}$ ,  $t_{ON}$ ,  $t_{OFF}$ are the respective current and overlap duration of the transistor turn-on and turn-off phases. Equation (2.10) demonstrates the significant impact of switching frequency on the switching loss, emphasizing the need to minimize the frequency for effective reduction of overall switching losses. Furthermore, the switching loss is inversely proportional to the conduction loss. This correlation implies that mitigating switching losses may lead to an increase in conduction losses, and vice versa. Hence, achieving an optimal balance between these two losses becomes essential in order to optimize the performance of the system and maximize energy efficiency.

#### c) Reverse Current Loss

Reverse current loss, also known as reverse charge leakage, pertains to the undesired leakage or backflow of charge from the subsequent rectifier or CP stages to the preceding stages. The expression of reversion loss is given by equation (2.11) (Ling & Dongsheng, 2008):

$$P_{reverse} = \frac{1}{2} \left( \frac{C_b C_L (V_{OUT} - V_b)^2}{C_b + C_L} \right) \times f_{SW}$$

(2.11)

where  $C_b$  is the pumping capacitance,  $C_L$  is the load capacitance,  $V_{OUT}$  is the output voltage,  $V_b$  is the pumping voltage and  $f_{SW}$  is the switching frequency. The phenomenon of reversion loss occurs when the pumping transistors fail to effectively turn OFF during the reverse conduction phase, leading to a diminished transfer of charges to the output. Several factors can contribute to the improper turn-off of transistors, including variations in the  $V_{TH}$ , inadequate  $V_{GS}$  drive, and dissipation from short circuits (Eid & Rodriguez-Villegas, 2017; Kim et al., 2009; J. Y. Kim et al., 2014). However, it is important to note that the strategies employed to reduce reversion loss may lead to an increase in conduction loss. Therefore, careful consideration of design strategies is necessary to obtain the optimal balance point that enhances the overall efficiency and performance of the rectifier or charge pump circuit.

#### 2.4 Conventional Rectifier and CP Topologies

Rectifiers and CPs share a similar circuit topology but with different input sources. The Dickson architecture, as depicted in Figure 2.4, represents the fundamental topology for both rectifiers and CPs (Dickson, 1976). A single stage of Dickson topology consists of two diode-connected transistors  $M_{Dn}$ ,  $M_{Dn+1}$ , and a coupling capacitor,  $C_n$ . For the rectifier, the Dickson topology takes a single RF voltage as input while CP has three DC inputs, which are  $V_{DD}$ , and two oscillating clocks,  $\Phi_1$  and  $\Phi_2$ . Given the shared topology between the rectifier and CP circuits and the focus of this work on the backend RFEH circuit, this thesis will solely delve into the operation of the CP circuit from this point onwards.

Figure 2.4: Conventional Dickson Topology of (a) Rectifier and (b) Charge Pump

During the second-half clock cycle, the first stage of the Dickson CP is operating in the reverse conduction phase with  $M_{D2}$  conducting in reverse-bias mode and  $M_{D3}$ conducting in forward-bias mode as depicted in Figure 2.5. During this phase, the low amplitude of the clock  $\Phi_1$  creates a potential difference with the DC input voltage,  $V_{DD}$ , causing the charge to pass through  $M_{D1}$  from the CP input. This results in the charging of C<sub>1</sub> to a voltage level equivalent to  $V_{DD}$ . At the same time, the reverse bias on  $M_{D2}$  prevents the charges from C<sub>2</sub> from backflowing into the preceding stage.

Figure 2.5: The Operation of Dickson CP at (a) The Second-Half Clock Cycle and (b) the First-Half Clock Cycle

During the first-half clock cycle,  $\boldsymbol{\Phi}_1$  swings from low to high while  $\boldsymbol{\Phi}_2$  swings from high to low. This causes transistor M<sub>D2</sub> to conduct in forward bias and M<sub>D3</sub> conducts in reverse bias condition. The high voltage amplitude from  $\boldsymbol{\Phi}_1$  pushes the charges from C<sub>1</sub> through the M<sub>D3</sub> to charge the C<sub>2</sub> to a voltage level of  $\boldsymbol{V}_{\boldsymbol{\Phi}1} + \boldsymbol{V}_{C1}$ , which corresponds to  $2 \, \boldsymbol{V}_{DD}$ . The process of altering charging and discharging the coupling capacitor over the two-half clock cycle enables voltage boosting in the CP circuit. The output voltage of a Dickson CP is formulated as in equation (2.12) (Ho et al., 2022):

$$\mathbf{V}_{\text{OUT}} = \mathbf{V}_{\text{DD}} - \mathbf{V}_{\text{th}} + \mathbf{N} \left( \frac{\mathbf{C}}{\mathbf{C} + \mathbf{C}_{\text{par}}} \times \mathbf{V}_{\Phi} - \mathbf{V}_{\text{TH}} - \mathbf{V}_{\text{loss}} \right)$$

(2.12)

where  $V_{TH}$  is the threshold voltage of the diode-connected transistor, N is the number of CP stages, C is the pumping capacitance,  $C_{par}$  is the parasitic capacitance at the bottom plate of the pumping capacitor,  $V_{\Phi}$  is the clock amplitude and  $V_{loss}$  is the voltage loss. The equation (2.12) reveals a significant  $V_{TH}$  drop in the Dickson CP due to the diode-connected transistor. Given the typically low voltage scavenged from RFEH, this

substantial  $V_{TH}$  drop renders the Dickson topology unsuitable for RFEH applications. Consequently, a switch-based CP topology was introduced as an alternative solution.

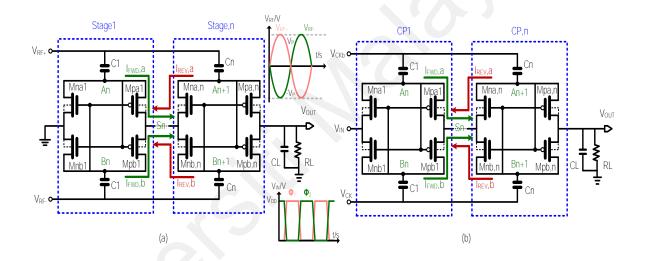

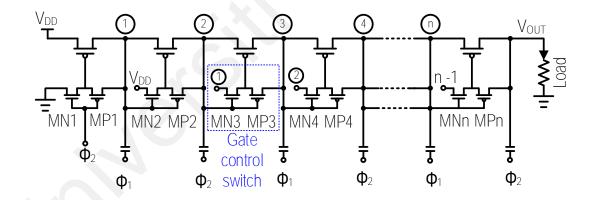

Figure 2.6 illustrates the rectifier and CP cross-coupling architecture which utilized switch-connected transistors to eliminate reverse current loss (Ballo et al., 2021). The cross-coupling architecture comprises two complementary charge-transferring paths, Path A and Path B, which enable voltage transfer to the output during both half cycles. Each path consists of a pair of cross-connecting NMOS-PMOS transistor pair and a coupling capacitor.

Figure 2.6: Conventional Cross-Coupled Topology of (a) Rectifier and (b) Charge Pump

Figure 2.7 illustrates the operation of cross-coupled CP topology. When  $\Phi_1$  transitions from high to low and  $\Phi_2$  transitions from low to high during the second half clock cycle, Path A of the Cross-coupled Charge Pump (CCCP) operates in reverse conduction mode while Path B operates in forward conduction mode. As a result, transistor M<sub>na1</sub> in Path A turns ON while transistor M<sub>pa1</sub> turns OFF. The charges from the input voltage,  $V_{IN}$ , flow through M<sub>na1</sub> to charge the capacitor C<sub>1</sub> to the voltage level of  $V_{DD}$ . Conversely,  $\Phi_1$  transitions from low to high while  $\Phi_2$  transitions from high to low during the first-half clock cycle. As a result, Path A of the CCCP enters the forward conduction mode, while Path B enters the reverse conduction mode. The high voltage amplitude from the clock  $\Phi_1$  drives the transfer of charges from capacitor C<sub>1</sub> to the subsequent CP stage, resulting in the charging of the pumping capacitor in the next stage to a voltage level of 2  $V_{DD}$ . The operation of Path B is identical to that of Path A, except it occurs in the alternate clock cycle.

Figure 2.7: The Operation of Cross-coupled CP at (a) The Second-Half Clock Cycle and (b) The First-Half Clock Cycle

The CCCP overcomes the drawback of high  $V_{TH}$  loss associated with diode-connected transistors in the Dickson topology. Moreover, the dual branch connection in the CCCP

allows charge delivery to the output during both the charging and discharging phases. This can effectively suppress the output voltage ripples (Jiang et al., 2018).

While the CCCP architecture offers several advantages, it also exhibits setbacks, especially when it comes to reversion loss. Consequently, considerable research efforts which will be discussed in the following section have been devoted to overcoming this issue by devising enhancement methods specifically tailored for low-input voltage CCCP circuits.

# 2.5 Rectifier and CP Topologies Improvement Method

## 2.5.1 Gate Biasing Technique

#### a) VTH Compensation

The gate bias technique refers to the practice of applying a specific voltage bias to the gate terminal of a transistor to change its  $R_{ON}$  for nullifying the  $V_{TH}$  drop across a transistor. The most common gate biasing technique is  $V_{TH}$  compensation for Dickson topology where a voltage level of  $V_{TH}$  is applied to the  $V_{GS}$  of a transistor to compensate for the voltage drop across the diode-connected transistor.

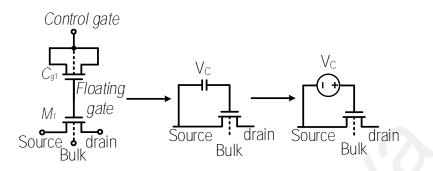

Le et al. (2008) proposes a floating gate threshold voltage compensation technique. This technique utilized the behavior of charge trapping in a floating gate PMOS transistor which acts as a capacitor. The floating gate PMOS is connected between the drain and the gate terminal of the diode-connected transistor to passively reduce the effective threshold voltage of the transistor as shown in Figure 2.8. This method however requires accurate pre-charging to avoid excessive extra potential, which can lead to negative turn-on voltages. Moreover, the pre-charging process requires an external battery which is not suitable for autonomous solutions. Chouhan and Halonen (2015) put forth a  $V_{TH}$  compensation scheme that eliminates the need for external manual pre-charging. This

scheme accomplishes  $V_{TH}$  compensation by utilizing capacitors as pumping storage to nullify the impact of  $V_{TH}$ . The C<sub>bat</sub> is charging during the positive cycle and discharging during the negative cycle, thereby providing the necessary bias voltage for transistor P1.

Figure 2.8: Floating Gate Threshold Voltage Compensation Technique (Le et al., 2008)

The work on Palumbo and Pappalardo (2010) and Umezawa et al. (1992) improves the Dickson topology with a bootstrap CP using an additional transistor and capacitor to bias the gate terminal of the charge-transferring transistor as illustrated in Figure 2.9. The capacitor provides the biasing voltage for  $V_{TH}$  compensation while the additional transistor acts as the gate control switch for voltage biasing.