## ON THE PREVENTION OF CROSS-VM CACHE-BASED SIDE CHANNEL ATTACKS

**ZAKIRA INAYAT**

FACULTY OF COMPUTER SCIENCE AND INFORMATION TECHNOLOGY UNIVERSITY OF MALAYA KUALA LUMPUR

2017

### ON THE PREVENTION OF CROSS-VM CACHE-BASED SIDE CHANNEL ATTACKS

### ZAKIRA INAYAT

### THESIS SUBMITTED IN THE FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

### FACULTY OF COMPUTER SCIENCE AND INFORMATION TECHNOLOGY UNIVERSITY OF MALAYA KUALA LUMPUR

2017

### UNIVERSITY OF MALAYA

### **ORIGINAL LITERARY WORK DECLARATION**

Name of Candidate: Zakira Inayat

Registration/Matric No: WHA130033

Name of Degree: Doctor of Philosophy

Title of Project Paper/Research Report/Dissertation/Thesis: ("On the Prevention of

Cross-VM Cache-Based Side Channel Attacks"):

Field of Study: Information Security (Computer Science)

I do solemnly and sincerely declare that:

- (1) I am the sole author/writer of this Work;

- (2) This Work is original;

- (3) Any use of any work in which copyright exists was done by way of fair dealing and for permitted purposes and any excerpt or extract from, or reference to or reproduction of any copyright work has been disclosed expressly and sufficiently and the title of the Work and its authorship have been acknowledged in this Work;

- (4) I do not have any actual knowledge nor do I ought reasonably to know that the making of this work constitutes an infringement of any copyright work;

- (5) I hereby assign all and every rights in the copyright to this Work to the University of Malaya ("UM"), who henceforth shall be owner of the copyright in this Work and that any reproduction or use in any form or by any means whatsoever is prohibited without the written consent of UM having been first had and obtained;

- (6) I am fully aware that if in the course of making this Work I have infringed any copyright whether intentionally or otherwise, I may be subject to legal action or any other action as may be determined by UM.

Candidate's Signature Date:

Dan

Date:

Subscribed and solemnly declared before,

Witness's Signature

Name:

Designation:

# ON THE PREVENTION OF CROSS-VM CACHE-BASED SIDE CHANNEL ATTACKS

### ABSTRACT

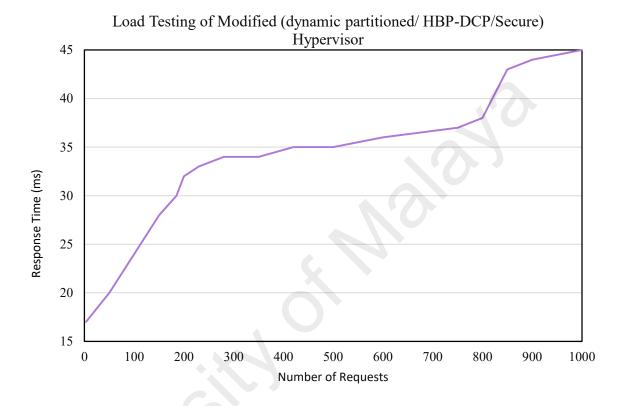

The state-of-the-art Cloud Computing (CC) has been commercially popular for shared resources of third party applications. A cloud platform enables to share resources among mutually distrusting CC clients and offers cost-effective, on-demand scaling. With the exponential growth of CC environment, vulnerabilities and their corresponding exploitation of the prevailing cloud resources may potentially increase. While it provides numerous benefits to the CC tenant, however, resource sharing and Virtual Machine (VM) physical co-residency raising the potential for sensitive information leakages such as side channel (SC) attacks. In particular, physical co-residency features allow attackers to communicate with another VM on the same physical machine and leak the confidential information due to inadequate logical isolation. We investigate SC attacks involving the CPU cache and identify that traditional prevention mechanisms for SC attacks are not appropriate for prevention of cross-VM cache-based SC attacks. We go on to demonstrate the prevention mechanisms, however, the existing prevention techniques either require the client to change the software or the underlying hardware and suffer from performance degradation leading to reduce cache usage and increase overhead. To address this problem and improve performance, we investigate that new technique such as dynamic cache partition is necessary to mitigate these sorts of attacks in a cloud environment which is hypervisor-based and does not need the client to change their software and the underlying hardware. Finally, we propose new hypervisor-based mitigation technique, implementing them in a state-of-the-art cloud system which guarantees the security and performance feature of the system. The proposed prevention mechanism is evaluated using various benchmarking experiments. The evaluation results show that merging our proposed method into hypervisor can prevent cross-VM cache-based SC attacks without affecting the performance of hypervisor. Our dynamic partitioned (HBP-DCP based) hypervisor improves the bearable load by increasing the number of request per second by 45% and by decreasing the average response time by 5.58%. Moreover, improve cache utilization that each VM has access to by increasing cache read/modify/write, cache read, and cache write bandwidth in combine by 53.5% and increasing the cache access time by 15.53%, as a result substantially increase the efficiency as significant.

Keywords: Cloud Computing, Cache-based SC Attacks, Cross-VM SC Cache-based SC Attacks, Countermeasure, Dynamic Cache Partition

# PENCEGAHAN SERANGAN SALURAN SISI BERASASKAN SILANG-VM CACHE

#### ABSTRAK

Kajian semasa dalam bidang Pengkomputeran Awan (CC) secara komersialnya telah popular dalam perkongsian sumber aplikasi pihak ketiga. Platform awan membenarkan perkongsian sumber di antara pelanggan CC yang saling tidak mempercayai dan menawarkan penskalaan yang kos efektif dan berdasarkan permintaan. Dengan pertumbuhan persekitaran CC yang pesat, kelemahan dan eksplotasi yang berkaitan antara sumber awan semasa, berpotensi boleh meningkat. Walaupun ia menyediakan pelbagai faedah kepada penyewa pengkomputeran awan, perkongsian sumber dan fizikal mesin maya (VM), ia boleh meningkatkan potensi untuk kebocoran maklumat sensitif seperti serangan saluran sisi. Secara khususnya, ciri-ciri fizikal residensi bersama membolehkan penyerang untuk berkomunikasi dengan VM lain pada mesin fizikal yang sama dan membocorkan maklumat sulit yang disebabkan oleh kekurangan pengasingan logik. Kami menyiasat tentang serangan saluran sisi yang melibatkan cache CPU dan mengenalpasti bahawa mekanisma pencegahan tradisional bagi serangan saluran sisi tidak sesuai untuk pencegahan serangan saluran sisi berasaskan silang-VM cache. Kami memilih untuk menunjukkan mekanisma pencegahan, walau bagaimanapun, teknikteknik pencegahan sedia ada sama ada memerlukan pelanggan untuk menukar perisian atau perkakasan asas akan menyebabkan kemerosotan prestasi yang boleh mengurangkan penggunaan cache dan meningkatkan overhed. Bagi menangani masalah ini dan meningkatkan prestasi, kami menyiasat teknik baru iaitu pemetakan cache secara dinamik. Ia adalah perlu untuk mengatasi serangan di dalam persekitaran awan yang berasaskan hypervisor tanpa perlu menukar perisian dan perkakasan pelanggan. Akhir sekali, kami mencadangkan mitigasi baru berasaskan hypervisor, melaksanakannya

dalam sistem awan yang mengikut aliran semasa bagi menjamin keselamatan dan ciri-ciri prestasi sistem. Mekanisma pencegahan yang dicadangkan dinilai dengan menggunakan pelbagai eksperimen penandaarasan. Keputusan penilaian menunjukkan bahawa penggabungan kaedah cadangan kami ke hypervisor boleh mencegah serangan SC berasaskan silang-VM cache tanpa menjejaskan prestasi hypervisor. Pemetakan secara dinamik (berasaskan HBP-DCP) *hypervisor* telah meningkatkan tanggungan beban dengan pertambahan jumlah permintaan setiap saat sebanyak 45% dan pengurangan purata masa respon sebanyak 5.58%. Selain itu, ia juga meningkatkan penggunaan cache di mana setiap VM mempunyai akses dan peningkatan jalur lebar bagi operasi baca/kemaskini/tulis cache sebanyak 53.5%, peningkatan masa capaian cache sebanyak 15.53% dan keputusan ini menunjukkan kecekapan meningkat secara purata.

**Keywords:** Pengkomputeran Awan, Serangan SC, Serangan saluran sisi berasaskan silang-VM cache, tindak balas, Pemetakan cache dinamik

#### ACKNOWLEDGEMENTS

ALLAH Almighty provides the courage, knowledge, and resources to every human being in this world. I am thankful to ALLAH Almighty for blessing me in every form of human quality such that I have reached this point of life and completed my PhD thesis. My hearty thanks must go to my advisors, family (Especially in Laws), and friends who have supported and encouraged me through difficult times of life. I am highly thankful to my supervisor Prof. Dr. Abdullah Gani who has patiently provided the vision, encouragement and advice necessary for me to proceed through this doctoral program and complete my PhD. I'd like also to extend my gratitude to my co-supervisor, Dr. Nor Badrul Anuar for his deep commitments and continued help and support. Their continuous support and guidance helped me producing a valuable piece of research reported in this thesis.

I would like to sincerely thank my dearest and loveliest parents for their faith in me and allowing me to be as ambitious as I wanted. I owe them everything and I hope that this work makes them proud. I would also like to gratefully express my special appreciation and thanks to my beloved husband, Rahat Ali, for his great support, encouragement and unwavering and unconditional love. Words cannot express how grateful I am to my dearest brother Shahid Anwar for his great support. He had always been a tremendous mentor for me.

Finally, I would like to thank the Malaysian Ministry of Higher Education, Malaysia for the financial support and assistance of the entire period of my PhD. I am also thankful to FSKTM support staff at WISMA RND and University for lending their support and resources. I dedicate this thesis to my beloved parents and husband for their constant support and unconditional love, who believes in me under any circumstances, cheers on my trivial achievements, and always stands beside me in the face of difficulties.

vii

### **TABLE OF CONTENTS**

| On The Prevention Of Cross-Vm Cache-Based Side Channel Attacks | III  |

|----------------------------------------------------------------|------|

| Pencegahan Serangan Saluran Sisi Berasaskan Silang-Vm Cache    | V    |

| Acknowledgements                                               | VII  |

| Table Of Contents                                              | VIII |

| List Of Figures                                                | XIII |

| List Of Tables                                                 | XVI  |

| List Of Symbols And Abbreviations                              | XIX  |

| CHAPTER 1: INTRODUCTION                                        |      |

|                                                                |      |

| 1.1 Background                                                 | 1    |

| 1.2 Motivation                                                 | 5    |

| 1.3 Statement of the Problem                                   | 8    |

| 1.4 Statement of Objectives                                    | 10   |

|                                                                |      |

| 1.5 Research Methodology                                       | 11   |

| 1.6 Thesis Layout                                              | 14   |

| CHAPTER 2: LITERATURE REVIEW                                   | 17   |

| 2.1 Background                                                 |      |

| 2.1.1 Cloud Computing                                          |      |

| 2.1.1.1 Virtualization                                         |      |

| 2.1.1.2 Cloud Model                                            |      |

| 2.1.2 Side Channel Attacks                                     | 22   |

| 2.1.3 Taxonomy of Side Channel Attacks                         | 24   |

| 2.1.3.1 Side Channel Attacks based on the Computing Location   | 24   |

| (a) Intra-VM Side Channel Attacks                              |      |

| (b) Cross Platform Side Channel Attacks                        |      |

| (c) Cross-VM Side Channel Attacks                              |      |

| 2.1.3.2 Side Channel Attacks based on Implementation           |      |

| (a) Sequential Side Channel Attacks                            |      |

|     |           | (b) Para        | llel Side Channel Attacks                                     | 27 |

|-----|-----------|-----------------|---------------------------------------------------------------|----|

|     |           | 2.1.3.3         | Side Channel Attacks based on the Way of Accessing the Module | 28 |

|     |           | (a) Invas       | sive/ Hardware Side Channel Attacks                           | 29 |

|     |           | (b) Non-        | invasive/ Software Side Channel Attacks                       | 29 |

|     |           | (c) Semi        | -invasive SC Attacks                                          | 30 |

| 2.2 | Cross-VN  | M Cache-based S | Side Channel Attacks                                          | 32 |

| 2.3 | Causes o  | f the Cross-VM  | Cache-based Side Channel Attacks                              | 34 |

|     | 2.3.1     | Last Level Cac  | he Memory                                                     | 35 |

|     | 2.3.2     |                 | olication                                                     |    |

|     | 2.3.3     | Big Data Dedu   | plication                                                     | 41 |

|     | 2.3.4     | Huge Pages      |                                                               | 43 |

| 2.4 | Types of  | Cross-VM Cach   | e-based Side Channel Attacks                                  | 44 |

|     | 2.4.1     | Time driven Si  | de Channel Attacks                                            | 44 |

|     | 2.4.2     | Trace–Driven S  | Side Channel Attacks                                          | 46 |

|     | 2.4.3     | Access-Driven   | Side Channel Attacks                                          | 47 |

| 2.5 | Preventio | on of Cross-VM  | Cache-based Side Channel Attacks                              | 55 |

|     | 2.5.1     | Existing Count  | ermeasures                                                    | 57 |

|     |           | 2.5.1.1         | Hardware-based Countermeasure                                 | 57 |

|     |           | 2.5.1.2         | Software-based Solutions                                      | 58 |

|     | 2.5.2     | Proposed Coun   | termeasures                                                   | 63 |

|     |           | 2.5.2.1         | Disable Huge Size Pages                                       | 63 |

|     |           | 2.5.2.2         | Cache Partition Using Cache Coloring                          | 63 |

|     |           | 2.5.2.3         | Private LLC Cache Slices                                      | 64 |

|     |           | 2.5.2.4         | Controlling Clflush Instruction                               | 64 |

|     |           | 2.5.2.5         | Preventing Page Sharing                                       | 65 |

|     |           | 2.5.2.6         | Prefetching Cache Memory                                      | 65 |

|     |           | 2.5.2.7         | Flushing Cache Memory                                         | 65 |

|     |           | 2.5.2.8         | Hardware Masking of Addresses                                 | 66 |

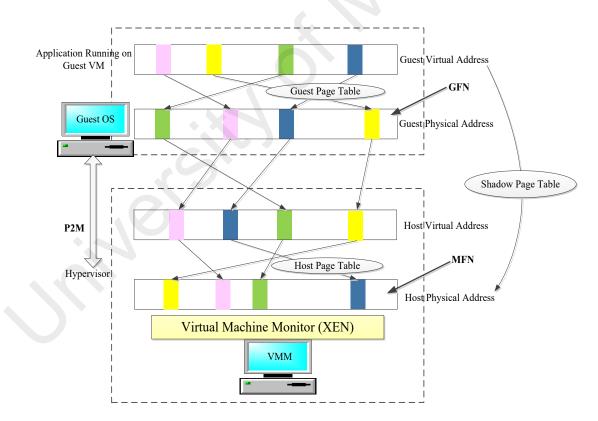

|     |           | 2.5.2.9         | Address Translation using Shadow Page Table                   | 67 |

|     |           | 2.5.2.10        | Dynamic Software Diversity                                    | 68 |

| 2.6 | Research  | Challenges      |                                                               | 68 |

|     | 2.6.1     | Efficient Cache | Utilization                                                   | 68 |

|     | 2.6.2     | Server Side Solution Transparent to Guest OS and Client Software.                    | 69    |  |

|-----|-----------|--------------------------------------------------------------------------------------|-------|--|

|     | 2.6.3     | Predicting Cache Contention6                                                         |       |  |

|     | 2.6.4     | Determining Optimal Cache Partition Policy at run time with low<br>Overhead          | 70    |  |

|     | 2.6.5     | Improving the Xen Credit Scheduler                                                   | 70    |  |

|     | 2.6.6     | Hiding Memory Access Pattern                                                         | 70    |  |

|     | 2.6.7     | Cache-Aware Scheduler for Optimum Cache Partition                                    | 71    |  |

|     | 2.6.8     | Soft Isolation as a Solution                                                         | 71    |  |

| 2.7 | Discussio | on                                                                                   | 72    |  |

| 2.8 | Conclusi  | on                                                                                   | 76    |  |

| CHA | APTER 3:  | PROBLEM ANALYSIS                                                                     | 78    |  |

| 3.1 | Experime  | ental Methodology                                                                    | 79    |  |

| 3.2 | How cac   | he based side channel attack works                                                   | 80    |  |

|     | 3.2.1     | Implementation of Cross-VM Cache-based SC Attack by using Flus<br>+ Reload technique |       |  |

|     |           | 3.2.1.1 Flush + Reload Attack Scenario                                               | 83    |  |

|     |           | (a) Flushing step                                                                    | 83    |  |

|     |           | (b) Target accessing step                                                            | 84    |  |

|     |           | (c) Reloading step                                                                   | 84    |  |

|     |           | (d) Discussion                                                                       | 84    |  |

|     | 3.2.2     | Implementation of Cross-VM cache-based SC attack by using Prime<br>+ Probe technique |       |  |

|     | 3.2.3     | Experimental Setup                                                                   | 87    |  |

|     |           | 3.2.3.1 Attack1 Setup: Attack in Native Operating System<br>and in Single VM         |       |  |

|     |           | 3.2.3.2 Attack2 Setup: Cross-VM Attacks                                              | 89    |  |

|     | 3.2.4     | Experimental Results                                                                 |       |  |

|     |           | 3.2.4.1 Result in Native Operating System                                            | 91    |  |

|     |           | 3.2.4.2 Result of Attacks in Single VM and in Cross-VM                               | 91    |  |

| 3.3 | Preventio | on Mechanism                                                                         | 94    |  |

|     | 3.3.1     | Cache Partitioning as a Prevention Mechanism                                         | 97    |  |

|     | 3.3.2     | Phoronix Test Suite                                                                  | .100  |  |

| 3.4 | Evaluatio | on Parameters                                                                        | . 100 |  |

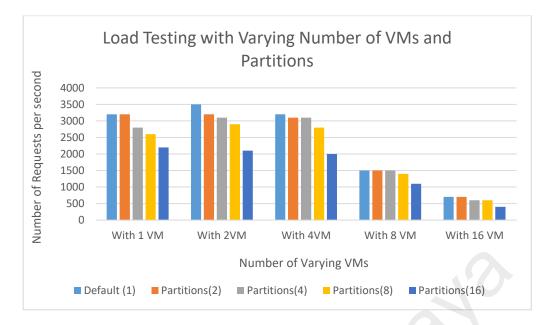

|     | 3.4.1     | Load Testing with varying numbers of VMs and Partitions101                   |

|-----|-----------|------------------------------------------------------------------------------|

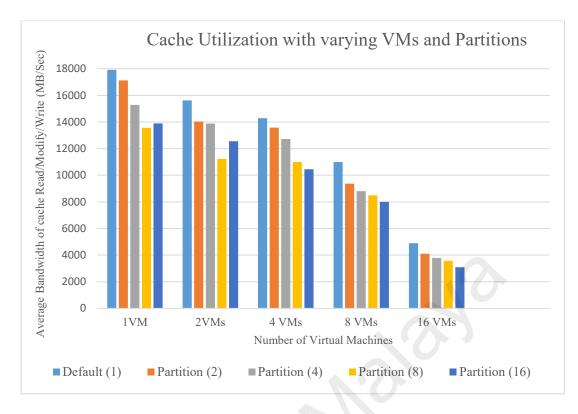

|     | 3.4.2     | Cache Utilization with varying numbers of VMs and Partitions 103             |

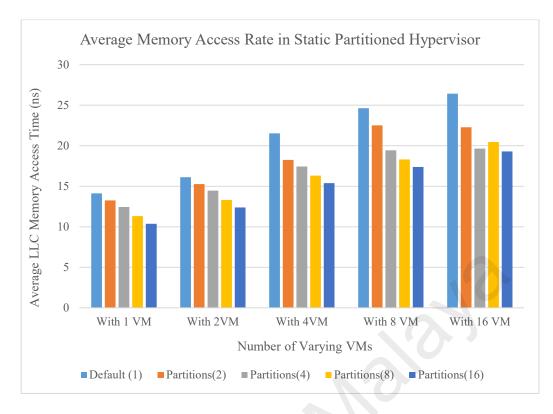

|     | 3.4.3     | Memory Access Rate with varying numbers of VMs and Partitions104             |

| 3.5 | Conclusi  | on105                                                                        |

|     |           | HYPERVISOR-BASED PREVENTION MECHANISM USING<br>ACHE PARTITIONING: HBP-DCP108 |

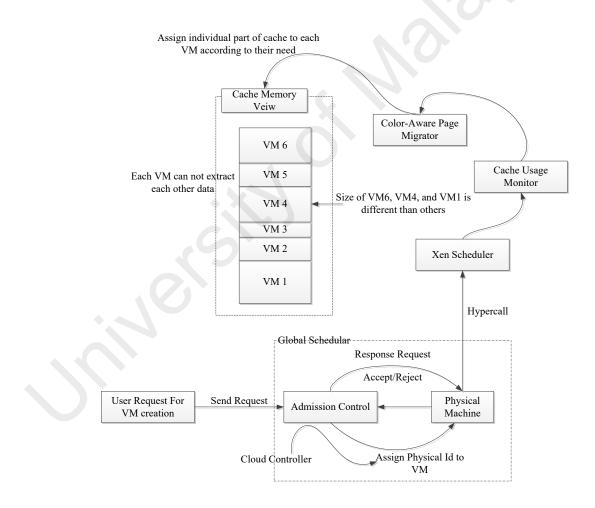

| 4.1 | Hypervis  | or-based Prevention mechanism using Dynamic Cache Partitioning 109           |

|     | 4.1.1     | Features of the Proposed HBP-DCP Prevention Mechanism109                     |

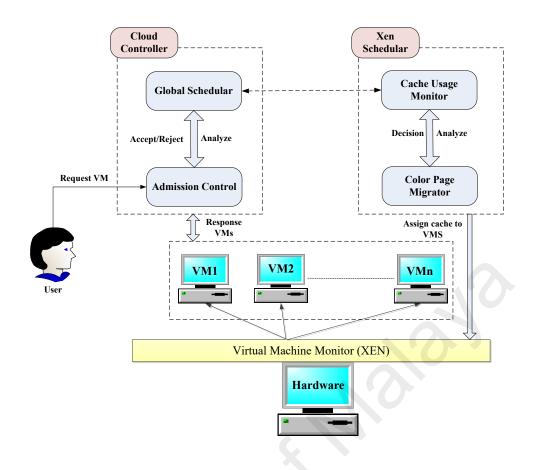

| 4.2 | System A  | Architecture                                                                 |

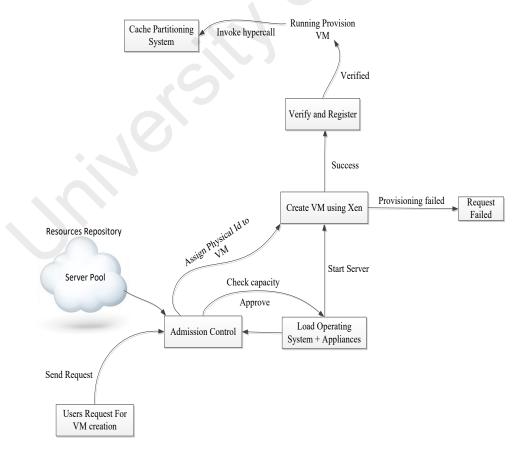

|     | 4.2.1     | Virtual Machine Provisioning113                                              |

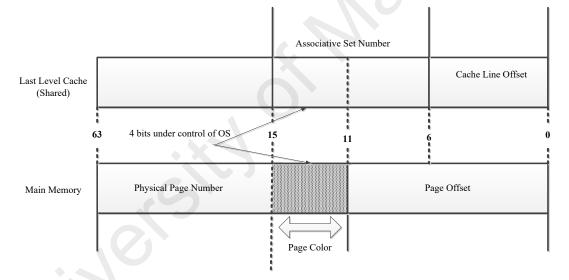

|     | 4.2.2     | Page Coloring115                                                             |

|     | 4.2.3     | Paging Mechanism in Xen Hypervisor116                                        |

| 4.3 | Compone   | ents of the Proposed HBP-PDC Prevention Mechanism                            |

|     | 4.3.1     | Server Side Admission Control                                                |

|     | 4.3.2     | Global Scheduler vs Xen Scheduler                                            |

|     | 4.3.3     | Cache Usage Monitor                                                          |

|     | 4.3.4     | Color-Aware Page Migrator                                                    |

| 4.4 | HBP-DC    | P Prevention Mechanism Algorithm126                                          |

| 4.5 | Data Des  | ign128                                                                       |

|     | 4.5.1     | Performance Evaluation Metrics129                                            |

|     |           | (a) Load Testing                                                             |

|     |           | (b) Cache Usage                                                              |

|     |           | (c) Memory Access Rate                                                       |

|     | 4.5.2     | Data Collection Tool                                                         |

|     | 4.5.3     | Performance Evaluation Method131                                             |

| 4.6 | Conclusi  | on131                                                                        |

| CHA | APTER 5:  | EVALUATION133                                                                |

| 5.1 | Evaluatio | on Process                                                                   |

|     | 5.1.1     | Experimental Setup                                                           |

| 5.1.2          | Effect of our HBP-DCP based Hypervisor on the Cross-VM SC Attack | 137 |

|----------------|------------------------------------------------------------------|-----|

| 5.2 Benchma    | ark Applications                                                 | 142 |

| 5.2.1          | Apache Benchmark                                                 | 143 |

| 5.2.2          | Cachebench Benchmark                                             | 143 |

| 5.2.3          | Cachegrind Benchmark                                             | 144 |

| 5.3 Evaluation | on methods                                                       | 14: |

| 5.3.1          | Descriptive statistics                                           | 145 |

| 5.3.2          | Confidence Interval                                              | 145 |

| 5.3.3          | Paired Samples T-Test                                            | 146 |

| 5.3.4          | Linear Regression                                                | 147 |

| 5.4 Evaluation | on Metrics                                                       |     |

| 5.4.1          | Load Testing                                                     | 148 |

| 5.4.2          | Cache Utilization                                                | 158 |

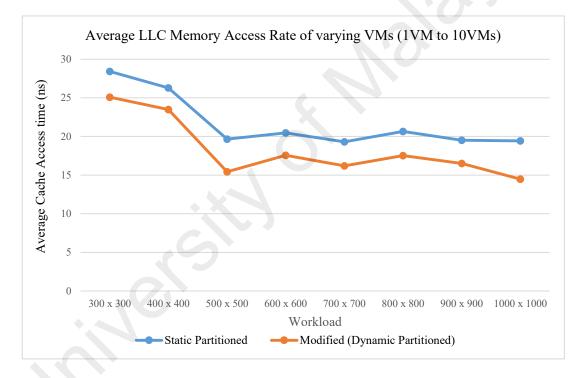

| 5.4.3          | Memory Access Rate                                               | 175 |

| 5.5 Conclusi   | on                                                               | 186 |

| CHAPTER 6:     | RESULTS AND DISCUSSION                                           | 188 |

| 6.1 Performa   | ance Evaluation Results                                          | 188 |

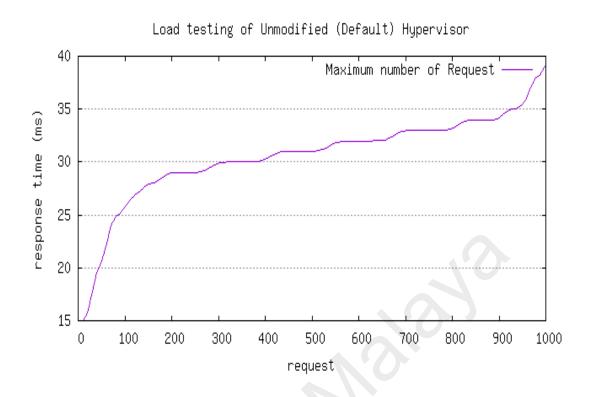

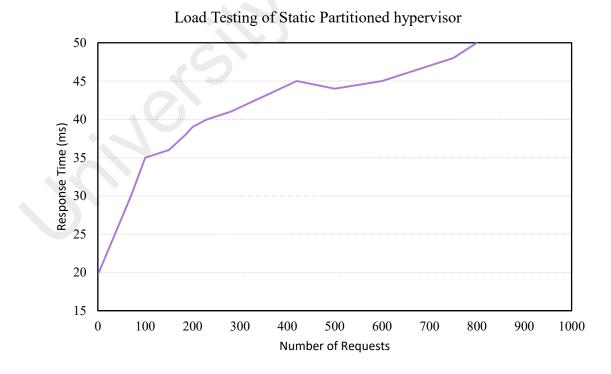

| 6.1.1          | Load Testing                                                     | 189 |

| 6.1.2          | Cache Utilization                                                | 198 |

| 6.1.3          | Memory Access Rate                                               | 204 |

| 6.2 Conclusi   | on                                                               | 212 |

| CHAPTER 7:     | CONCLUSION                                                       | 215 |

| 7.1 Research   | o Objectives                                                     | 21: |

| 7.2 Contribu   | tion                                                             | 218 |

| 7.3 Significa  | nce of the work                                                  | 22( |

| 7.4 Limitatio  | on and Future Work                                               | 22  |

|                |                                                                  |     |

| REFERENCI      | 2S                                                               | າງຈ |

### LIST OF FIGURES

| Figure 1.1: Year wise Progression of Cloud Computing Usage (Irazoqui, Inci et al. 2014)                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Research Methodology12                                                                                                            |

| Figure 1.3: Summary of Chapters Presented in this Thesis16                                                                                    |

| Figure 2.1: Layered Model of Cloud Computing19                                                                                                |

| Figure 2.2: Virtualization                                                                                                                    |

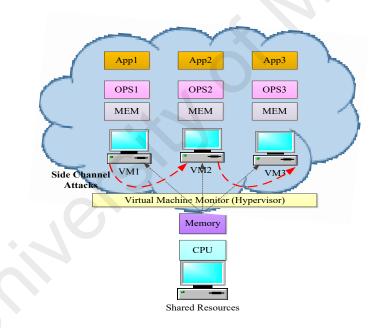

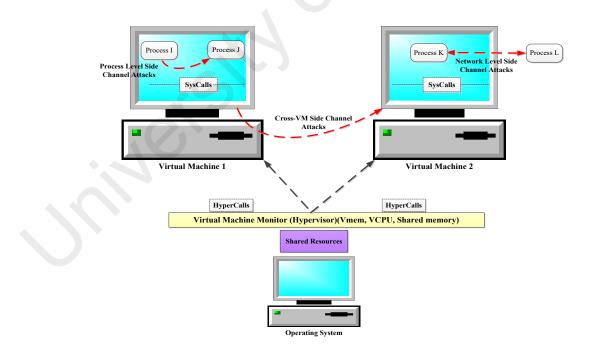

| Figure 2.3: Types of Side Channel Attack in Hypervisors (XEN)                                                                                 |

| Figure 2.4: Taxonomy of Side Channel Attacks                                                                                                  |

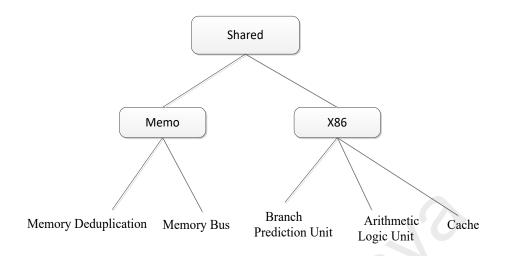

| Figure 2.5: Sources of Information Leakage on Shared Hardware                                                                                 |

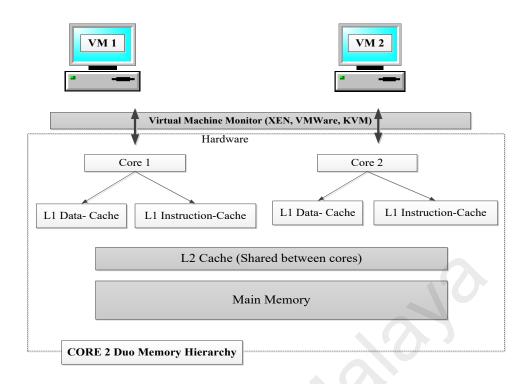

| Figure 2.6: Virtual Machine CORE 2 Duo Memory Allocation Hierarchy                                                                            |

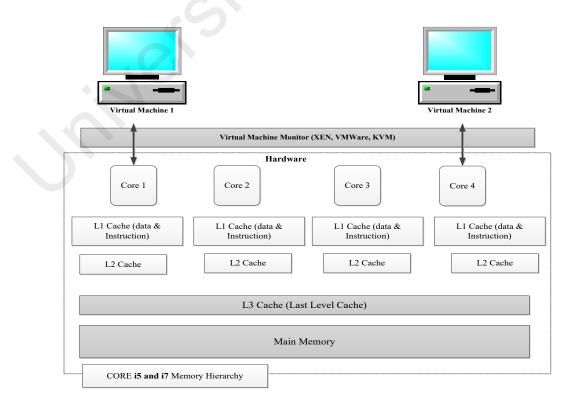

| Figure 2.7: Virtual Machine CORE i7 Memory Allocation Hierarchy                                                                               |

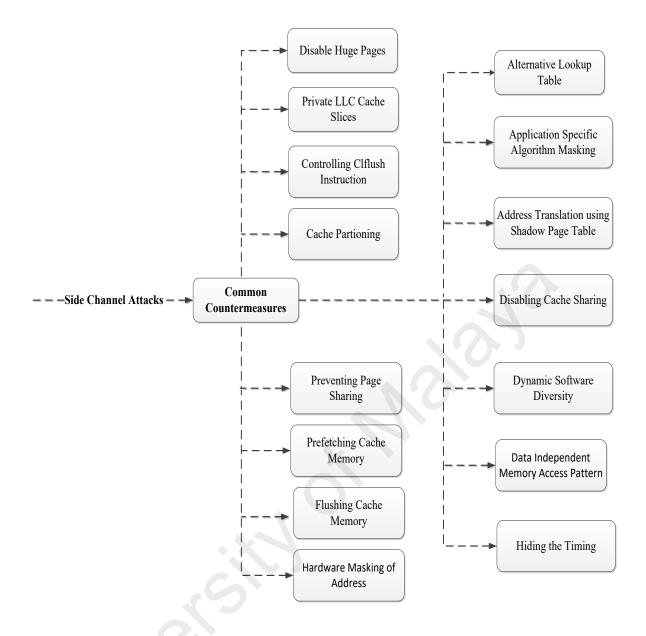

| Figure 2.8: Overview of Countermeasure for Side Channel Attacks                                                                               |

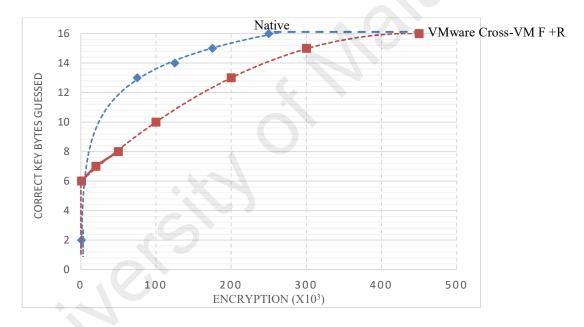

| Figure 3.1: Number of the Key Bytes of AES Key Correctly Guessed vs Number of Needed Encryption                                               |

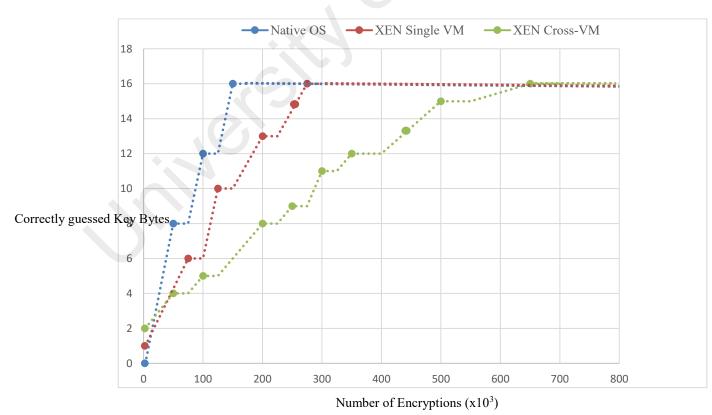

| Figure 3.2: Number of Recovered Key Bytes Correctly Guessed vs Number of Requested Encryption for Native OS, Single-VM, and Cross-VM in XEN92 |

| Figure 3.3: Problem Visualization                                                                                                             |

| Figure 3.4: Static Cache Partition Using Page Coloring                                                                                        |

| Figure 3.5: Load Testing in Static Partitioned Hypervisor with Varying Number of VMs and Partitions                                           |

| Figure 3.6: Cache Utilization with Varying Number of VMs and Partitions104                                                                    |

| Figure 3.7: Cache Access Rate in Static partitioned based Hypervisor105                                                                       |

| Figure 4.1: Proposed Hypervisor-based Prevention Mechanism Using Dynamic Cache<br>Partitioning                                                |

| Figure 4.2: Process of VM Provisioning114                                                                                                     |

| Figure 4.3: Mapping between the Physical Address and Cache Lines (Overlapped Bi are Used for Page Coloring)11                                                             |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 4.4: Paging Mechanism in Hypervisor11                                                                                                                              | 9         |

| Figure 4.5: Flow of the Prevention Mechanism Using Dynamic Cache Partitioning12                                                                                           | 28        |

| Figure 5.1: Effect of Dynamic Cache Partition on the PTP technique                                                                                                        | <u>39</u> |

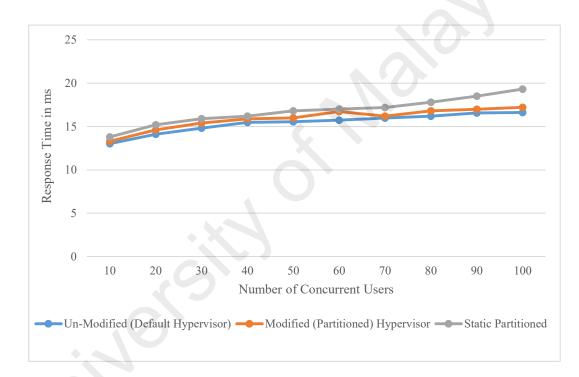

| Figure 5.2: Result of Apache Benchmark with Varying Number of Concurrent Reques                                                                                           |           |

| Figure 6.1: Load Testing of Unmodified (Default/Insecure) Hypervisor                                                                                                      | 90        |

| Figure 6.2: Load Testing of Static Partitioned Hypervisor                                                                                                                 | )0        |

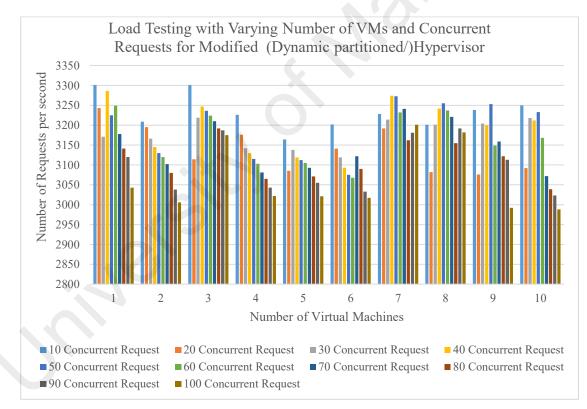

| Figure 6.3: Load Testing of Modified (Dynamic Partitioned/Secure/HBP-DCI<br>Hypervisor                                                                                    |           |

| Figure 6.4: Average Response Time for Concurrent Request without VMs for Modifie<br>(Default) and Unmodified (Dynamic Partitioned) Hypervisor                             |           |

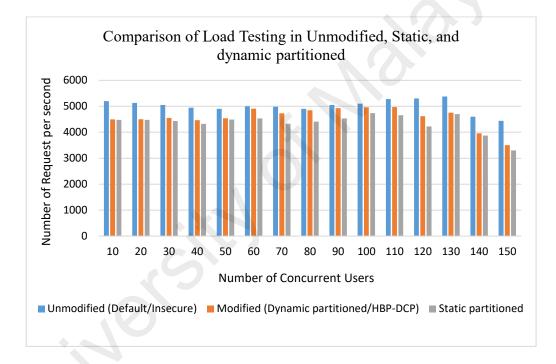

| Figure 6.5: Number of Requests per Second Time for (10-150) Concurrent Reque without VMs for both Unmodified and Modified (Partitioned) Hypervisor                        |           |

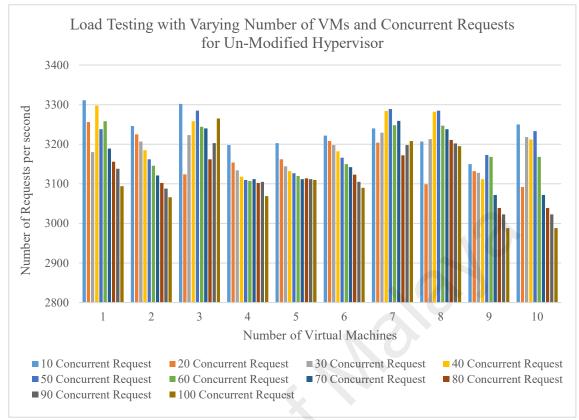

| Figure 6.6: Number of Requests per Second in Unmodified (Default) Hypervisor with Varying Number of VMs, Partitions, and Number of Concurrent Requests                    |           |

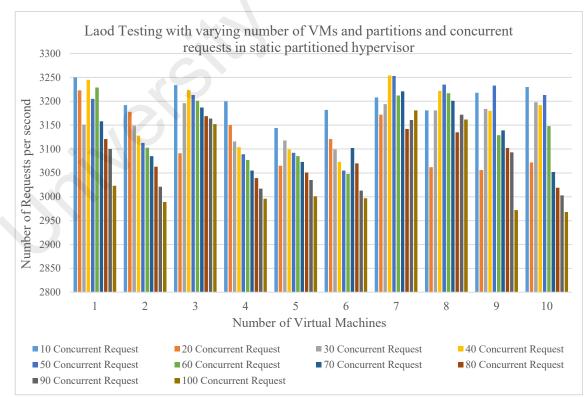

| Figure 6.7: Number of Requests per Second in Static Partitioned Hypervisor with Varyir Number of VMs, Partitions, and Number of Concurrent Requests                       | -         |

| Figure 6.8: Number of Requests per Second in Modified (Dynamic Partitioned/HBI<br>DCP) Hypervisor with Varying Number of VMs, and Number of Concurrent Reques             | sts       |

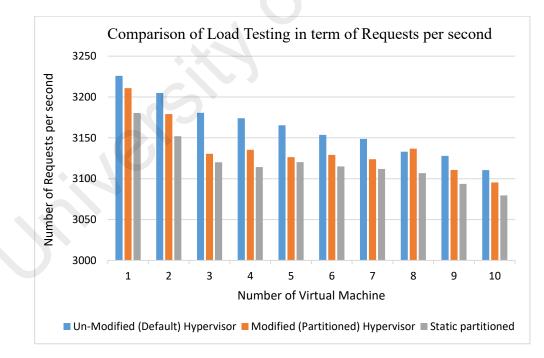

| Figure 6.9: Average Number of Request per Second with Varying Number of VMs E<br>Unmodified, Static Partitioned, and Modified (Dynamic Partitioned/HBP-DCE<br>Hypervisors | P)        |

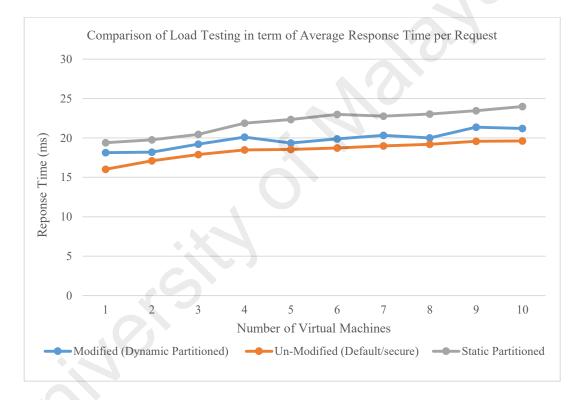

| Figure 6.10: Average Response Time for Concurrent Request with Varying Number of VMs in Unmodified (Default) and Modified (Dynamic Partitioned) Hypervisor                |           |

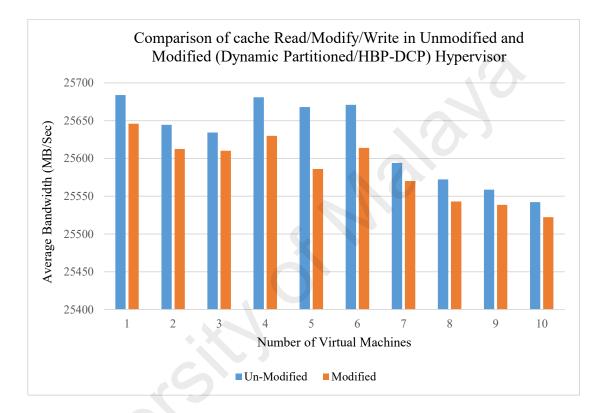

| Figure 6.11: Cache Read/Modify/Write Bandwidth in Unmodified and Modifie<br>(Dynamic Partitioned) Hypervisors                                                             |           |

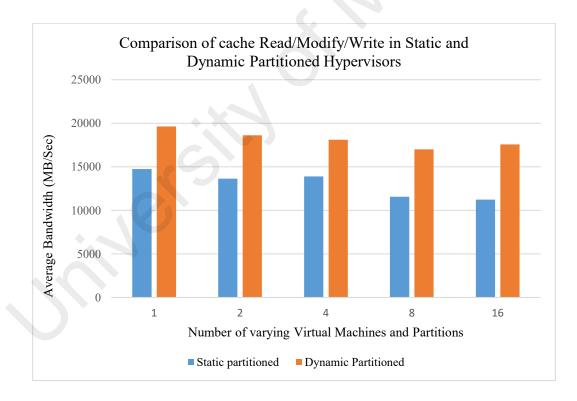

| Figure 6.12: Cache Read/Modify/Write Bandwidth in Static Partitioned and Modifie<br>(Dynamic Partitioned/HBP-DCP) Hypervisors                                             |           |

|                                                                                                                                                                           |           |

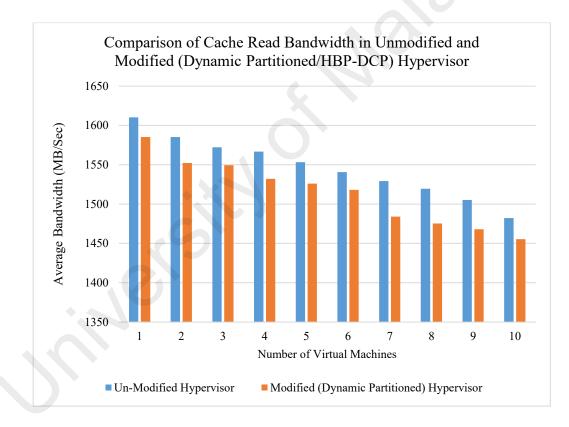

| Figure 6.13: Cache Read Bandwidth in Unmodified and Modified (Dynamic Partitioned/HBP-DCP) Hypervisor                          |

|--------------------------------------------------------------------------------------------------------------------------------|

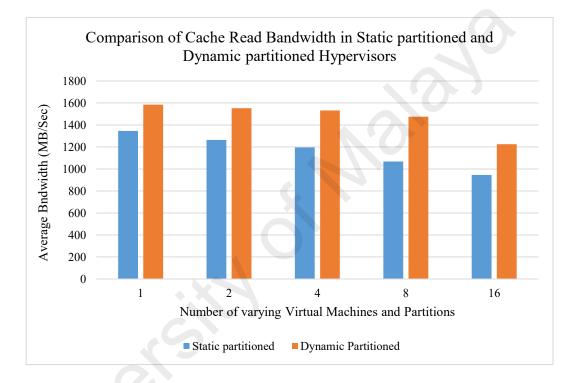

| Figure 6.14: Cache Read Bandwidth in Static Partitioned and Modified (Dynamic-Partitioned/HBP-DCP) Hypervisor                  |

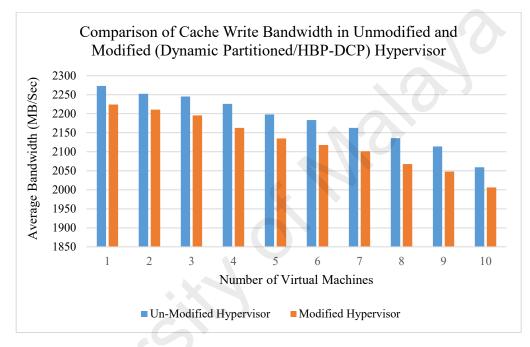

| Figure 6.15: Cache Write of Unmodified and Modified Hypervisor203                                                              |

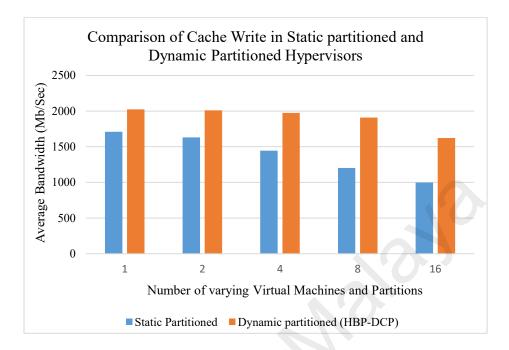

| Figure 6.16: Cache Write of Static Partitioned and Dynamic Partitioned (HBP-DCP)<br>Hypervisor                                 |

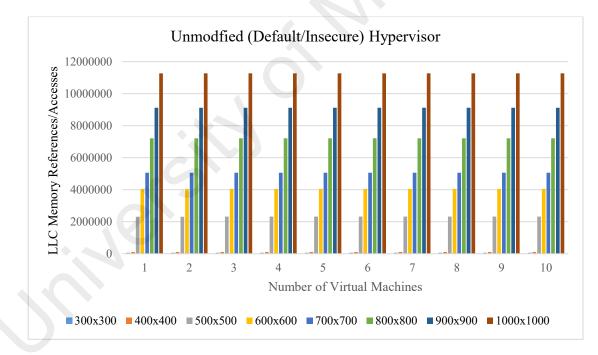

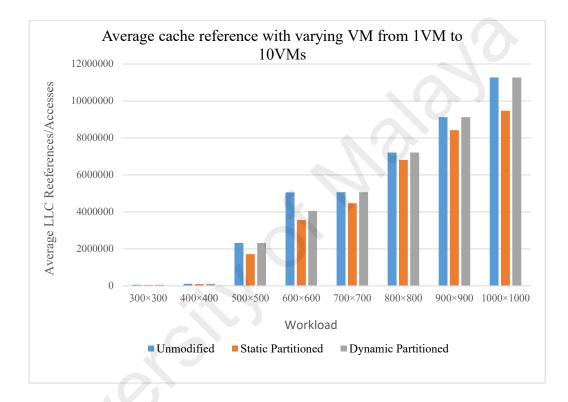

| Figure 6.17: Average LLC Memory References in Unmodified Hypervisor for Varying VMs (1VM-10VMs)                                |

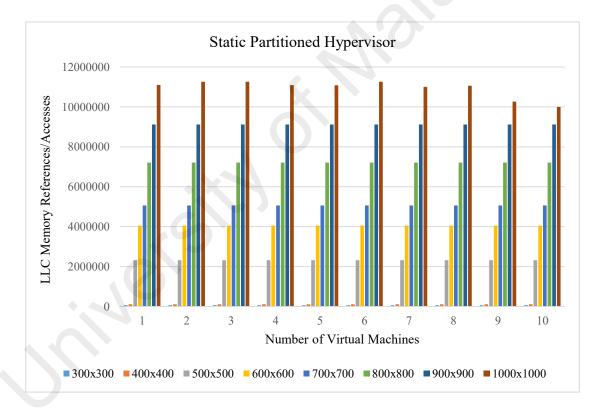

| Figure 6.18: Average LLC Memory References in Static Partitioned Hypervisor for Varying VMs (1VM-10VMs)                        |

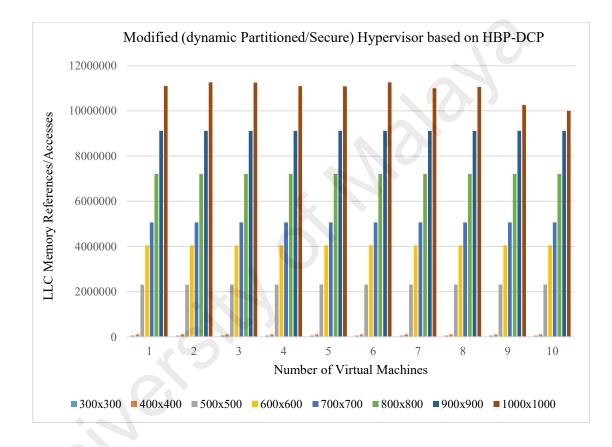

| Figure 6.19: Average LLC Memory References in HBP-DCP based Hypervisor for Varying VMs (1VM-10VMs)                             |

| Figure 6.20: Comparison of LLC Memory References in Unmodified, Static and HBP-<br>DCP based (Dynamic partitioned) Hypervisors |

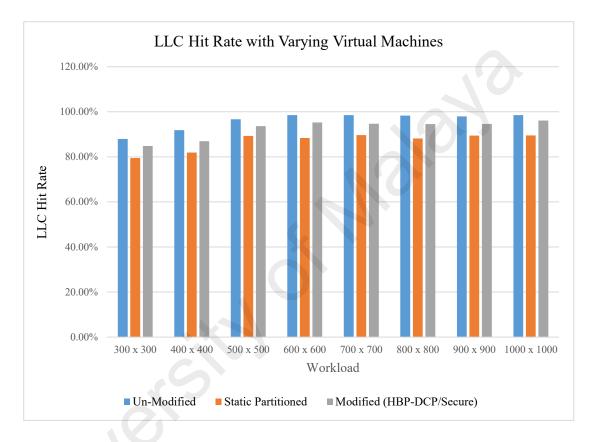

| Figure 6.21: Average LLC Memory Hit Rate with Varying VMs                                                                      |

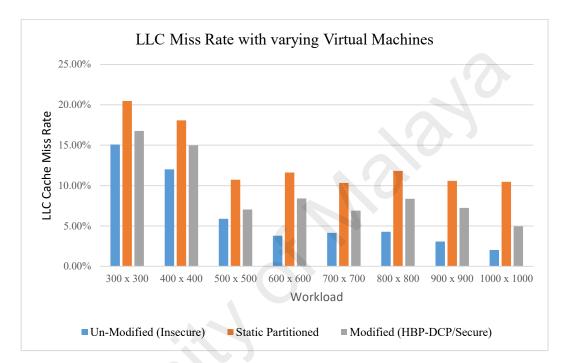

| Figure 6.22: Average LLC Memory Miss Rate with Varying VMs                                                                     |

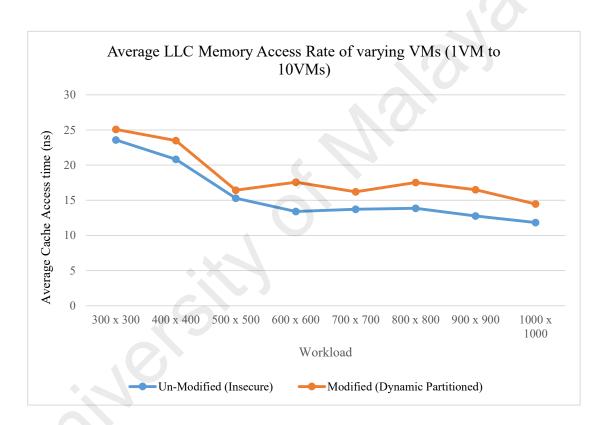

| Figure 6.23: Comparison of Average LLC Memory Access Time in both Unmodified and HBP-DCP (Dynamic Partitioned) Hypervisors     |

| Figure 6.24: Comparison of Average LLC Memory Access Time in Static Partitioned and HBP-DCP (Dynamic Partitioned) Hypervisors  |

|                                                                                                                                |

|                                                                                                                                |

|                                                                                                                                |

### LIST OF TABLES

| Table 5.10: Load Testing with Varying Number of VMs in Dynamic Partitioned         Hypervisor         155                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 5.11: Comparison of Load Testing in Static-Partitioned and Dynamic-Partitioned-<br>based Hypervisors with Varying Number of VMs and Partitions (Average for 10 to 100<br>Concurrent Request for each VM) |

| Table 5.12: Regression Statistics Summary for Load Testing of Varying VMs                                                                                                                                      |

| Table 5.13: Cache Utilization of Unmodified Hypervisor                                                                                                                                                         |

| Table 5.14: Cache Utilization of Modified Hypervisor    163                                                                                                                                                    |

| Table 5.15 Average Bandwidth (MB/Sec) of Cache Read and Cache Write of VaryingVMs (1VM-10VM) in Un-Modified and Modified Hypervisor165                                                                         |

| Table 5.16: Bandwidth of Cache Read/Write/Modify in Static Partitioned Hypervisor                                                                                                                              |

| Table 5.17: Average Bandwidth of cache Read/Modify/Write in Static and Dynamic         Partitioned Hypervisors                                                                                                 |

| Table 5.18: Average Bandwidth of Cache Read in Static and Dynamic Partitioned      Hypervisors      169                                                                                                        |

| Table 5.19: Average Bandwidth of Cache Write in Static and Dynamic Partitioned      Hypervisors      170                                                                                                       |

| Table 5.20: Comparison of cache Read/Modify/Write in Unmodified and Modified (HBP-DCP) Hypervisors                                                                                                             |

| Table 5.21: Comparison of Cache Read in Unmodified and Modified (HBP-DCP)      Hypervisor      172                                                                                                             |

| Table 5.22: Comparison of Cache Write in Unmodified and Modified (HBP-DCP)      Hypervisor      172                                                                                                            |

| Table 5.23: Regression Statistics Summary for Cache Utilization of Virtual Machines                                                                                                                            |

| Table 5.24: Last Level Cache (LLC) Memory Accesses in Unmodified Hypervisor 177                                                                                                                                |

| Table 5.25: Last Level Cache (LLC) Memory Accesses in Modified Hypervisor 177                                                                                                                                  |

| Table 5.26: Descriptive statistics of LLC Memory Accesses Data Generated by Standard         Experimentation         179                                                                                       |

| Table 5.27: Average Cache Access Rate, Cache Hit, and Miss Rate of LLC in Unmodified(Default/Insecure) Hypervisor180                  |

|---------------------------------------------------------------------------------------------------------------------------------------|

| Table 5.28: Average Cache Access Rate, Cache Hit and Miss Rate of LLC in StaticPartitioned Hypervisor (1, 2, 4, 8, and 16 partitions) |

| Table 5.29: Average Access Rate, Cache Hit, and Miss Rate of LLC Memory in Modified(Dynamic Partitioned/HBP-DCP) Hypervisor182        |

| Table 5.30: Average Cache Access Rate of Varying VMs in Unmodified and Modified      Hypervisors    183                               |

| Table 5.31: Comparison of Average Cache Access Rate of Varying VMs in Static and      Dynamic-Partitioned Hypervisors                 |

| Table 5.32: Regression Statistics Summary of Memory Access Rate for varying VMs         186                                           |

| LIST OF SYMBOLS AND A | BBREVIATIONS |

|-----------------------|--------------|

|-----------------------|--------------|

| Symbols<br>AES | Description           Advance Encryption Standard                         |

|----------------|---------------------------------------------------------------------------|

| CC             | ••                                                                        |

|                | Cloud Computing                                                           |

| CMOS           | Complementary metal–Oxide–Semiconductor                                   |

| CMP            | Chip Multi-Processing                                                     |

| Cross-VM       | Cross-Virtual Machine                                                     |

| DES            | Data Encryption Standard                                                  |

| DPA            | Differential Power Analysis                                               |

| FA             | Fault Analysis                                                            |

| HBP-DCP        | Hypervisor-based Prevention Mechanism using Dynamic<br>Cache Partitioning |

| IaaS           | Infrastructure as a Service                                               |

| IPS            | Intrusion Prevention System                                               |

| IRS            | Intrusion Response System                                                 |

| ISA            | Instruction Set Architecture                                              |

| IT             | Information Technology                                                    |

| KSM            | Kernel Same-page Merging                                                  |

| LLC            | Last Level Cache                                                          |

| MFN            | Machine Frame Number                                                      |

| OS             | Operating System                                                          |

| PaaS           | Platform as a Service                                                     |

| PFN            | Physical Frame number                                                     |

| PLcache        | Partition Locked Cache                                                    |

| RPCache        | Random Permutation Cache                                                  |

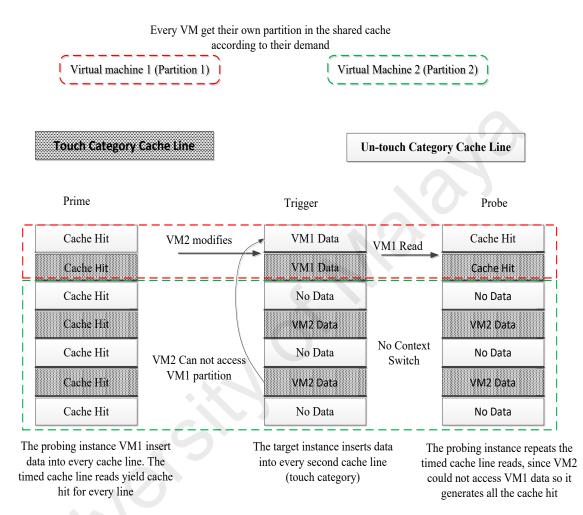

| РТР            | Prime + Trigger + Probe                                                   |

| SaaS           | Software as a Service                                                     |

| SC             | Side Channel                                                              |

| SMP            | Symmetric Multi-Processing                                                |

| SMT            | Simultaneous Multi-Threading                                              |

| SPA            | Simple Power Analysis                                                     |

| SPT            | Shadow Page Table                                                         |

| SSL            | Secure Sockets Layer                                                      |

| TLB            | Translation Lookaside Buffer                                              |

| VM             | Virtual Machine                                                           |

| VMM            | Virtual Machine Manager                                                   |

#### **CHAPTER 1: INTRODUCTION**

This chapter introduces the basis of the research work carried out in this thesis. The background of our initial research domain, Cloud Computing (CC) and Side Channel (SC) is provided. It explains the key motivations in the establishment of a research problem of the thesis leading to highlight our research problem and objectives. The research problem is highlighted from a broad perspective in the form of statements of the problem. The research aim and objectives are highlighted in the domain of side channel attacks in CC. Furthermore, the research methodology employed to address the research problem is presented.

The structure of the remainder of the chapter is as follows: Section 1.1 presents the background knowledge of the field of research namely CC, cache-based SC attack, and cross-VM SC attacks. Section 1.2 presents the motivation of inspiring the research provided in this thesis. In Section 1.3, the established research problem is presented. Section 1.4 provides the research aim and objectives. In Section 1.5, the research methodology employed to address the research problem is defined. Finally, Section 1.6 presents the layout of the rest of the thesis.

### 1.1 Background

Cloud Computing (CC) can be defined as a new paradigm that delivers computing and IT as services. The cloud resources on-demand concept has attracted end users to utilize various CC services, such as "Software, Platform, and Infrastructure" as-a-service ("SaaS, PaaS, and IaaS") at low cost (Zhang, Cheng et al. 2010). As a new paradigm, CC acquires more importance and brings unique features and vulnerabilities in today Information Technology (IT) industry. Specifically, it introduces multi-tenancy to facilitate the users to share computing physical resources provisioned over the Internet and offers cost-effective, on-demand scaling to the CC tenants. Moreover, it establishes the new concept in computing namely mutually distrusting co-resident clients as a valid execution state. Although mutually distrusting co-resident and multi-tenancy provide numerous benefits to the CC tenants, this paradigm introduces a new concept known as client's co-residence and VM's physical co-residency. However, the security vulnerabilities arise from these well-known concepts because it enables a new form of sensitive information leakage. One of the security vulnerability to CC is the SC attacks which exploit the information leakage channel at the micro-architectural level. The CC infrastructure relies on the virtualized servers that provide the required logical isolation between guest VMs through sandboxing. However, this isolation was described to be imperfect in the past research work which exploited the information leakage channel to extract the sensitive information across co-located VMs. Co-residence clients and physical co-residency of VMs allow the attacker's VM to communicate with the victim's VM running on the same physical device that by design they are unable to have access (Ristenpart, Tromer et al. 2009).

Since CC is not equivalent to physically separated systems and due to an inadequate logical isolation, it facilitates the co-located malicious VM to use the SC attacks to leak sensitive information about the victim VM functionality and exploit the correlation between the software and hardware. SC attacks use the unconventional methods including cache access and timings to extract and transfer confidential data in a way that violate security policies have been identified as a major issue in implementing cryptographic algorithms. Although cryptographic algorithms provide security to the sensitive information from attackers by encrypting and decrypting sensitive data. However, CC is a big concern for cryptographers because they are putting their data and program out there away from their trusted computers (Ristenpart, Tromer et al. 2009). The encryption keys of the cryptographic algorithms e.g., Advance Encryption Standard (AES) are extracted by the attackers using simple spying processes by the attacker to analyze information

about cache lines, which have been accessed. In addition, AES in various well known cryptographic libraries namely OpenSSL, polarssl, and libcrypto are vulnerable to information leakage attacks, when running in different hypervisors' including XEN and VMware used by cloud service providers. The current VM in the processor analyzes this cache information. Although the cache data is protected, the metadata about cache is not fully protected (Tromer, Osvik et al. 2010).

Since SC attacks are physical attacks, they require the fundamental characteristics of computation including power consumption, timings it takes to run a program and exploitation of hardware to extract the secret information of the cryptographic algorithms (e.g., encryption key). This attack typically works by creating the correlation between the functionality of the underlying hardware in the physical device and the software. Moreover, this correlation can be used to exploit the co-located VMs by interpreting the internal execution of the software program from the observed phenomena of hardware at a specified time. This allows SC attack to be conducted in an environment where the attacker and the victim have access to the same hardware in the absence of any prevention mechanism. In order to exploit the physical properties of the machine, the attacker and victim have to access the same hardware by using hardware and software SC attacks.

Although in a traditional system, gaining access to the same physical device as a target was a difficult task in establishing SC attacks. However, CC environment makes it easy to accomplish SC attacks. In a non-virtualized environment, it is difficult to launch the SC attack as compared to in a virtualized environment. This is because, in a virtualized environment, the attacker and the victim are co-located on the same physical machine. Since SC attacks are used to extract the cryptographic information, thereby, can be implemented on all those devices which used cryptography concepts for securing their data such as smart cards, mobile phones, tablets, personal computers, and servers (Fisk, Fisk et al. 2002).

SC attacks are categorized into various types according to the specific piece of hardware medium they target and exploit and have been discussed in Chapter 2 in detail. Since CPU caches are the high interacting and sharing devices between processes and are always been targeted by the adversaries. Therefore, it enables us to categorize the SC attacks in this thesis, specifically cache-based SC attacks and the prevention mechanism based on the exploited hardware medium and physical characteristics of computation.

The state-of-the-art literature shows that a large number of cache-based SC attacks have been studied in the past in non-virtualized multilevel systems including database, Operating System (OS) and networking (Zander, Armitage et al. 2007). For instance, Bernstein's proposed SC attack based on the cache access time variation (Bernstein 2004). The author used the access time information (whether the data is being accessed from the cache or from main memory) to extract AES key. Moreover, the co-residency feature of CC makes cache-based SC attacks more effective in the virtualized environment. In 2009, the first cache-based SC attack became visible in the community when Ristenpart et al. (Ristenpart, Tromer et al. 2009) successfully implemented this attack in the virtualized environment by using the co-residency feature. Because of these information leakage channels, information security in a public or shared cloud environment is a general concern that must be considered.

Since these attacks are always implemented by using the hardware or software channels, therefore, the defensive mechanisms for such attacks are also implemented on the hardware channel as well as through software (Zhang, Juels et al. 2012). Although hardware-based prevention mechanisms provide security from SC attacks, these mechanisms require changing the underlying hardware. The changing of hardware would take longer time as well as expensive and the SC attacks would be succeeded before the changing of hardware. Therefore, the software-based prevention mechanism is required which prevents the SC attacks before occurring and which is hypervisor-based that

comply with the cloud model and does not need to change the software and the underlying hardware.

#### 1.2 Motivation

CC is a rapidly growing technology in terms of both research work and commercial applications. Over the last five years, CC has grown exponentially from its origin to the existing vast research and application development industry. It is predicted that CC market will grow approximately to over \$45.90 billion by 2018. Despite the characteristics such as dynamic provisioning, multi-tenancy, scalability, and ease of integration as shown in Table 2.1 in detail, CC is vulnerable to SC attacks because of its easy accessibility and distributed infrastructure. In spite of this threat to CC, the users of the cloud are increasing day by day as shown in Figure 1.1.

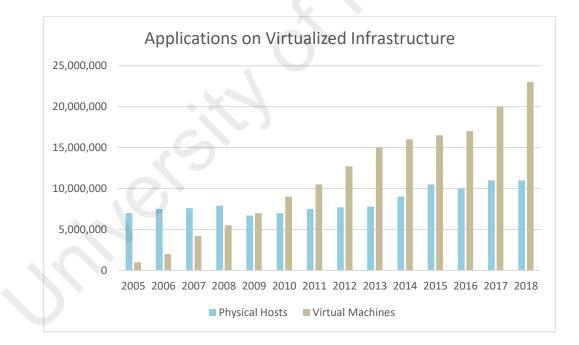

**Figure 1.1:** Year wise Progression of Cloud Computing Usage (Irazoqui, Inci et al. 2014)

Figure 1.1 shows the gradual increase from standard technology to virtualized environment. Moreover, it shows an increase in the number of cloud users compared to physical machine users. The statistic shows that from 2013 to 2017, there is approximately one billion increase in the number of online users of cloud-based service

through all over the world. The increase in cloud-based service users is estimated from the fact that in 2013 the cloud users was 2.4 billion and it is predicted that it would be approximately exceeded to 3.5 billion in 2018 (Portal 2016).

According to a recent Tech News report (NEWS 2015), Apple announced a major vulnerability to the security of iPhones that some Canadians attacked the iPhones and iPads with malware that could extract their iCloud passwords and other personal confidential data. Similarly, according to Digital Forensics Association (DFA), from 2009 to April 2016, the lost records' quantity in data breaches ranged from 1 to 140,000,000 with an average of 407,926 (DFA 2016). Even if a packets contains only single bit can be covertly transmitted , 26 GB of data could be leak on a large Internet Site through SC attacks (Zander, Armitage et al. 2007). Moreover, the CERT statistics in 2017 indicated a 50% increase in the information leakage from insider attackers and reported more than 40 % of SC attacks (Cert. 2017.). These reports prove that the effect of SC attacks are unavoidable. This is the reason that motivated researchers to explore information leakage channel namely SC attacks in cloud environment.

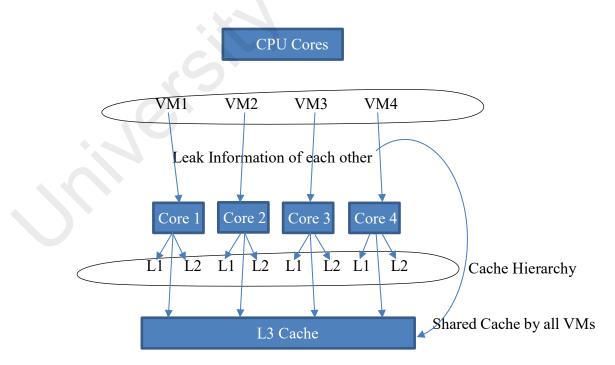

CC is a distributed computing paradigm that enables on-demand access to a shared pool of scalable computing resources. As a new design paradigm in computing, the goal of CC is computing consolidation and multi-tenancy. Multitenancy employs virtualization to share computing physical resources among CC customers. Since CC provide the logical isolation to cloud resources through sandboxing mechanism across guest VMs and does not provide the physical isolation. Therefore, data is vulnerable to information leakage due to the concept of co-residence clients and physically co-residence VMs provided by CC (Irazoqui, Eisenbarth et al. 2015). Unlike other multilevel systems (i.e., OSs, databases, networking etc.,), CC allows attackers to access the same hardware and perform malicious activities among their own users. Specifically, attackers exploit the physical characteristics of computation and hardware side-channels to access

the place such as cache that by design is restricted to them and gain the information. To limit this leakage channel, the cache must be divided across the VMs through software mechanism.

Unlike encryption, which protects confidential information from being decoded by unauthorized persons, SC attacks aim to attack the encryption systems and to hide the occurrence of communication. Since the evidence of the existence of communication is sufficient to detect the physical properties of computation. So encryption is unable to prevent attackers from detecting the pattern of communication (Zander, Armitage et al. 2007). Therefore, cloud provider, criminals, terrorist company, or government organization have the interest to hide their confidential communication.

The Cloud features affected by cross-VM SC attacks are data outsourcing, multitenancy, and co-residency. Presently, more than 79% of organizations attempt to utilize data outsourcing, because approximately 75% of the total ownership cost is assigned to manage of in-house huge storage. Since any co-resident VM can perpetrate cross-VM attacks through a covert channel. Therefore, end-users trust will be declined on cloudbased application.

Although there are several defensive mechanisms such as firewall, cryptography, and access control, however, these are unable to protect cloud environment from SC attacks. Moreover, some prevention mechanisms need to change the client software and the underlying hardware. Therefore, there is a need for a prevention mechanism for cross-VM cache-based SC attacks which is software-based and does not need to change the client software and the underlying hardware. In this thesis, the software-based prevention mechanism is proposed. Our proposed prevention mechanism for cross-VM cache-based SC attacks, need to be followed by the two key points of the cloud model. First, it does not need to modify the software on the client-end of interfaces it intends to run and second it does not require the modification of underlying hardware.

### **1.3** Statement of the Problem

Although side-channel attacks have existed in the multilevel system including databases and OSs in the past (Osvik, Shamir et al. 2006), the novel co-residency feature of CC makes them more effective in virtualized environment. Due to shared technology, the attacker is no longer required to gain unlawful or restricted access to the victim's hardware, which bypasses the first line of defense against such attacks. Because a side-channel requires the exploitation of the underlying hardware and software, each defensive mechanism must also be specifically adapted for the underlying hardware and software channel. Therefore, it enables us to categorize side-channel attacks and the defensive mechanism based on the hardware and software channel they exploit. Since each channel provides unique vulnerabilities. The CPU cache is one of the most frequently used pieces of shared hardware and often deals with sensitive data. Thus it become one of the most common targets for use in a SC attack as it can more easily be used to extract useful data at a high rate. An attack made over this channel is referred to as a cache-based SC attack.

Multiple prevention mechanisms are available to prevent cache-based SC attacks in multiprocessing systems including OS, databases, and networking. However, these existing mechanisms are unable to prevent the cross-VM cache-based SC attacks, as the cloud facilitates the users with the shared resources (Kim, Chandra et al. 2004, Percival 2005). Determined adversaries have the ability to place malicious hosts in the cloud environment on the same machine as a target host (Ristenpart, Tromer et al. 2009). The malicious hosts are then able to monitor and manipulate the shared cloud resources, including caches and other hardware resources in order to leak critical information from the target hosts. In a cloud environment, the prevention mechanisms are divided into hardware-based and software-based prevention mechanisms, and hardware-based are implemented on the hardware level (Kim, Chandra et al. 2004, Percival 2005). However, hardware based countermeasures are unable to provide an immediate solution to the

problem. They will take the time to develop and are failed to protect the existing hardware. In addition, hardware-based prevention mechanisms are expensive and need special design hardware to support cache control, or need individual cache, need to disable the cache, or need to change the replacement policy of cache (Osvik, Shamir et al. 2006). Consequently, for immediate mitigation of SC attack, software-based prevention solutions are required. Because software-based solution can be implemented in the already existed architecture. Therefore, there is a need for a software-based mechanism for the prevention of cross-VM cache-based SC attacks.

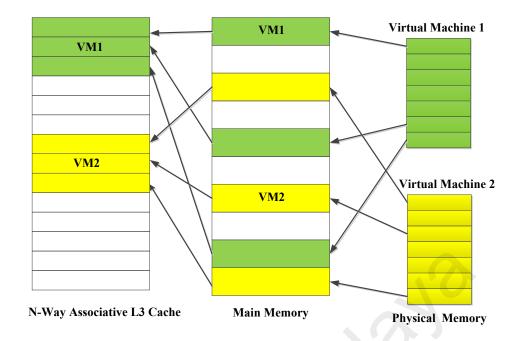

One of the software-based prevention mechanism for cross-VM cache-based SC attacks is static partition which use the page coloring technique to partition the entire cache into static parts for various VMs during boot time. Page coloring allows the hypervisor to limit the cache usage of any application and VMs. However, this method can only configure the cache usage of each virtual machines at boot time and once the VM is created we cannot change its configuration. For instance, if we partition the entire cache into 16 parts during boot time and currently one VM is executing, then only one part would be assign to that VM and the remaining 15 parts will be idle. We cannot change the entire cache partition according to running VMs during execution. Moreover, static cache partition degrades the performance in term of bearable load, cache utilization, and cache access time. The VMs are only allowed to allocate the memory at boot time from the same partition that belonging to the same VM.

Since a single VM running in a 4-way partitioned system, therefore, one-quarter of the total memory is assigned to that VM may lead to wasted resources. Consequently, the memory resources are maximized even balancing of loads. Therefore, there is a need for a preventive mechanism for SC attacks which dynamically partition the entire cache for each VM upon the creation of new VM. Once the VM is created then we would be able to configure the entire cache for various VMs. For instance, if one VM is created then the whole cache memory is assigned to that VM on a dynamic basis. If two or three VMs are created then the cache memory is divided into 2 or 3 partitions accordingly and would be assigned to those VMs. Moreover, prevention mechanism of SC attacks, need to be followed by the two key points of the cloud model. First, it does not need to modify the software on the client-end of interfaces it intends to run and second it does not need the modification of underlying hardware.

Our goal is to provide a defense capable of preventing cache-based side-channels in the Cloud while not interfering with the Cloud model and without degrading the system performance. Using the code base of an open source hypervisor, Xen (Project 2016), we have conducted our solution based on dynamic cache partition demonstrate to inhibit cache-based side-channels from occurring within a Cloud server. In our solution, all cache monitoring and cache partitioning operations are done transparently within the hypervisor or VMM. Therefore it is applicable to commodity operating systems such as Windows, of which the source code is unavailable. Second, because guest OSes are black boxes to the VMM, this single mechanism is portable across all the OSes supported by the VMM. Our solution is implemented in the hypervisor, therefore it provides cache partitioning both within and across OSes and also provides more flexibility and opportunities for the whole-system optimization.

#### **1.4 Statement of Objectives**

This research is undertaken with the aim to prevent cache-based SC attacks across VMs and in CC with minimum overhead in terms of bearable load, cache utilization, and cache access time. The research aim is accomplished by addressing the following objectives:

• To study the existing SC attacks in virtualized and non-virtualized environment involving CPU-cache to gain an insightful understanding to the performance limitations of current state-of-the-art prevention mechanisms for these attacks.

- To investigate the identified problem by conducting the cross VM cache-based SC attacks in the real environment and applied the existing prevention mechanism based on the static cache partition and unveiling the impact of existing prevention mechanism on the load, cache utilization, and cache access time as well as on the cloud model.

- To propose a prevention mechanism based on the dynamic cache partition for the prevention of cache based SC attacks across VMs that leads to an efficient cache utilization among various VMs.

- To evaluate and validate the performance of our dynamic cache based prevention mechanism considering three metrics namely: computing load, cache utilization, and memory access rate and compare it with the state-of-the-art prevention mechanisms.

#### 1.5 Research Methodology

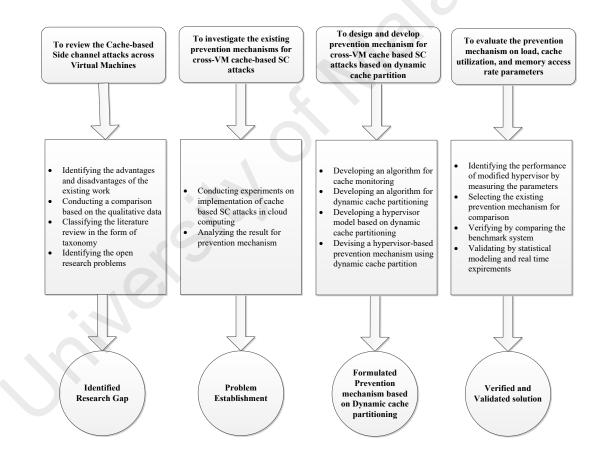

The research carried out in this thesis used the following four main steps in order to achieve the four objectives defined in Section 1.4. The proposed research methodology along with the detail description of research objectives corresponding to each research phase is given in Figure 1.2.

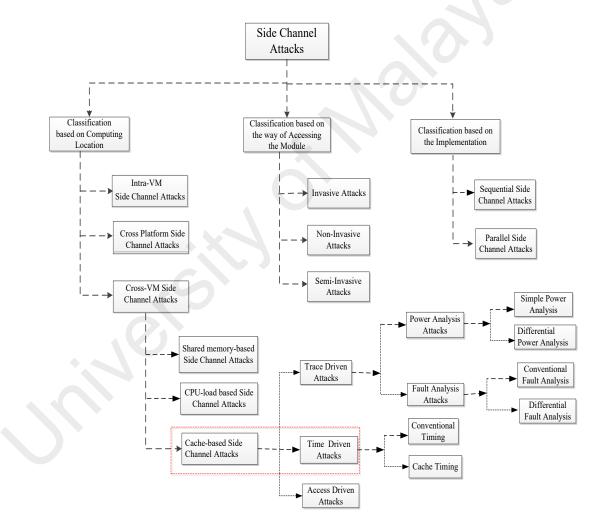

• The state of the art SC attacks in CC with emphasize on cache-based SC attacks across VMs are reviewed in the first phase. The SC attacks are generally categorized based on the computing location, on the way of implementation, and on the way of accessing the modules. Moreover, the SC attacks based on the computing location are classified into: intra-VM, cross-platform, and cross-VM SC attacks. Similarly, the SC attacks based on the implementation are divided into sequential and parallel SC attacks. In addition, the SC attacks based on the way of accessing the module is further divided into invasive, non-invasive, and semi-invasive attacks. Since all the aforementioned attacks have been discussed in the non-virtualized environment including database,

networking and OS for many years. Therefore, in this research work our focus is on the cache-based SC attacks in the virtualized environment (e.g., Cross-VM cachebased SC attacks). The aim of this thesis is to explore the SC attacks involving CPUcache and their mitigation techniques in a state-of-the-art cloud system to improve security in CC. We also categorized the cross-VM cache-based SC attacks according to the hardware medium they target and exploit, the ways they access the module and the method they use to extract the confidential information. Through a comprehensive literature review, we identify the most significant research problem to cross-VM cache-based SC attacks to address in this research.

Figure 1.2: Research Methodology

• The second phase of this research involves the investigation of the identified problem and verification of its significance through experimental analysis between two VMs using Xen hypervisor in a real CC environment. By real implementation of cachebased SC attacks between two VMs in Xen and VMWare hypervisor, we analyzed that these attacks are extracting the secret cryptographic key via cache information and are very dangerous in the virtualized environment. The static cache partition at boot time as a solution to these attacks is exercised to reveal degradation in the performance in terms of load, cache utilization, and cache access time.

- In the third phase of this research work, we implement and design HBP-DCP (Hypervisor-based Prevention Mechanism using Dynamic Cache Partitioning) prevention mechanism that prevent cross-VM cache-based SC attacks to alleviate the identified problem. HBP-DCP consists of two algorithms: one for cache monitoring and one for page allocation to each requested VMs. These algorithms are embedded into the source code of page allocator of existing hypervisor. The basic objective of cache-based SC attacks is that target VM1 traces the cache access and access time variation of the victim VM2 to extract the secret information of secret cryptographic key of the encryption algorithms (e.g., AES, DES). To prevent the cache access between VMs e.g., victim VM1 from attacker VM2, our proposed HBP-DCP prevention mechanism divide the cache into partitions on dynamic basis that no VM would access the partition assigned to another VM. In addition, it divide the cache into different color on dynamic basis and assign the specific color to each VM.

- We implemented and evaluated the performance of our proposed HBP-DCP prevention mechanism through benchmarking experiments in the last phase of our research. A set of standard computation benchmarking along with matrix multiplication and customized benchmark are used to evaluate the performance of our proposed HBP-DCP prevention mechanism. A real testbed environment is created by using Xen hypervisor. Load testing, cache utilization, and memory access rate are the performance evaluation metrics in this experiment. We synthesize the result of these three parameters using modified (dynamic partitioned /HBP-DCP/secure): the case of our solution) with the result of the unmodified (default/insecure) and the static

partitioned hypervisor. Moreover, we devised a statistical model to analyze and validate the result of performance evaluation metrics. The statistical model is devised using regression model which is a predominant observation-based modeling and analysis method. The statistical model is validated using split-sample validation approach. The empirical results of our performance evaluation are validated through the statistical regression model.

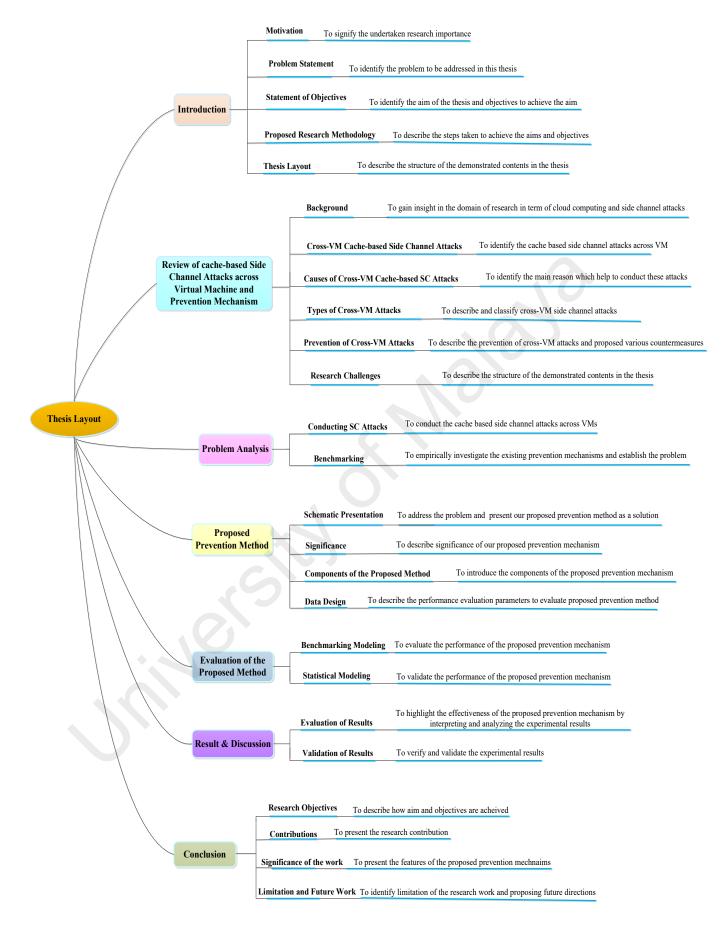

#### 1.6 Thesis Layout

The research entitled "On the prevention of cross-VM cache-based SC attacks" is comprising of an extensive study. Therefore, the thesis has been divided into chapters for a clear reader understandability. The thesis is comprised of 7 chapters and the layout of the thesis is presented in Figure 1.3.

**Chapter 2** aims to review the research undertaken in the field of cross VM cachebased SC attacks. The chapter describes knowledge about the CC and the vulnerability of SC attacks to identify and classify the SC attacks across VMs and in CC. Moreover, in this chapter, cross-VM cache-based SC attacks are focused and the detail about the prevention mechanism for these attacks are provided which discover the deficiency of the existing solution. We provide qualitative critical analysis in the aforementioned research direction based on the metrics derived from the proposed taxonomy. The research problems are identified by the literature review expose the need for the prevention mechanism based on the dynamic cache partition for the cross-VM cache-based SC attacks. Furthermore, several research issues are identified for the future research direction.

In Chapter 3, we conducted the cache-based SC attacks in the cloud environment in single VM and across VMs. Using series of experiments for conducting these attacks by using the Prime + Probe and Flush + Reload techniques in Linux and across VM, we analyzed that CC is vulnerable to the dangerous information leakage attacks.

**Chapter 4** describes HBP-DCP mechanism for the prevention of cache-based SC attacks across VM in the CC environment. The objectives and assumption undertaken by the technique are presented. Moreover, the schematic presentation of the proposed prevention mechanism is presented and each component of the technique is described in detail. The significance of the proposed technique is highlighted and the performance evaluation parameter is derived.

**Chapter 5** reports on the performance evaluation methodology for the HBP-DCP technique. The experimental setup is explained with accompanying benchmarks and the devices. The data collection method regarding the experimental and evaluation methods namely statistical modeling and benchmarking is described that have been utilized to evaluate and validate the proposed technique performance. The benchmarking application is described and the technique to evaluate the statistical modeling is also demonstrated.

In **Chapter 6**, we present the result of the experimental performance evaluation of the HBP-DCP technique to prove its efficiency and significance. The experimental evaluation is based on three parameters, namely load, cache utilization, and memory access rate. We compare and contrast the result of benchmarking with the statistical model result to validate the performance of the proposed method.

Finally, **Chapter 7** concludes this work by revisiting the aim and objective of this research that how it is fulfilled. The main contribution of the research is summarized and the significance and the method proposed in this thesis are highlighted. The future research directions and limitations conclude the chapter.

Figure 1.3: Summary of Chapters Presented in this Thesis

#### **CHAPTER 2: LITERATURE REVIEW**

This chapter presents a literature review on the cache-based cross-VM SC attacks and countermeasure for these attacks. The purpose of this chapter is to detail the literature work related to our problem domain in order to identify the potential research issues in the field of SC attacks and their countermeasures in virtualized environment. The primary research issues identified through the literature review is that with the exponential growth of CC environment, vulnerabilities and their corresponding exploitation of the prevailing cloud resources may potentially increase. CC supports multi-tenancy, physical coresidency features which enable resource sharing among mutually distrusting CC clients and offers cost-effective, on-demand scaling. Although, these features provides numerous benefits to the CC tenant, however, resource sharing and VMs physical co-residency enable a new form of sensitive information leakage such as SC attacks. Unlike encryption, which protects information from being decoded by unauthorized persons, SC attacks aim to attack the encryption systems and to hide the existence of communication. Initially, SC attacks were identified as the main threat on multi-level secure systems i.e. OS, database, and networks. More recently the focus of researchers has shifted toward SC attacks in CC. The target of this article is to explore SC attacks, especially cache-based cross-VM SC attacks and countermeasure in CC and how they compare to traditional SC attacks and countermeasure. The taxonomies are devised with reference to cache-based cross VM SC attacks and countermeasures for these attacks. Qualitative comparison of the state-ofthe-art research works is detailed in each section. The chapter also provides the basic knowledge of the technical elements found in the thesis such as cache-based SC attacks, Cross-VM cache-based SC attack, and countermeasures for these attacks.

The rest of this chapter is organized is as follows: Section 2 discusses the background detail of cache-based SC attacks and to classify the cache-based SC attacks into different

types. Section 3 describes the SC attacks in the cloud environment. Section 4 provides the prevention mechanism for cross-VM SC attacks followed by the discussion on the existing cross-VM SC attacks and proposed countermeasure. Finally, Sections 6 conclude this chapter by comparing existing approaches and providing a general design approach for prevention of SC attacks.

# 2.1 Background

This section describes the background detail about the CC, cache-based SC attacks, and previous work related to SC attacks in the cloud. It also describes techniques to implement cache-based SC attacks. Since the cloud users use the same hardware and the computational properties of hardware channel namely power consumption and time are mostly used for these types of attack. Since a cache is the most accessed hardware, most targeted hardware channel for SC attacks, therefore, this study includes a detail description of cache-based SC attacks and their typical prevention techniques.

Although there are existing surveys which explored SC attacks in detail (Osvik, Shamir et al. 2006). However, they investigated the cache-based SC attacks in the nonvirtualized environment including database, networking, and OS. To the best of our knowledge, this is the first survey which explores the cross-VM cache-based SC attacks as well as cache-based SC attacks in CC and proposed some countermeasures in the virtualized environment. The aim of this thesis is to explore the SC attacks involving CPU-cache and their mitigation techniques in a state-of-the-art cloud system to improve security in CC. We categorized the SC attacks according to the hardware medium they target and exploit, based on the ways of accessing the module and the method used to extract the confidential information. We also investigate countermeasures for their prevention, required to improve the security in CC.

### 2.1.1 Cloud Computing

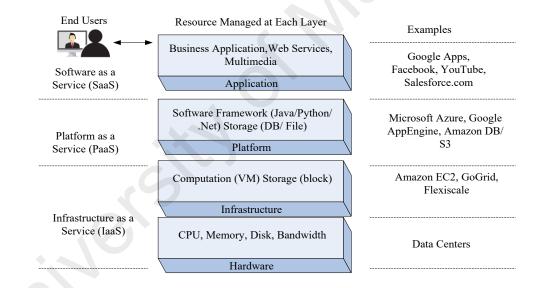

CC can be defined as a new paradigm that delivers computing and IT as a service as shown in Figure 2.1. The cloud resources on-demand concept has attracted end users to utilize various CC services, such as "Software, Platform, and Infrastructure" as-a-service ("SaaS, PaaS, and IaaS") at low cost (Zhang, Cheng et al. 2010). However, CC is a big concern for cryptographers because they are putting their data and program out there away from their trusted computers (Ristenpart, Tromer et al. 2009). Therefore, security in CC is a critical issue given the distributed infrastructure and user-friendly nature of this technology. Cyber threats to the cloud environment are different from the threats to traditional systems (Security 2010).

Figure 2.1: Layered Model of Cloud Computing

As cloud service providers offer their customer unlimited use of shared cloud resources, this makes the cloud environment vulnerable to attacks. Furthermore, CC facilitates end users with a set of API and software interfaces, opening a window for intruders. As company delivers services (SaaS, PaaS, IaaS) from cloud provider in a scalable way, they provide an opportunity for intruders to gain an inappropriate level of control over the cloud resources and this shared technology of CC enables intruders to extract information in the form of SC attacks. Table 2.1 describes the characteristics of

CC. CC introduces a multitenancy feature, however, this new concept of co-residence client and physical co-residency enables hardware and software covert and SC attacks.

| Characteristics      | Description                                                      |

|----------------------|------------------------------------------------------------------|

| Dynamic provisioning | Mobile users execute their application in a flexible way without |

|                      | any advance reservation for cloud resources                      |

| Scalability          | The deployment of mobile applications meet the unpredictable     |

|                      | demand                                                           |

| Multi-tenancy        | Multi-tenancy provides sharing technology of cloud resources     |

| Ease of integration  | Multiple cloud services from different cloud service providers   |

|                      | can be integrated to meet user demands                           |

Table 2.1: Characteristic of CC

Despite these characteristics, CC is vulnerable to SC attacks because of its easy accessibility and distributed infrastructure. Although there are several defensive techniques such as firewall, cryptography, and access control, however, are unable to protect cloud environment from SC attacks. Therefore, there is a need for a preventive mechanism for SC attacks.

# 2.1.1.1 Virtualization