# INTEGRATED VECTOR INSTRUCTION TRANSLATOR AND OFFLOADING FRAMEWORK FOR MOBILE CLOUD COMPUTING

**JUNAID SHUJA**

FACULTY OF COMPUTER SCIENCE AND INFORMATION TECHNOLOGY UNIVERSITY OF MALAYA KUALA LUMPUR

2017

# INTEGRATED VECTOR INSTRUCTION TRANSLATOR AND OFFLOADING FRAMEWORK FOR MOBILE CLOUD COMPUTING

JUNAID SHUJA

THESIS SUBMITTED IN FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

FACULTY OF COMPUTER SCIENCE AND INFORMATION TECHNOLOGY UNIVERSITY OF MALAYA KUALA LUMPUR

2017

## **UNIVERSITI MALAYA**

## **ORIGINAL LITERARY WORK DECLARATION**

Name of Candidate: Junaid Shuja

Registration/Matrix No.: WHA130039

Name of Degree: Doctor of Philosophy

Title of Thesis: Integrated Vector Instruction Translator and Offloading Framework for

Mobile Cloud Computing

Field of Study: Distributed Systems

I do solemnly and sincerely declare that:

- (1) I am the sole author/writer of this Work;

- (2) This work is original;

- (3) Any use of any work in which copyright exists was done by way of fair dealing and for permitted purposes and any excerpt or extract from, or reference to or reproduction of any copyright work has been disclosed expressly and sufficiently and the title of the Work and its authorship have been acknowledged in this Work;

- (4) I do not have any actual knowledge nor do I ought reasonably to know that the making of this work constitutes an infringement of any copyright work;

- (5) I hereby assign all and every rights in the copyright to this Work to the University of Malaya ("UM"), who henceforth shall be owner of the copyright in this Work and that any reproduction or use in any form or by any means whatsoever is prohibited without the written consent of UM having been first had and obtained;

- (6) I am fully aware that if in the course of making this Work I have infringed any copyright whether intentionally or otherwise, I may be subject to legal action or any other action as may be determined by UM.

Candidate's Signature

Date

Subscribed and solemnly declared before,

Witness's Signature

Name: Designation: Date

## ABSTRACT

Mobile Cloud Computing (MCC) facilitates energy efficient operations of mobile devices through computational offload. The mobile devices offload computations to nearby cloud servers while limiting energy consumption in the low-power wait mode. The MCC offloading frameworks are enabled by system virtualization, application virtualization, and native code migration techniques to address the heterogeneous computing architectures. The existing MCC offloading techniques suffer from either computational or communicational overheads leading to higher execution time and energy consumption on the cloud server. This research work addresses the overhead of conventional MCC offloading frameworks while focusing on vectorized applications based on Single Instruction Multiple Data (SIMD). We propose SIMDOM, a framework for SIMD instruction translation and offloading in heterogeneous MCC architectures. The SIMD translator utilizes re-compilation of SIMD instructions of the mobile device (ARM architecture) that are translated to corresponding cloud server instructions (x86 architecture). Based on inputs from the application, network, and mobile device energy profilers, the offloader module decides upon the feasibility of code offload. The SIMD translator is analyzed for its accuracy and translation overhead. The impact of code offload size, application partition, and device sleep time is investigated on the energy and time efficiency of the mobile applications. The lower feasibility bounds for server speed and application partition are derived from the system model. The SIMDOM framework prototype is implemented on a cloudlet and a cloud server. Results show that SIMDOM framework provides 85.66% energy and 3.93% time efficiency compared to MCC-disabled execution. Comparison with state-ofthe-art code offloading framework reveals that SIMDOM provides 55.99% energy and 57.30% time efficiency. The SIMDOM framework provides 31.10% higher energy efficiency while translating SIMD instructions as compared to existing MCC offloading

frameworks. The improvement in energy and time efficiency increases the usability of MCC offloading frameworks for vectorized applications.

iv

### ABSTRAK

Perkomputeran Awan Mudah-alih (MCC) memudahkan operasi cekap tenaga peranti yang bergerak melalui pengiraan penurunan. Pengiraan peranti bergerak penurunan kepada pelayan pelayan awan yang berdekatan sementara membataskan penggunaan tenaga dalam mod penantian yang berkuasa rendah. Rangka kerja penurunan MCC dibolehkan oleh system virtualisasi, aplikasi virtualisasi, dan teknik penghijrahan kod asli untuk menangani arkitektur pengkomputeran yang pelbagai. Teknik penurunan MCC yang sedia ada mengalami masalah samada dalam pengiraan atau komunikasi berlebihan yang membawa kepada masa perlaksanaan yang tinggi dan penggunaan kuasa pada pelayan awan. Kerja penyelidikan ini mengemukakan rangka kerja penurunan MCC konvensional lebihan ketika menumpukan pada aplikasi divektorkan berdasarkan Data Beberapa Arahan Dalam Satu (SIMD). Kami mencadangkan SIMDOM, satu rangka kerja bagi terjemahan arahan SIMD dan penurunan dalam seni bina MCC yang pelbagai. Penterjemah SIMD menggunakan penyusunan semula arahan-arahan SIMD dalam peranti bergerak (seni bina ARM) yang diterjemahkan untuk menjawab arahan-arahan pelayan awan (seni bina x86). Berdasarkan input dari aplikasi, rangkaian, dan tenaga peranti bergerak, modul penurunan memutuskan di atas kemungkinan kod yang menurunkan. Penterjemah SIMD dianalisa untuk ketepatan dan berlehihan terjemahan. Kesan daripada kod saiz code penurunan, menurunkan saiz, sekatan aplikasi, dan waktu tidur peranti disiasat pada kecekapan tenaga dan masa aplikasi mudah alih. Kemungkinan yang rendah sempadan dan untuk kelajuan pelayan dan sekatan aplikasi timbul dari model sistem. Keputusan menunjukkan ranga kerja SIMDOM menyediakan tenaga 85.66% dan 3.93% masa efisien dibandingkan dengan perlaksanaan MCC yang tidak digunakan. Perbandingan dengna kod penurunan rangka kerja menemukan SIMDOM menyediakan 55.99% tenaga dan 57.30% masa yang efisien. Rangka kerja SIMDOM menyediakan 31.10% tenaga efisien yang lebih tinggi

sementara menterjemahkan arahan SIMD jika dibandingkan dengan rangka kerja MCC yang sedia ada. Penambahbaikan dalam tenaga dan masa yang efisien menambahkan kepenggunaan penurunan rangka kerja MCC untuk aplikasi yang divektorkan.

#### ACKNOWLEDGEMENTS

ALLAH Almighty provides the courage, knowledge, and resources to every human being in this world. I am thankful to ALLAH Almighty for blessing me in every form of human quality such that I have reached this point of life and completed my Ph.D. thesis.

I am thankful to my supervisors, family, and friends who have supported and encouraged me through difficult times of life. I am highly thankful to my supervisor, Prof. Dr. Abdullah Gani, who took me under his guidance and provided me his support for the completion of my Ph.D. After the early struggles in my Ph.D., I knew that only one supervisor could guide me through this difficult phase of life. I am also thankful to Dr. Anjum Naveed, who provided the technical guidance and ideas that form the crux of this thesis. I was lost in ideas of mobile virtualization when Dr. Anjum advised me to work on SIMD instructions and ARM emulation for my research.

I would also like to thank my fellow lab mates from whom I have consulted on various technical issues. In particular, I would like to thank Abdullah, Wasim, and Dr. Ejaz. My family has been a source of inspiration for me. I dearly want my grandmother, mother, daughter, and wife to share the prosperous and happy days of my life with me. Through all the difficult times, I have imagined care-free days of enjoying my time with my family as an inspiration for hard work. I am also thankful for their support and prayers. My college friends have been the bond of my life. They provide me hope for future meaningful conversations and adventurous outings. I am also thankful to the FSKTM support staff at WISMA RND and University for lending their support and resources.

Last but not the least, I am thankful to the BrightSpark Program for financially supporting me throughout my Ph.D. tenure. Their strict KPI's were a blessing in disguise that enabled me to publish multiple Tier-1 articles as the first author. To my Family, especially Aqsa

## TABLE OF CONTENTS

| Abs  | stract                                                                                                              | iii      |

|------|---------------------------------------------------------------------------------------------------------------------|----------|

| Abs  | strak                                                                                                               | v        |

| Ack  | knowledgements                                                                                                      | vii      |

| Ded  | lication                                                                                                            | viii     |

| Tab  | le of Contents                                                                                                      | ix       |

| List | t of Figures                                                                                                        | xiii     |

| List | t of Tables                                                                                                         | XV       |

| List | t of Appendices                                                                                                     | xvi      |

| СН   | APTER 1: INTRODUCTION                                                                                               | 1        |

| 1.1  | Background                                                                                                          | 2        |

| 1.2  | Motivation                                                                                                          | 3        |

| 1.3  | Statement of The Problem                                                                                            | 5        |

| 1.4  | Statement of Objectives                                                                                             | 7        |

| 1.5  | Research Methodology                                                                                                | 7        |

| 1.6  | Thesis Layout                                                                                                       | 9        |

| СН   | APTER 2: OFFLOADING FRAMEWORKS IN MCC                                                                               | 13       |

| 2.1  | MCC Architecture and Computational Offload                                                                          | 14       |

|      | 2.1.1 MCC Offload Enabling Techniques                                                                               | 17       |

|      | 2.1.1.1 System Virtualization                                                                                       | 17       |

|      | 2.1.1.2 Application Virtualization                                                                                  | 18       |

|      | 2.1.1.3 Native Code Migration                                                                                       | 19       |

|      | 2.1.2 Cloud Augmentation for MCC Offloading Frameworks                                                              | 19       |

| 2.2  | MCC Offloading Frameworks                                                                                           | 21       |

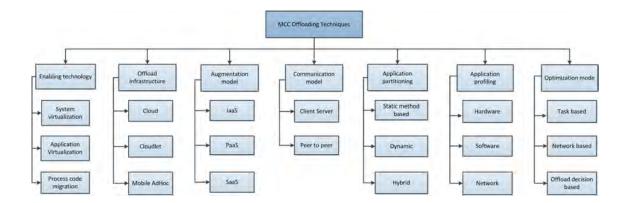

|      | 2.2.1 Taxonomy of MCC Offloading Frameworks                                                                         | 21       |

|      | 2.2.2 Review of MCC Offloading Frameworks                                                                           | 24       |

|      | 2.2.2.1 System Virtualization based MCC Frameworks                                                                  | 24       |

|      | 2.2.2.2 Application Virtualization based MCC Frameworks                                                             | 26       |

|      | 2.2.2.3 Native Code Migration based MCC Frameworks                                                                  | 28<br>29 |

| 2.3  | 2.2.3 Comparison of MCC Frameworks<br>ARM Emulation Techniques                                                      | 29<br>31 |

| 2.5  | -                                                                                                                   |          |

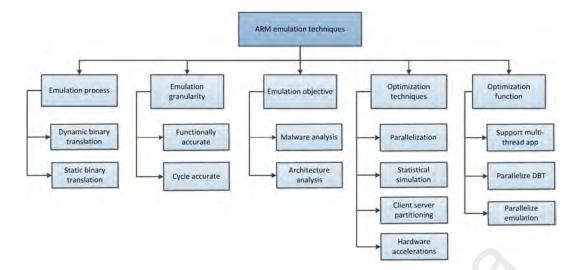

|      | <ul><li>2.3.1 Applications of ARM Emulation Techniques</li><li>2.3.2 Taxonomy of ARM Emulation Techniques</li></ul> | 32<br>33 |

|      | <ul><li>2.3.2 Taxonomy of ARM Emulation Techniques</li><li>2.3.3 Review of ARM Emulation Techniques</li></ul>       | 35       |

|      | 2.3.3 Review of ARM Emulation reeninques<br>2.3.3.1 Qemu                                                            | 35       |

|      | 2.3.3.2 Gem5                                                                                                        | 36       |

|      | 2.3.3.3 PQEMU                                                                                                       | 37       |

|      | 2.3.3.4 HQEMU                                                                                                       | 38       |

|                                               |                                            | 2.3.3.5 Trace-driven approach for gem5                                                                                                                                                                          | 39                                                 |

|-----------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                                               |                                            | 2.3.3.6 Client/server DBT                                                                                                                                                                                       | 40                                                 |

|                                               |                                            | 2.3.3.7 Retargetable Static Binary Translation                                                                                                                                                                  | 40                                                 |

|                                               | 2.3.4                                      | Comparison of ARM Emulation Techniques                                                                                                                                                                          | 41                                                 |

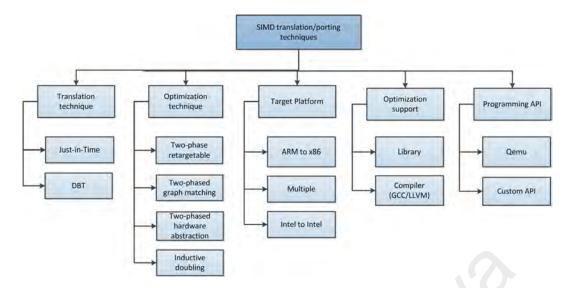

| 2.4                                           | SIMD                                       | Instruction Porting Techniques                                                                                                                                                                                  | 42                                                 |

|                                               | 2.4.1                                      | Application of SIMD Instructions                                                                                                                                                                                | 43                                                 |

|                                               | 2.4.2                                      |                                                                                                                                                                                                                 | 45                                                 |

|                                               | 2.4.3                                      | E I                                                                                                                                                                                                             | 47                                                 |

|                                               |                                            | 2.4.3.1 FREERIDER                                                                                                                                                                                               | 48                                                 |

|                                               |                                            | 2.4.3.2 IDISA+                                                                                                                                                                                                  | 48                                                 |

|                                               |                                            | 2.4.3.3 Improving SIMD Instruction Generation in DBT                                                                                                                                                            | 49                                                 |

|                                               |                                            | 2.4.3.4 Liquid SIMD                                                                                                                                                                                             | 50                                                 |

|                                               |                                            | 2.4.3.5 Optimizing DBT of SIMD                                                                                                                                                                                  | 51                                                 |

|                                               |                                            | 2.4.3.6 VaporSIMD                                                                                                                                                                                               | 51                                                 |

|                                               |                                            | 2.4.3.7 Speeding up SIMD DBT                                                                                                                                                                                    | 52                                                 |

|                                               | 2 4 4                                      | 2.4.3.8 MC2LLVM                                                                                                                                                                                                 | 53                                                 |

| 2.5                                           | 2.4.4                                      |                                                                                                                                                                                                                 | 54<br>55                                           |

| 2.3                                           |                                            | Research Issues                                                                                                                                                                                                 |                                                    |

|                                               | 2.5.1                                      |                                                                                                                                                                                                                 | 56                                                 |

|                                               | 2.5.2                                      | 6                                                                                                                                                                                                               | 57                                                 |

| 26                                            | 2.5.3                                      | 6 6                                                                                                                                                                                                             | 58                                                 |

| 2.6                                           | Conclu                                     | usion                                                                                                                                                                                                           | 59                                                 |

| CH                                            | APTER                                      | 3: PERFORMANCE ANALYSIS OF MCC OFFLOADING                                                                                                                                                                       |                                                    |

|                                               |                                            | TECHNIQUES                                                                                                                                                                                                      | 61                                                 |

| 3.1                                           | Backg                                      | round                                                                                                                                                                                                           | 62                                                 |

| 3.2                                           | Exper                                      | iments: Performance Analysis of MCC Offload Enabling Techniques                                                                                                                                                 | 63                                                 |

|                                               | 3.2.1                                      | Application Benchmarks                                                                                                                                                                                          | 64                                                 |

|                                               | 3.2.2                                      | Devices                                                                                                                                                                                                         | 66                                                 |

| 3.3                                           | Experi                                     | imental Results                                                                                                                                                                                                 | 68                                                 |

|                                               | 3.3.1                                      | System Virtualization                                                                                                                                                                                           | 68                                                 |

|                                               |                                            | 3.3.1.1 Multimedia Benchmarks                                                                                                                                                                                   | 69                                                 |

|                                               |                                            | 3.3.1.2 Phoronix Test Suite                                                                                                                                                                                     | 70                                                 |

|                                               | 3.3.2                                      | Application Virtualization                                                                                                                                                                                      | 71                                                 |

|                                               |                                            | 3.3.2.1 Multimedia Benchmark                                                                                                                                                                                    | 71                                                 |

|                                               |                                            | 3.3.2.2 Scimark Benchmark                                                                                                                                                                                       | 73                                                 |

|                                               |                                            | 3.3.2.3 Dalvik Compilation Method Optimization                                                                                                                                                                  | 74                                                 |

|                                               |                                            | · ·                                                                                                                                                                                                             |                                                    |

|                                               | 3.3.3                                      | ARM ISA Emulators                                                                                                                                                                                               | 76                                                 |

|                                               | 3.3.3                                      | ARM ISA Emulators<br>3.3.3.1 System Call Emulation                                                                                                                                                              | 76<br>76                                           |

|                                               | 3.3.3                                      | ARM ISA Emulators<br>3.3.3.1 System Call Emulation<br>3.3.3.2 Full System Emulation                                                                                                                             | 76<br>76<br>77                                     |

| 2.4                                           |                                            | ARM ISA Emulators3.3.3.1System Call Emulation3.3.3.2Full System Emulation3.3.3.3ARM to Intel Atom Emulation                                                                                                     | 76<br>76<br>77<br>79                               |

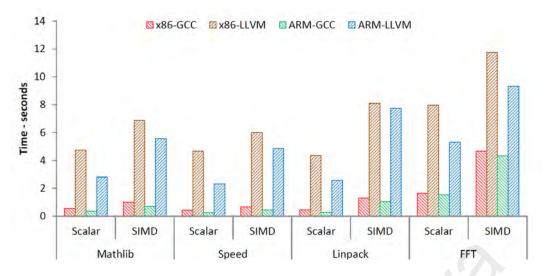

| 3.4                                           | Case f                                     | ARM ISA Emulators<br>3.3.3.1 System Call Emulation<br>3.3.3.2 Full System Emulation<br>3.3.3.3 ARM to Intel Atom Emulation<br>For SIMD Instruction Optimizations                                                | 76<br>76<br>77<br>79<br>81                         |

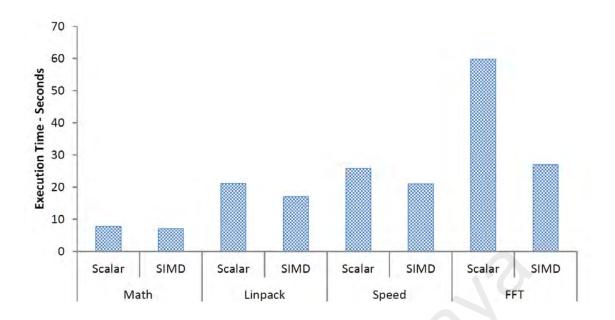

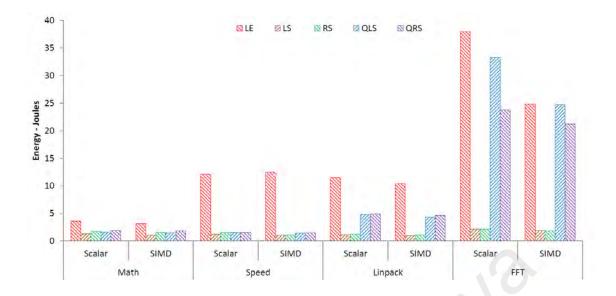

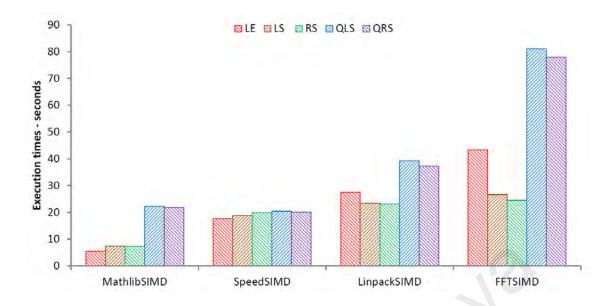

| 3.4                                           | Case f<br>3.4.1                            | ARM ISA Emulators<br>3.3.3.1 System Call Emulation<br>3.3.3.2 Full System Emulation<br>3.3.3.3 ARM to Intel Atom Emulation<br>for SIMD Instruction Optimizations<br>Mathlib                                     | 76<br>76<br>77<br>79<br>81<br>82                   |

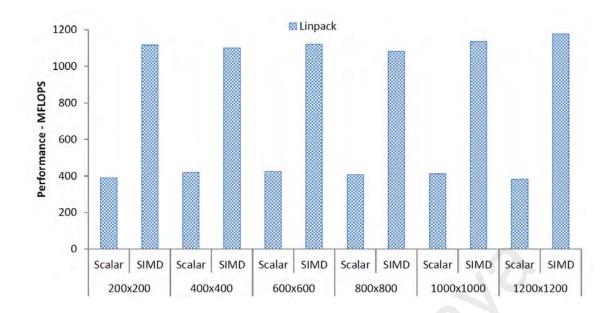

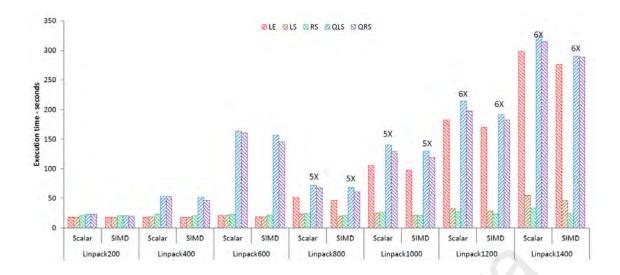

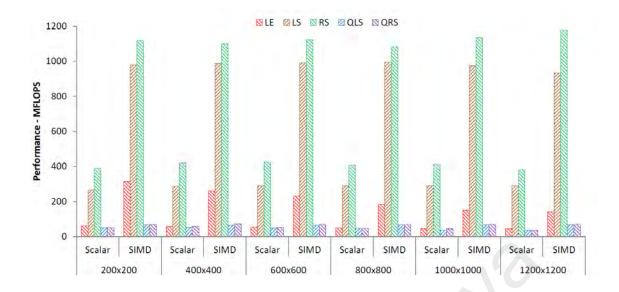

| 3.4                                           | Case f<br>3.4.1<br>3.4.2                   | ARM ISA Emulators<br>3.3.3.1 System Call Emulation<br>3.3.3.2 Full System Emulation<br>3.3.3.3 ARM to Intel Atom Emulation<br>For SIMD Instruction Optimizations<br>Mathlib<br>Linpack                          | 76<br>76<br>77<br>79<br>81<br>82<br>83             |

| 3.4                                           | Case f<br>3.4.1<br>3.4.2<br>3.4.3          | ARM ISA Emulators<br>3.3.3.1 System Call Emulation<br>3.3.3.2 Full System Emulation<br>3.3.3.3 ARM to Intel Atom Emulation<br>for SIMD Instruction Optimizations<br>Mathlib<br>Linpack<br>Speed                 | 76<br>76<br>77<br>79<br>81<br>82<br>83<br>84       |

|                                               | Case f<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4 | ARM ISA Emulators<br>3.3.3.1 System Call Emulation<br>3.3.3.2 Full System Emulation<br>3.3.3.3 ARM to Intel Atom Emulation<br>For SIMD Instruction Optimizations<br>Mathlib<br>Linpack<br>Speed<br>FFT          | 76<br>76<br>77<br>79<br>81<br>82<br>83<br>84<br>86 |

| <ul><li>3.4</li><li>3.5</li><li>3.6</li></ul> | Case f<br>3.4.1<br>3.4.2<br>3.4.3          | ARM ISA Emulators<br>3.3.3.1 System Call Emulation<br>3.3.3.2 Full System Emulation<br>3.3.3.3 ARM to Intel Atom Emulation<br>for SIMD Instruction Optimizations<br>Mathlib<br>Linpack<br>Speed<br>FFT<br>ssion | 76<br>76<br>77<br>79<br>81<br>82<br>83<br>84       |

| СН  | APTER 4: A FRAMEWORK FOR SIMD INSTRUCTION<br>TRANSLATION AND OFFLOADING IN MCC: SIMDOM | 91         |

|-----|----------------------------------------------------------------------------------------|------------|

| 4.1 | SIMDOM Framework                                                                       | 91         |

|     | 4.1.1 SIMDOM Features                                                                  | 92         |

|     | 4.1.2 System Architecture                                                              | 92         |

|     | 4.1.3 Assumptions                                                                      | 93         |

| 4.2 | Components of SIMDOM                                                                   | 94         |

|     | 4.2.1 SIMD Profiles                                                                    | 94         |

|     | 4.2.2 SIMD Translator                                                                  | 95         |

|     | 4.2.3 Application Profiler                                                             | 100        |

|     | <ul><li>4.2.4 Energy Profiler</li><li>4.2.5 Network Profiler</li></ul>                 | 102<br>103 |

|     | 4.2.6 Offload Manager                                                                  | 103        |

| 4.3 | e                                                                                      | 103        |

| 4.4 | SIMDOM Algorithm                                                                       | 108        |

| 4.5 | Conclusion                                                                             | 110        |

| СН  | APTER 5: EVALUATION                                                                    | 112        |

| 5.1 | Evaluation Process                                                                     | 112        |

|     | 5.1.1 Experimental Setup                                                               | 113        |

|     | 5.1.2 Experimental Devices                                                             | 114        |

|     | 5.1.3 Application Benchmarks                                                           | 115        |

|     | 5.1.3.1 Mathlib                                                                        | 116        |

|     | 5.1.3.2 Linpack                                                                        | 117        |

|     | 5.1.3.3 Speed<br>5.1.3.4 FFT                                                           | 117<br>117 |

| 5.2 |                                                                                        | 117        |

|     | 5.2.1 Idle Power                                                                       | 119        |

|     | 5.2.2 Computing Power                                                                  | 120        |

|     | 5.2.3 Wi-Fi Power                                                                      | 121        |

|     | 5.2.4 Wi-Fi Throughput                                                                 | 122        |

|     | 5.2.5 Application Instructions                                                         | 123        |

| 5 2 | 5.2.6 Computational Power and CPI                                                      | 124        |

| 5.3 |                                                                                        | 125        |

|     | <ul><li>5.3.1 Active Instructions</li><li>5.3.2 Semantic Accuracy</li></ul>            | 125<br>126 |

|     | 5.3.3 Overhead of SIMD Translator                                                      | 120        |

| 5.4 | Data Collection and Analysis of Application Profiler                                   | 130        |

|     | 5.4.1 Static Code Analysis                                                             | 130        |

|     | 5.4.2 Overhead of Application Profiler                                                 | 133        |

| 5.5 | Model Bounds                                                                           | 135        |

|     | 5.5.1 Bounds for Application Partitioning                                              | 135        |

|     | 5.5.2 Bounds for Server Speed                                                          | 137        |

| 5.6 | Case Studies                                                                           | 138        |

|     | 5.6.1 Case Study: System Virtualization                                                | 138        |

|     | 5.6.2 Case Study: Application Virtualization                                           | 140        |

| 5.7 | Conclusion                                                                             | 141        |

| CH         | APTER 6: RESULTS AND DISCUSSION                              |  |

|------------|--------------------------------------------------------------|--|

| 6.1        | Framework Validation                                         |  |

|            | 6.1.1 Energy                                                 |  |

|            | 6.1.2 Execution Time                                         |  |

| 6.2        | Comparison of SIMDOM for Application Benchmarks              |  |

|            | 6.2.1 Energy                                                 |  |

|            | 6.2.2 Execution Time                                         |  |

|            | 6.2.3 Performance Gain                                       |  |

| 6.3        | Comparison of SIMDOM with Qemu Offloading Framework          |  |

|            | 6.3.1 Energy                                                 |  |

|            | 6.3.1.1 Energy Distribution                                  |  |

|            | 6.3.1.2 Impact of Sleep Time                                 |  |

|            | 6.3.1.3 Impact of Application Partitioning                   |  |

|            | 6.3.1.4 Impact of Computational Size<br>6.3.2 Execution Time |  |

|            | 6.3.2.1 Time Distribution                                    |  |

|            | 6.3.2.2 Impact of Application Partitioning                   |  |

|            | 6.3.2.3 Impact of Computational Size                         |  |

|            | 6.3.3 Performance Gain                                       |  |

| 6.4        | Conclusion                                                   |  |

| CH         | APTER 7: CONCLUSION                                          |  |

| 7.1        | Research Objectives                                          |  |

| 7.2        | Contributions                                                |  |

| 7.3        | Significance of The Work                                     |  |

| 7.4        | Scope and Limitations                                        |  |

| 7.5        | Future Work                                                  |  |

| Ref        | erences                                                      |  |

| Ann        | endices                                                      |  |

| 1 <b>.</b> | churces                                                      |  |

|            |                                                              |  |

|            |                                                              |  |

|            |                                                              |  |

|            |                                                              |  |

|            |                                                              |  |

|            |                                                              |  |

|            |                                                              |  |

## LIST OF FIGURES

| Figure 1.1: | Distribution of Mobile Data Traffic Among Applications From                                                                         |     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | 2014 To 2019                                                                                                                        | 4   |

| Figure 1.2: | Proposed Research Methodology                                                                                                       | 8   |

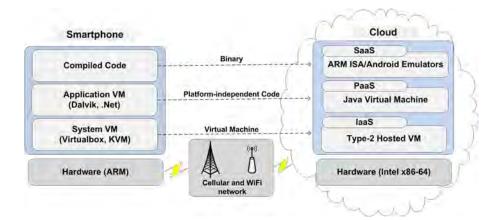

| -           | Generic Architecture of MCC Offloading                                                                                              | 15  |

| Figure 2.2: | Process Diagram of Computational Offload                                                                                            | 16  |

| -           | MCC Offload Enabling Techniques                                                                                                     | 20  |

| Figure 2.4: | Taxonomy of MCC Offloading Frameworks                                                                                               | 22  |

| Figure 2.5: | Taxonomy of ARM Emulation Techniques                                                                                                | 33  |

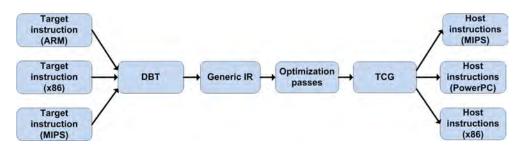

| U           | High Level Architectural Diagram of Qemu                                                                                            | 36  |

| Figure 2.7: | SIMD vs Scalar Instructions                                                                                                         | 44  |

| •           | Taxonomy of SIMD Porting Techniques                                                                                                 | 46  |

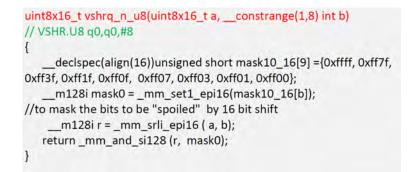

| Figure 2.9: | SIMD Code: Scalar, ARM NEON and Intel SSE Instructions                                                                              | 47  |

| -           | System Virtualization Evaluation with Multimedia Benchmarks                                                                         | 69  |

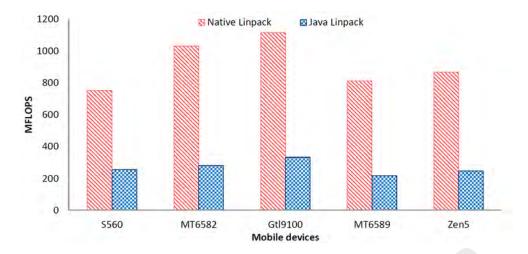

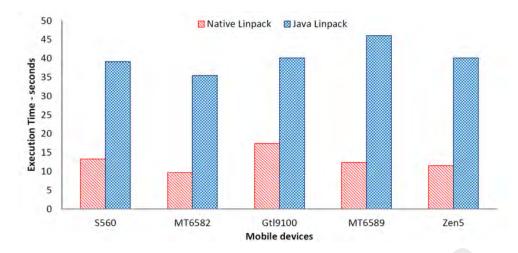

| Figure 3.2: | Application Virtualization Evaluation with Linpack: Performance in MFLOPS                                                           | 72  |

|             |                                                                                                                                     | 72  |

| -           | Application Virtualization Evaluation with Linpack: Execution Time<br>Application Virtualization Evaluation with Scimark Benchmark: | 15  |

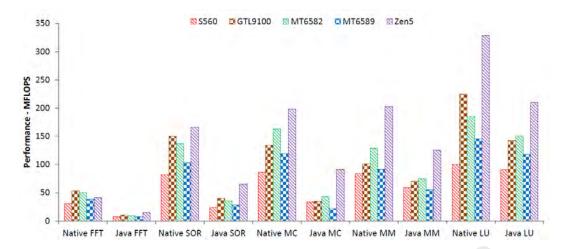

| Figure 5.4. | MFLOPS Performance                                                                                                                  | 74  |

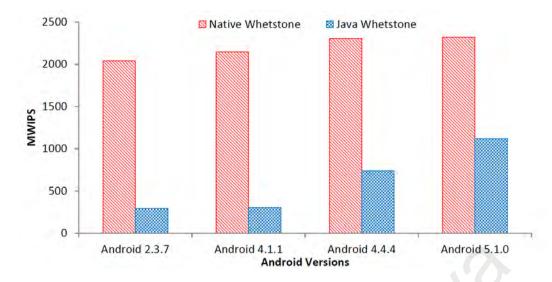

| Figure 3.5: | Java and Native C MWIPS Comparison for Upstream Android                                                                             |     |

| 0           | Versions: Performance in MWIPS                                                                                                      | 75  |

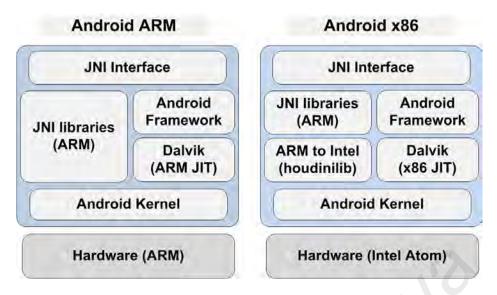

| Figure 3.6: | ARM and x86 based Android Framework                                                                                                 | 79  |

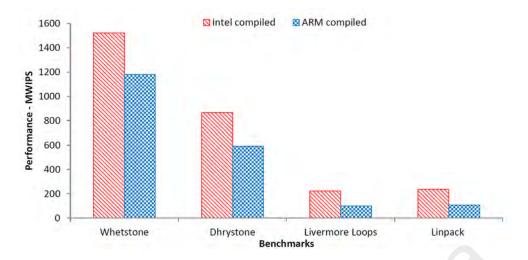

| Figure 3.7: | ARM to Intel Translation Overhead: Performance in MWIPS                                                                             | 80  |

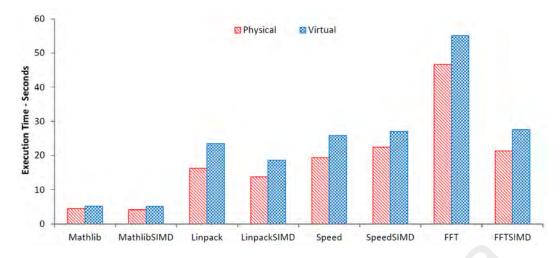

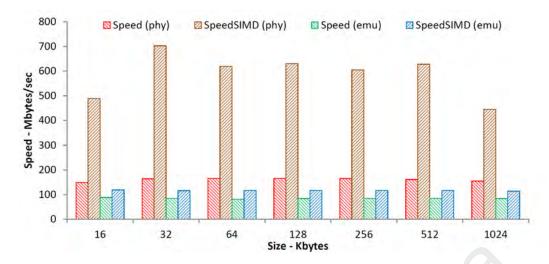

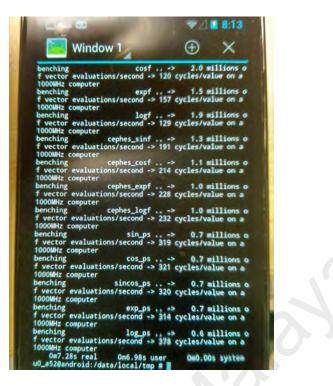

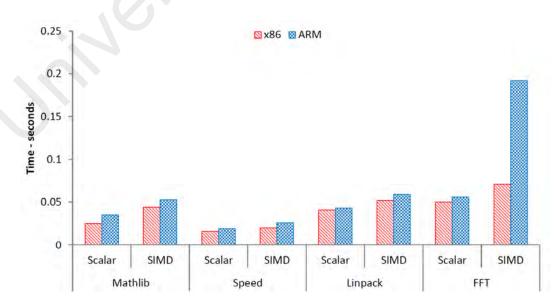

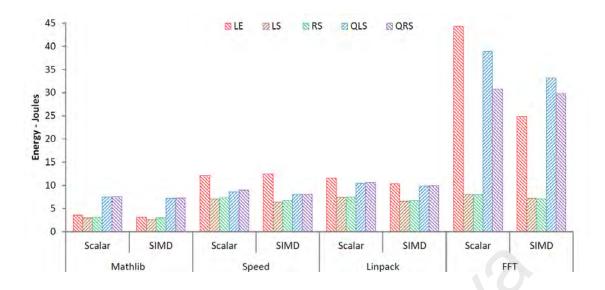

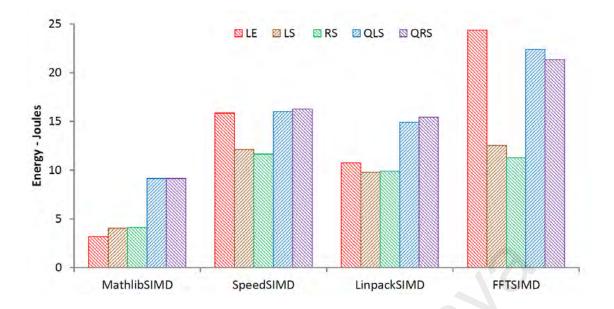

| Figure 3.8: | Speed and SpeedSIMD Comparison on Physical and Emulated Systems                                                                     | 85  |

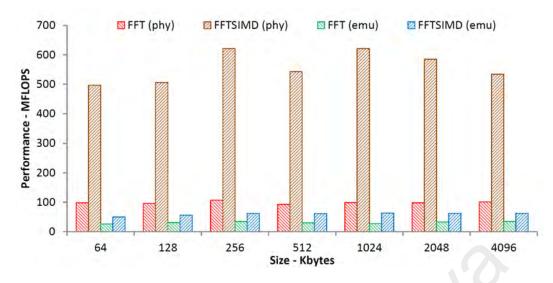

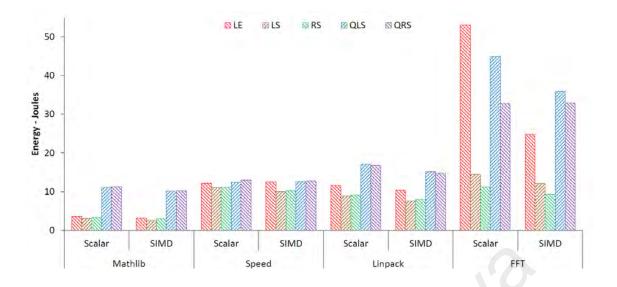

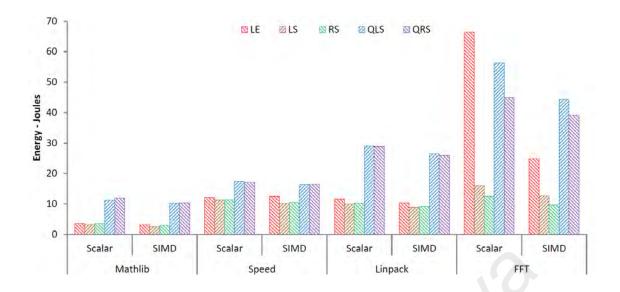

| Figure 3.9: | FFT and FFTSIMD Comparison on Physical and Emulated Systems                                                                         | 86  |

| Figure 4.1: | SIMDOM: A Framework for SIMD Instruction Based Multimedia                                                                           |     |

|             | Application Offloading in MCC                                                                                                       | 93  |

| Figure 4.2: | SIMD Translator: Sample Code for Case 1: One-to-One Vector                                                                          |     |

|             | Mapping                                                                                                                             | 98  |

| Figure 4.3: | SIMD Translator: Sample Code for Case 2: One-to-Many Vector                                                                         |     |

|             | Mapping                                                                                                                             | 99  |

| Figure 4.4: | SIMD Translator: Sample Code for Case 3: Serial Implementation                                                                      |     |

|             | with One-to-Many Vector/Scalar Mapping                                                                                              | 99  |

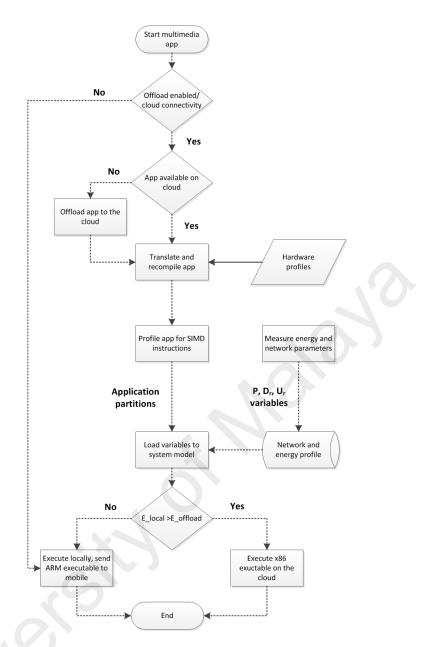

| Figure 4.5: | Flow Diagram of SIMDOM: A Framework for Pre-compiled                                                                                | 100 |

|             | Multimedia Application Offload                                                                                                      | 109 |

| Figure 5.1: | Experimental Setup for Evaluation of SIMDOM Framework                                                                               | 114 |

| Figure 5.2: | Experimental setup for measurement of energy coefficients                                                                           | 119 |

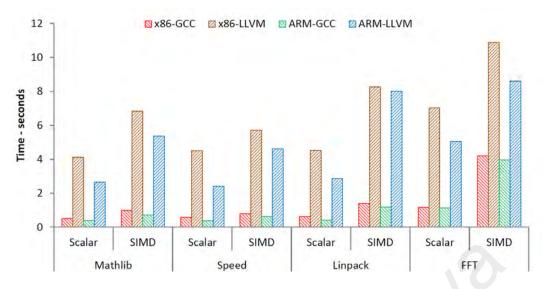

| Figure 5.3: | SIMD Translator Overhead on Cloudlet: Comparison of Compilers                                                                       | 128 |

| -           | 1 1                                                                                                                                 | 129 |

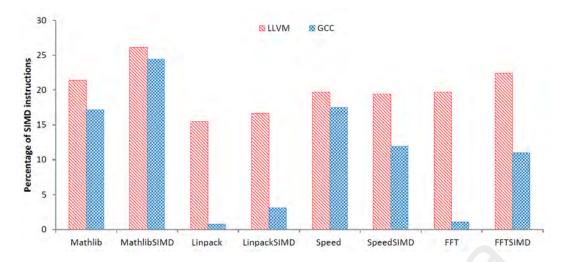

| Figure 5.5: | Analysis of ARM GCC and LLVM\Clang Compilers for                                                                                    |     |

|             | 11                                                                                                                                  | 131 |

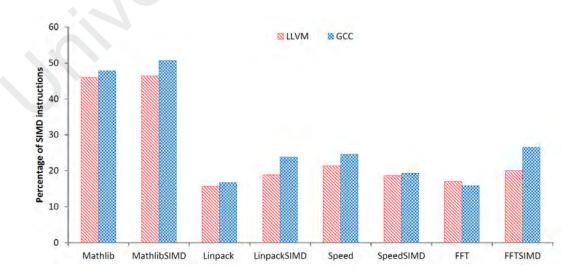

| Figure 5.6: | Analysis of x86 GCC and LLVM\Clang Compilers for                                                                                    |     |

|             | 11                                                                                                                                  | 131 |

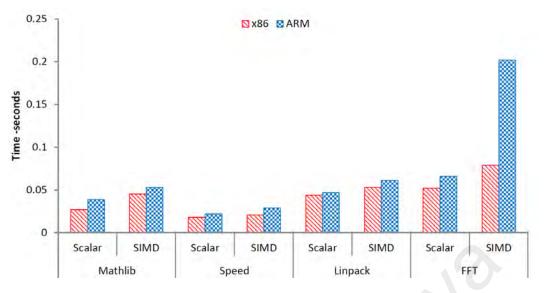

| -           | 11                                                                                                                                  | 134 |

| Figure 5.8: | Application Profiler Overhead on Cloud                                                                                              | 134 |

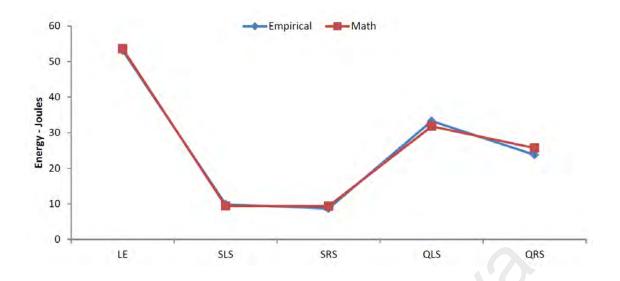

| Figure 6.1:  | Mathematical Validation of SIMDOM Framework for FFT                |        |

|--------------|--------------------------------------------------------------------|--------|

| -            | Benchmark: Energy Consumption                                      | 145    |

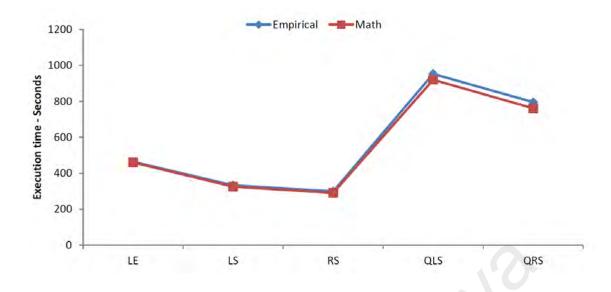

| Figure 6.2:  | Mathematical Validation of SIMDOM Framework for FFT                |        |

| e            | Benchmark: Execution Time                                          | 146    |

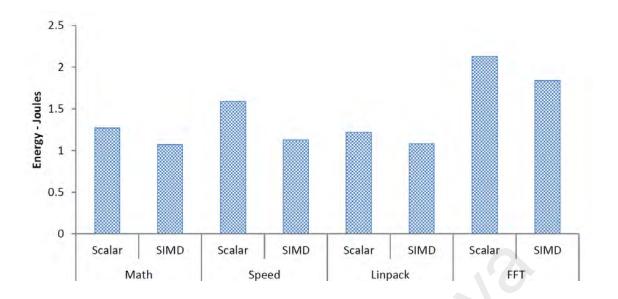

| Figure 6.3:  | Comparison of SIMDOM Framework for Application                     |        |

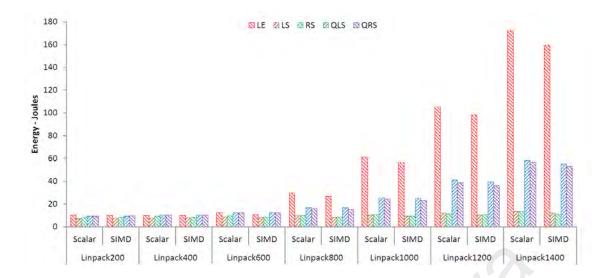

| e            | Benchmarks: Energy Consumption                                     | 148    |

| Figure 6.4:  | Comparison of SIMDOM Framework for Application                     |        |

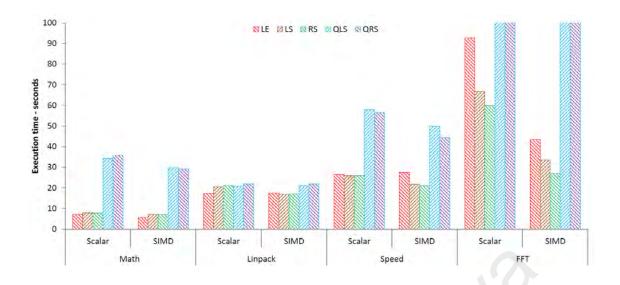

| e            | Benchmarks: Execution Time                                         | 149    |

| Figure 6.5:  | Comparison of SIMDOM Framework for Application                     |        |

| C            | Benchmarks: MFLOPS Performance                                     | 150    |

| Figure 6.6:  | Energy Consumption: LCD Sleep Time = $0$                           | 152    |

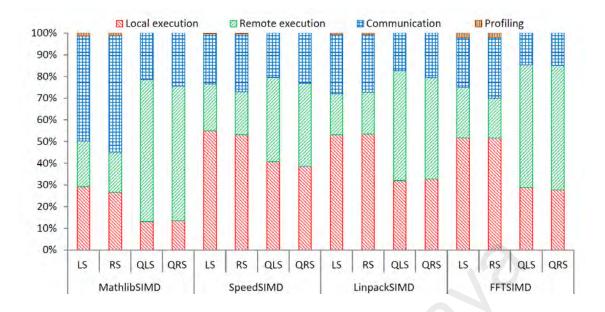

| -            | Energy Distribution: LCD Sleep Time = 0                            | 154    |

| -            | Energy Consumption: Sleep Time = 15s                               | 156    |

| -            | Energy Consumption: Sleep Time = 30s                               | 158    |

| -            | Energy Consumption: Sleep Time = 60s                               | 159    |

|              | Energy Consumption: The Case of Application Partition              | 162    |

| -            | Energy Distribution: The Case of Application Partition             | 163    |

| -            | Energy Consumption: Linpack Benchmark on Variable Input            |        |

| e            | Matrices of Size $N * N$                                           | 165    |

| Figure 6.14: | Execution Time of Evaluated Benchmark Applications                 | 166    |

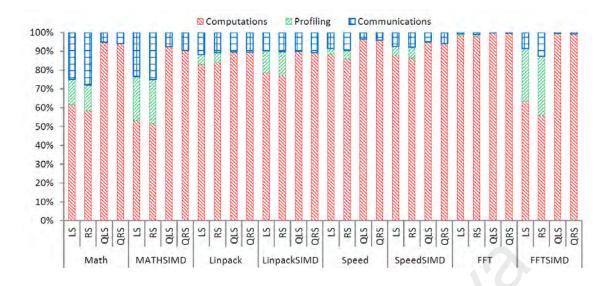

| -            | Execution Time Distribution of The Evaluated Application Benchmark | cs 169 |

| -            | Execution Time: The Case of Application Partition                  | 170    |

| -            | Execution Time of Linpack Benchmark on Variable Input Matrices     |        |

| e            | of Size N * N                                                      | 172    |

| Figure 6.18: | Performance of Linpack Benchmark on Variable Input Matrices of     |        |

| e            | Size <i>N</i> * <i>N</i>                                           | 173    |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

|              |                                                                    |        |

## LIST OF TABLES

| Table 1.1: | Thesis Layout                                                | 10  |

|------------|--------------------------------------------------------------|-----|

| Table 2.1: | Comparison of MCC Offloading Frameworks                      | 29  |

|            | Comparison of ARM Emulation Techniques                       | 41  |

| Table 2.3: | Comparison of SIMD Porting Techniques                        | 54  |

| Table 3.1: | Experimental Devices for Problem Analysis                    | 67  |

| Table 3.2  | System Virtualization Evaluation with Phoronix Test Suite    | 70  |

| Table 3.3  | System Call Emulation Performance: Execution Time            | 77  |

| Table 3.4: | Full System Emulation Performance: Execution Time            | 78  |

| Table 3.5: | Mathlib and MathlibSIMD Comparison on Physical and Emulated  |     |

|            | Systems                                                      | 82  |

| Table 3.6  | Linpack and LinpackSIMD Comparison on Physical and Emulated  |     |

|            | Systems                                                      | 83  |

| Table 4.1  | Symbol Table                                                 | 105 |

| Table 4.1  | Symbol Table                                                 | 105 |

| Table 5.1: | Experimental Devices                                         | 114 |

| Table 5.2  | Application Benchmarks                                       | 118 |

| Table 5.3: | Experimental Evaluation for $p_i$                            | 120 |

| Table 5.4: | Experimental Evaluation for $p_m$                            | 120 |

| Table 5.5: | Experimental Evaluation for $p_c$                            | 121 |

| Table 5.6  | Experimental Evaluation for RTT and Throughput               | 122 |

| Table 5.7: | Experimental Evaluation for <i>l</i>                         | 123 |

| Table 5.8: | Data Collection for SIMD Translator: ARMv-7 Active NEON      |     |

|            | Instructions                                                 | 126 |

|            | NEON Math Library: Semantic Analysis of SIMD Translator      | 127 |

| Table 5.10 | ): Energy Consumption of System Virtualization Based MCC     |     |

|            | Offloading Techniques                                        | 139 |

| Table 5.1  | : Energy Consumption of Application Virtualization Based MCC |     |

|            | Offloading Techniques                                        | 141 |

|            |                                                              |     |

|            |                                                              |     |

|            |                                                              |     |

|            |                                                              |     |

|            |                                                              |     |

|            |                                                              |     |

|            |                                                              |     |

|            |                                                              |     |

## LIST OF APPENDICES

| Appendix A: | List of Publications                               | 192 |

|-------------|----------------------------------------------------|-----|

| Appendix B: | Sample Code For Linpack and LinpackSIMD Benchmarks | 195 |

university

### **CHAPTER 1: INTRODUCTION**

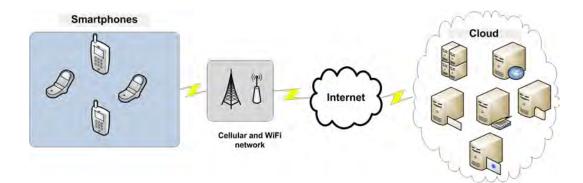

The advances in mobile devices and wireless technology have led to a paradigm shift from static computing to mobile computing. The smart mobile devices provide users with reasonable computational power within the constraints of size and battery. Smartphone users can perform tasks and execute applications on the modern mobile devices that were previously only feasible on desktop and server systems. The mobile devices still remain resource-scarce compared to server devices. The mobile devices have several communication interfaces that allow them to offload or migrate large computations to nearby cloud servers. The task offloading saves the mobile device energy and provides efficient execution time. The extension of cloud resources to the mobile device for task offloading is known as Mobile Cloud Computing (MCC).

MCC facilitates resource-scarce mobile devices to utilize resource-rich cloud server. The mobile user provides the input to the application and the rest of computations are performed on the cloud server. Meanwhile, the mobile device waits in low-power energy saving state. Mobile applications are not directly executable on the cloud servers due to the heterogeneity of computing architectures. This research work addresses the challenge of computational offload in heterogeneous MCC computing architectures.

This chapter introduces the foundations of the research work carried out in the thesis. The background of the primary research domain, MCC, is provided. Key motivations in undertaking the research problem of the thesis are described. The research problem is emphasized in the form of statements of the problem. Research aim and objectives are highlighted in the domain of MCC. Moreover, the research methodology employed to solve the research problem is presented.

The structure of the rest of the chapter is as follows. Section 1.1 provides the background knowledge of the field of research. Section 1.2 explains the motivations for inspiring the research presented in this thesis. In Section 1.3, the statement of research problem is elaborated. Section 1.4 presents the research aim and objectives. In Section 1.5, the research methodology followed to solve the research problem is defined. At last, Section 1.6 presents the layout of the rest of the thesis.

## 1.1 Background

Smartphones and mobile devices have emerged as a new computational platform over the last decade known as Mobile Computing (MC). The paradigm of MC has been possible due to rapid increase in the processing power and wireless access technology for mobile devices. Modern handheld and mobile devices, known as smartphones due to their capabilities, have equivalent processing power as some of the desktop systems. However, modern smartphones still lag behind in performance due to battery and size constraints when compared to server devices (Satyanarayanan et al., 2015).

The performance of the mobile devices can be enhanced with Mobile Cloud Computing (MCC). MCC is an operational integration of mobile and cloud computing technologies. Cloud computing offers vast resources of computation and storage that can be augmented with resource constrained smartphones (Kumar & Lu, 2010). In MCC, the majority of tasks are offloaded from the smartphone to the cloud. The cloud then performs the required computations and sends back the result to the smartphone over the communication interfaces. Mobile and cloud server hardware architectures are heterogeneous. Intel x86 based processors dominate the server market while ARM Instruction Set Architecture (ISA) based processors power 90% of smartphones (Shuja, Gani, Bilal, et al., 2016). Therefore, code offloaded from mobile device to the cloud server requires Dynamic Binary Translation (DBT) due to the heterogeneity of underlying hardware architectures. The DBT of an application translates its code from one hardware architecture to another. However, significant overhead is incurred during the process of DBT (Hsu, Hong, Hsu, Liu, & Wu, 2015). Other than DBT, system and application virtualization are also employed as MCC offload enabling techniques for heterogeneous hardware architectures (Ahmed, Gani, Sookhak, Ab Hamid, & Xia, 2015).

A number of compute-intensive applications, such as augmented reality, natural language translation, object, voice recognition, and multimedia-based software are dependent on MCC due to resource scarcity of smartphones. Popular multimedia based smartphone applications are; (a) cloud storage (store retrieve files, photos, videos e.g., Instagram, Facebook) and (b) audio video streaming e.g., YouTube, Sound-Cloud (Satyanarayanan et al., 2015).

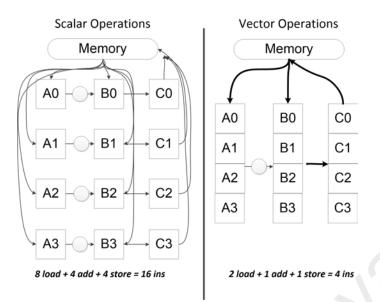

Multimedia based applications rely on Single Instruction Multiple Data (SIMD) commonly known as vector instructions. SIMD instructions are a hardware capability that allows execution of the same operation on multiple data points simultaneously. For example, the change in brightness of a picture requires retrieving of N pixels and ADD/SUB operation on the N pixels. The utilization of SIMD instructions significantly boosts the performance of applications. Up to 25-50% of the code of multimedia based applications can be SIMD instructions (Mitra, Johnston, Rendell, McCreath, & Zhou, 2013). SIMD instructions and intrinsics vary from one ISA to another. Applications programmed with SIMD instructions are not portable and executable on heterogeneous ISAs. Therefore, SIMD instruction translation techniques are required to enable vectorized multimedia applications to offload between heterogeneous MCC architectures (Manilov, Franke, Magrath, & Andrieu, 2015).

## **1.2** Motivation

MCC is a rapidly growing technology in terms of both commercial applications and research work. Over the past five years, mobile cloud computing has grown exponentially from its inception to current vast research and application development industry. It is pre-

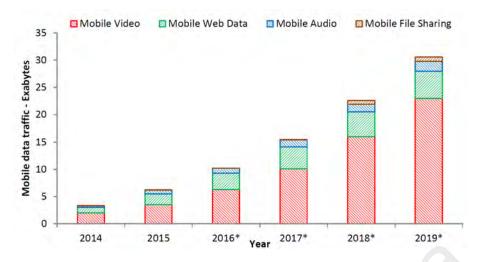

Figure 1.1: Distribution of Mobile Data Traffic Among Applications From 2014 To 2019

dicted that the mobile cloud market will grow to over \$46.90 billion by 2019. Similarly, mobile data traffic grew 74% globally in 2015. It is predicted that out of total mobile data traffic, the cloud-based traffic will increase from 81% in 2014 to 90% in 2019. It is estimated that 75% of total data accessed through the mobile networks by 2020 will be of multimedia applications (Statista, 2015; Cisco, 2015). To limit the energy consumption of increasing multimedia content on mobile devices, computational offloading techniques are unavoidable. Offloaded mobile applications execute seamlessly over the cloud servers while providing energy and execution time efficiency to the mobile users. Figure 1.1 shows the increasing multimedia content share in mobile traffic that motivates the development of computational offloading frameworks for multimedia applications.

Specialized hardware known as vector processors and corresponding instruction sets are devised to adapt to the computational demands of multimedia applications. The vector processors increase the energy consumption of mobile devices due to their data and compute intensity. Therefore, vector instructions are offloaded to the cloud server while limiting local execution on energy-constrained mobile devices. The offloading requires that vector instructions are cross-platform compatible. In reality, vector instructions are platform-dependent and vary from one ISA to another. Hence, a vector instruction based application programmed for one architecture is often not executable on another (Fu, Wu, Liu, Hong, & Hsu, 2015). The challenge of offloading and seamless execution of vectorized smartphone applications on cloud servers for energy efficiency drives and motivates this research work.

### **1.3** Statement of The Problem

Multiple techniques enable offloading of computations between heterogeneous MCC architectures. These techniques are (a) system virtualization, (b) application virtualization, and (c) process or native code migration (Shuja, Gani, Naveed, Ahmed, & Hsu, 2016). System virtualization addresses the heterogeneity of MCC architectures through abstraction and migration of a full virtual machine (VM) instance. The network overhead of VM migrations is very high for mobile devices. Due to high network latency, system virtualization based MCC offloading is not deemed feasible for most of the mobile networks (Satyanarayanan, 2015). On the contrary, application virtualization has high computational overhead. Application virtualization techniques, such as Java-based Dalvik VM of Android leads to low performing code as compared to native code. The Dalvik code is interpreted to bytecode that is platform-independent and can be executed on any Java-based VM. The intermediate bytecode translations of Dalvik VM and their platform-specific compilations lead to compute-intensive vectorized applications (Oh, Kim, Choi, & Moon, 2012).

Compiled or pre-compiled native code can be migrated from the smartphone to the cloud server. The heterogeneity of the architectures demands Dynamic Binary Translation (DBT) of the compiled code at the cloud server. The DBT process can slow the execution of the code by large factors due to the overhead of instruction translation (Nimmakayala, 2015). Moreover, DBT techniques often translate vector instructions to scalar instructions, hence, losing the advantage of vectorization. On the contrary, native pre-compiled

code based MCC offloading techniques require re-compilation and translation of mobilebased libraries to server-based libraries. In the case of vectorized multimedia applications, it is necessary to translate and map the SIMD instruction library of the mobile device to the cloud server (Shuja, Gani, Naveed, et al., 2016).

Most of the current state-of-the-art MCC offloading frameworks are dependent on system and application virtualization while addressing the requirements of heterogeneous computing architectures (Ahmed, Gani, Khan, Buyya, & Khan, 2015). Less frequently, compiled code migration is utilized to offload computations from the mobile device to the cloud server (G. Lee et al., 2015). Vectorized applications require specialized techniques for cross-platform execution of SIMD instructions. An efficient MCC offloading framework that translates and maps guest vector instructions to corresponding target vector instructions such that the vectorized applications retain their performance needs to be developed. Based on the aforementioned discussion, we can state that the problem of efficient SIMD translations in an MCC offloading framework has not been the focus of research. The research gap discussed above leads to the problem statement of this thesis.

MCC technologies empower applications to execute efficiently over cloud servers. Applications rich with SIMD instructions increase the performance of smartphones. Generic MCC frameworks do not address the heterogeneity of computing architectures for efficient translation of SIMD instructions. MCC offloading frameworks lead to higher computational overhead and inefficient vector-to-scalar translations of SIMD instructions. In MCC offloading frameworks, vector instructions that can be executed in one cycle are translated to scalar instructions that take several cycles. This leads to increased execution time and energy consumption on the cloud server as the applications require more instruction cycles when offloaded to the cloud. As a result, the overall performance of vectorized multimedia applications degrades in MCC offloading frameworks.

### **1.4 Statement of Objectives**

In this thesis, the problem of inefficient SIMD instruction translations in MCC offloading frameworks is addressed. The aim of our research is to enhance energy and time efficiency of pre-compiled code based MCC offloading frameworks through efficient translation of offloaded SIMD instructions. The objectives of this research are as follows.

- To study the MCC offloading frameworks from the perspective of offload enabling techniques to gain insights to the performance limitations of current state-of-the-art solutions.

- To investigate the overhead of MCC offload enabling techniques to reveal inefficiency in SIMD instruction translations.

- To design and develop an MCC offloading framework based on dynamic mapping of SIMD instructions that supports heterogeneity of computing architectures while providing energy and time efficiency to mobile devices.

- To evaluate the proposed framework for energy and time efficiency and compare it with the state-of-the-art MCC code offloading frameworks.

## 1.5 Research Methodology

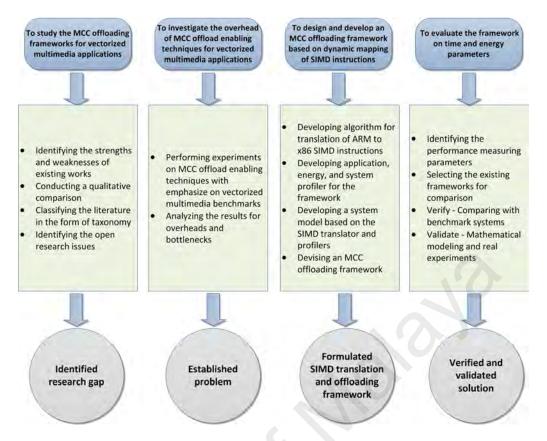

The research carried out in this thesis can be divided into four main phases according to the four objectives defined in Section 1.4. Figure 1.2 illustrates the proposed research methodology along with the details of the research objectives corresponding to each phase of research.

The state-of-the-art MCC offloading frameworks with an emphasize on native code offloading are reviewed in the first phase. The MCC offloading frameworks are classified based on the offload enabling techniques for heterogeneous computing architectures. Further, the MCC offload enabling techniques are classified as, (**a**) system virtualization, (**b**)

Figure 1.2: Proposed Research Methodology

application virtualization, and (c) native code migration. The qualitative assessment of the MCC offload enabling techniques sheds light on the computational overhead of application virtualization based solutions and communicational overheads of system virtualization based solutions. Therefore, native code offloading frameworks and the optimization of DBT process are further reviewed. In particular, the translation and porting techniques for SIMD instructions are debated. Through a comprehensive literature review, the research issue of native code offloading for SIMD instructions in MCC is identified.

The second phase of this research involves the investigation and performance evaluation of MCC offload enabling techniques, namely, system virtualization, application virtualization, and DBT for compiled code migration. Multimedia benchmarks are utilized in the performance evaluation to investigate the overheads of the MCC offload enabling techniques. The evaluation is exercised to reveal the application execution time and performance of the MCC offload enabling techniques.

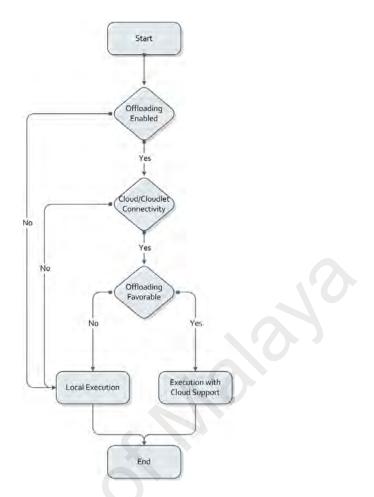

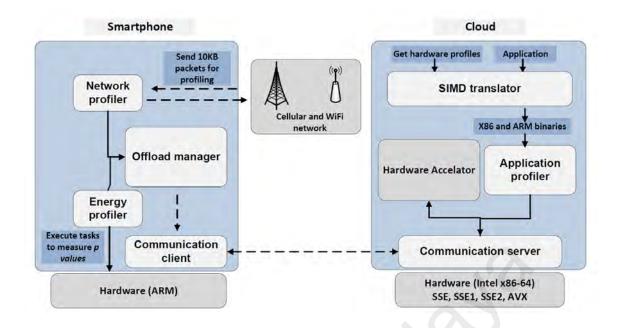

The third phase of this research work proposes SIMD instruction translation and offloading framework, SIMDOM, that enables execution of applications on heterogeneous cloud and mobile architectures. Based on the SIMD translator algorithm, a native code based MCC offloading framework and corresponding system model are formulated. The basic objective of the SIMDOM framework is to reduce the energy consumption of the mobile device while cyber-foraging computations to nearby cloud servers. To reduce the computational and communicational overhead of offloading, SIMDOM framework focuses on native code offloading and addresses the heterogeneity of the guest and host architectures through re-compilation and vector-to-vector instruction translations.

The SIMD translator based SIMDOM offloading framework is evaluated in the last phase of our research. The basic implementation of the SIMD translator is concerned with translating and mapping ARM SIMD instructions to the corresponding x86 SIMD instructions. SIMD to scalar translations are avoided as they degrade the overall performance of the system. A mathematical model is proposed to derive the energy and execution time efficiency of the framework. The mathematical model is validated by experimental results. Moreover, the effectiveness of the framework for SIMD instruction translation and offloading is verified based on the energy, execution time, and performance parameters. Furthermore, the framework performance is compared with state-of-the-art code offloading and translation frameworks in MCC.

## 1.6 Thesis Layout

This research entitled, "Integrated Vector Instruction Translator and Offloading Framework for Mobile Cloud Computing" comprises of an extensive study. Therefore, the thesis is divided into chapters for reader understandability. The thesis layout is expressed in Table 1.1.

| Chapter                | Why                                                                                                                                                                                                                                    | How                                                                                                                                                                                                                 |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction           | <ul><li>(a) To emphasize the motivation for research</li><li>(b) To state the problem and objectives</li></ul>                                                                                                                         | <ul> <li>(a) By stating the rational for undertaking the research</li> <li>(b) By formally writing the statement of problem and statement of objectives</li> <li>(c) Present the thesis organization</li> </ul>     |

| Literature re-<br>view | <ul> <li>(a) To classify and investigate the strengths and weaknesses of the state-of-the-art literature</li> <li>(b) To identify the open issues</li> </ul>                                                                           | <ul><li>(a) By critical analysis of the existing frameworks</li><li>(b) By formulation of the taxonomy and comparison based on the taxonomy</li></ul>                                                               |

| Problem anal-<br>ysis  | <ul> <li>(a) To investigate the severity of the overhead of existing MCC offload enabling techniques</li> <li>(b) To identify the impact of SIMD instructions and their translations on application performance</li> </ul>             | <ul> <li>(a) By performance analysis of MCC offload enabling techniques on multimedia benchmarks</li> <li>(b) By analyzing performance of vector and SIMD-based benchmarks</li> </ul>                               |

| SIMDOM<br>framework    | (a) To provide details of SIMDOM frame-<br>work, algorithms, and system model                                                                                                                                                          | (a) By providing pseudo code of the SIMD translator and offloading frameworks                                                                                                                                       |

| Evaluation             | <ul><li>(a) To discuss the framework evaluation parameters and their analysis</li><li>(b) To detail the data collection methodology</li></ul>                                                                                          | <ul><li>(a) By explaining the methods and tools utilized in data collection</li><li>(b) By reporting and analyzing collected data</li></ul>                                                                         |

| Results and discussion | (a) To highlight the effectiveness of the proposed solution by analyzing the experimental results                                                                                                                                      | (a) By discussing the insights gained from the experimental results                                                                                                                                                 |

|                        | (b) To verify and validate the experimental results                                                                                                                                                                                    | <ul> <li>(b) By comparing the SIMDOM framework with state-of-the-art native code offloading and translation frameworks (Qemu)</li> <li>(c) By comparing experimental results with the mathematical model</li> </ul> |

| Conclusion             | <ul> <li>(a) To summarize the findings of the research work and stress the significance of the proposed solution</li> <li>(b) To discuss the limitations of the research work and propose future directions of the research</li> </ul> | (a) By re-examination of the research objectives                                                                                                                                                                    |

Table 1.1: Thesis Layout

**Chapter 2** presents the literature review for MCC offloading frameworks and offload enabling techniques. We emphasize on native code offloading techniques that provide lower offloading overhead. Moreover, techniques for cross-platform translation of SIMD instructions in heterogeneous MCC architectures are focused. Qualitative comparison and critical analysis in the aforementioned research directions based on the parameters derived from the corresponding taxonomies is provided. The research issues highlighted by the literature review reveal the need for a framework for cross-platform execution of SIMD instructions in heterogeneous MCC architectures.

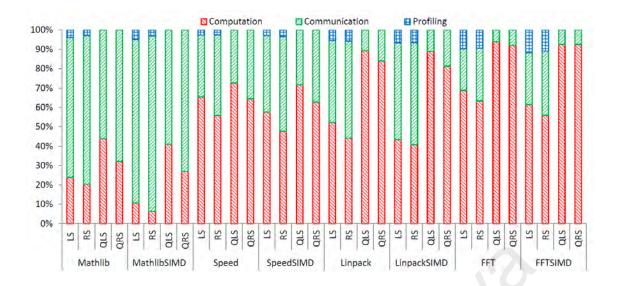

**Chapter 3** reports the performance evaluation of MCC offload enabling techniques. Vectorized benchmarks are utilized in most of the experiments to determine the overhead of MCC offload enabling techniques. The computational overhead of system virtualization (VirtualBox), application virtualization (Dalvik), and DBT (Qemu) is analyzed to gather insights to the performance limitations of the MCC offload enabling techniques. The analysis shows that the existing MCC offloading techniques have either high computational or high communicational overhead. Moreover, the performance gain for SIMD instruction based native applications and their cross-platform translations are analyzed.

**Chapter 4** describes the SIMDOM framework for translation and offloading of SIMD instruction based vectorized applications in MCC. Each module of the SIMDOM framework is described in detail with appropriate examples. Pseudo codes of the SIMD translator and offloading frameworks are also described. Furthermore, a system model for the SIMDOM framework is formulated in terms of energy optimizations.

**Chapter 5** reports on the evaluation methodology for the SIMDOM framework. The experimental setup is described with accompanying devices and vector application benchmarks. The data collection methodology regarding experimental and mathematical model parameters is described. Moreover, SIMD translator is analyzed for accuracy while application profiler is analyzed for overhead in terms of execution time. Furthermore, case studies are provided to derive the communicational overhead of system and application virtualization based MCC offloading techniques.

**Chapter 6** presents the results of experimental evaluation of the SIMDOM framework to prove its significance and efficiency. The experimental evaluation is based on two primary parameters, i.e., energy and execution time. The SIMDOM framework is compared with the native code offloading and translation framework of Qemu. Moreover, the SIMDOM framework is analyzed on varying values of system parameters, such as device sleep time and benchmark size. Furthermore, the system model of SIMDOM framework is validated with experimental data.

**Chapter 7** concludes this research work by re-visiting the research objectives. The chapter summarizes the contributions of this research work, highlights its significance, and lists its limitations. Moreover, future research directions are provided.

university

#### **CHAPTER 2: OFFLOADING FRAMEWORKS IN MCC**