# FACULTY OF COMPUTER SCIENCE AND INFORMATION TECHNOLOGY UNIVERSITY OF MALAYA SESSION 2000/2001

DEVELOPMENT OF OBJECT-ORIENTED

COMPONENTS FOR ATM NETWORK SIMULATION

WITH EMPHASIS ON SCHEDULE POLICIES

IN TRAFFIC SHAPING

BY

WONG CHEE SUM

UNDER THE SUPERVISION OF

MR. LING TECK CHAW

ATM Simulation Abstract

#### **ABSTRACT**

Asynchronous Transfer Mode (ATM) is considered to be the ground on which B-ISDN is to be built. The traffic control of ATM network is important to provide Quality of Service (QoS) for network applications. Therefore, different traffic management procedures have been introduced to achieve network performance objectives. Traffic shaping is one of the traffic management mechanisms that able to protect the network and the end-system from congestion problem.

This project focuses on the development for simulation of different scheduling policies in traffic shaping with object-oriented approach. The simulator is designed and implemented to ensure the correctness of scheduling within the network nodes, fairness of scheduling and to guarantee quality of service for ATM application. Simulation modeling is an ideal domain for the application of object-oriented methods, both in the modeling of problem domain entities and in the implementation of simulators.

A development of an object-oriented, platform independent, web-enabled, and multithread discrete-event simulator will build using Java programming language.

## **ACKNOWLEDGEMENT**

Sincere appreciation is dedicated specially to my supervisor, Mr. Ling Teck Chaw for his generous guidance and supervision for the project. His precious advises and sound understanding throughout the project is deeply appreciated

I also wish to express my greatest gratitude to my moderator Mr. Ibrahim Bin Abu Bakar for his assistance and tolerance.

Also special thanks to the other members of the project team Lim Shiau Hong, Chin Kim Choo, Sin Wai Kit, Jimmy Tan, Yu Soon Lye, Phung Jacen, Teh Boon Pin and Wong Wing Hong for their cooperation and assistance in putting the project together.

Last but not least, I will like to thanks all my coursemates for theirs generous sharing of knowledge and support. These direct and indirectly contribute to the completion of the project.

# TABLE OF CONTENTS

| ABSTRACT                                                                                                                                                         | i              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ACKNOWLEDGEMENT                                                                                                                                                  |                |

| TABLE OF CONTENTS                                                                                                                                                | iii            |

| LIST OF ILLUSTRATIONS                                                                                                                                            | vii            |

| 2.5 Types of Scheme, her Policies                                                                                                                                |                |

| CHAPTER 1: INTRODUCTION                                                                                                                                          |                |

| 1.1 Introduction to Asynchronous Transfer Mode (ATM)                                                                                                             | 1              |

| 1.2 Introduction to Traffic Shaping 1.2.1 Definition of Traffic Shaping 1.2.2 Advantages of Traffic Shaping                                                      | 2              |

| 1.3 Introduction to Scheduling Policies                                                                                                                          | 4              |

| 1.4 INTRODUCTION TO COMPUTER SIMULATION                                                                                                                          | 5              |

| 1.5 PROJECT OBJECTIVES                                                                                                                                           | 6              |

| 1.6 PROJECT SCHEDULE                                                                                                                                             | 8              |

| 1.7 REPORT ORGANIZATION                                                                                                                                          | 9              |

| CHAPTER 2: A STUDY ON ATM NETWORK SIMULATORS                                                                                                                     |                |

| 2.1 STUDY OF EXIST SIMULATORS                                                                                                                                    | 10             |

| 2.2 STUDIES ON SEVERAL NETWORK SIMULATION MODELS                                                                                                                 | 13 ramming     |

| 2.3 TRAFFIC MANAGEMENT IN ATM NETWORK                                                                                                                            |                |

| 2.3.2 Service Categories 2.3.2.1 Definition For Service Categories. 2.3.3.2 ATM Service Categories Parameters and Attributes 2.3.3 Quality of Service Parameters | 16<br>16<br>17 |

| 2.3.3.1 Peak-to-peak Cell Delay Variation (peak-to-peak CDV)                                                                    |              |

|---------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.3.3.2 Maximum Cell Transfer Delay (maxCTD)                                                                                    |              |

| 2.3.3.3 Cell Loss Ratio (CLR) 2.3.3.4 Cell Error Ratio (CER)                                                                    | 0            |

| 2.3.3.4 Cell Error Ratio (CER)                                                                                                  |              |

| 2.3.3.6 Cell Misinsertion Rate (CMR)                                                                                            |              |

| 2.3.4 Function and Procedures for Traffic Management                                                                            |              |

| 2.4 EXAMPLES OF TRAFFIC SHAPER                                                                                                  |              |

| 2.4.1 CMOS 0.35 ATM Traffic Shaper                                                                                              |              |

| 2.4.2 Cell-Space Shaper                                                                                                         |              |

| 6.1 PRODUCTION TENGUAGE CHOICE                                                                                                  |              |

| 2.5 TYPES OF SCHEDULING POLICIES                                                                                                |              |

| 2.5.1.1 Earliest Deadline First (EDF)                                                                                           |              |

| 2.5.1.2 Virtual Clock                                                                                                           |              |

| 2.5.1.3 Dynamically Weighted                                                                                                    |              |

| 2.5.1.4 Minimum Laxity Threshold                                                                                                |              |

| 2.5.1.5 Queue Length Threshold                                                                                                  |              |

| 2.5.2 Static Scheduling Algorithms                                                                                              | 26           |

| 2.5.2.1 First In First Out (FIFO) or First Come First Serve (FCFS).                                                             |              |

| 2.5.2.2 Static Priority Scheduling (SPS)                                                                                        | 27           |

|                                                                                                                                 | 27           |

| 2.5.2.4 Packet-by-packet Generalized Processor Sharing (PGPS)                                                                   | 28           |

| 2.6 EXAMPLES OF SCHEDULING                                                                                                      |              |

| 2.6.1 Algorithms on Dynamic Priority Scheduling for Heterogene                                                                  | eous Traffic |

| in ATM                                                                                                                          | 28           |

| 2.6.1.1 Double Minimum Laxity Threshold                                                                                         |              |

| 2.6.1.2 Double Queue Length Threshold                                                                                           |              |

| 2.6.1.3 Hysteresis effect Queue Length Threshold                                                                                |              |

| 2.6.3 Traffic-Controlled Rate-Monotonic Priority Scheduling of ATM                                                              | 30           |

| 그리고 그리고 있다면 그리고 있는 것이 없는 것이 없다면 |              |

| 2.7 PROGRAMMING LANGUAGE APPROACH                                                                                               |              |

| 2.7.1 Procedural Programming                                                                                                    |              |

| 2.7.2 Object-oriented Programming                                                                                               |              |

| 2.7.2.1 Java Programming                                                                                                        | 34           |

| 2.7.2.3 Java Programming Tools                                                                                                  | 38           |

|                                                                                                                                 |              |

| 2.8 CHAPTER SUMMARY                                                                                                             | 38           |

|                                                                                                                                 |              |

|                                                                                                                                 |              |

| CHAPTER 3: JAVASIM AND PRIORITY SCHEDULING ALGO                                                                                 | DRITHMS      |

| OVERVIEW                                                                                                                        |              |

| 3.1 JAVASIM                                                                                                                     | 20           |

| 3.1.1 Simulation Engine                                                                                                         |              |

| 3.1.2 Simulation Component                                                                                                      | 42           |

|                                                                                                                                 | 72           |

| 3.2 PRIORITY SCHEDULING ALGORITHMS                    |      |

|-------------------------------------------------------|------|

| 3.2.1 Hysteresis effect Queue Length Threshold (HQLT) |      |

| 3.2.2 Round Robin (RR)                                | 44   |

| 3.2.3 Select Largest Queue (SLQ)                      | 44   |

| 3.3 CHAPTER SUMMARY                                   | 45   |

|                                                       |      |

| CHAPTER 4: SYSTEM ANALYSIS                            |      |

| 4.1 PROGRAMMING LANGUAGE CHOICE                       |      |

| 4.1.1 Object-oriented Programming Techniques          |      |

| 4.1.2 The Java Programming Language                   | 46   |

| 4.2 DEVELOPMENT TOOLS                                 | . 47 |

| 4.2.1 Window 98                                       |      |

| 4.2.2 Borland Jbuilder                                |      |

|                                                       |      |

| 4.3 SYSTEM REQUIREMENTS                               |      |

| 4.3.1 Functional Requirements                         |      |

| 4.3.1.1 Topology Design System                        |      |

| 4.3.1.2 User Input System                             |      |

| 4.3.1.3 Generate Output                               |      |

| 4.3.2 Non-Functional Requirements                     |      |

| 4.3.2.1 Flexibility                                   |      |

| 4.3.2.2 Usability                                     |      |

| 4.3.2.3 Correctness                                   | . 49 |

| 4.3.2.4 Scalability                                   |      |

| 4.3.2.5 Reusability                                   | . 50 |

| 4.3.2.6 Portability                                   | . 50 |

| 4.3.2.7 Maintainability                               |      |

| 4.3.2.8 Manageability                                 | . 50 |

| 4.4 CHAPTER SUMMARY                                   |      |

|                                                       |      |

| CHAPTER 5: DESIGN OF ATM NETWORK SIMULATION           |      |

| 5.1 THE SIMULATION MODEL                              | 51   |

| 5.1.1 Overview                                        |      |

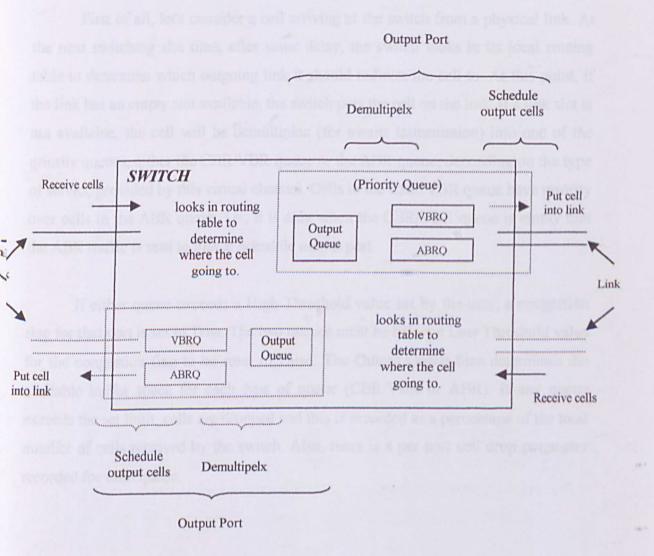

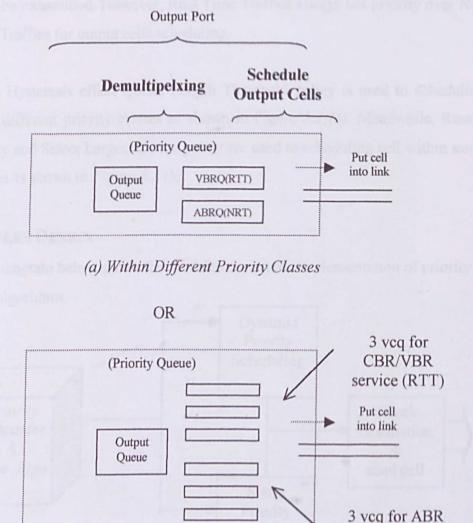

| 5.1.2 Output Ports of Switch                          | 51   |

| 5.1.3 Multithreading                                  |      |

|                                                       |      |

| 5.2 QUEUE ARCHITECTURE DESIGN                         |      |

| 5.2.1 Output Port Queuing Model                       | . 52 |

| 5.2.2 Priority Scheduling At Output Port              |      |

| 5.2.2.1 Demultiplexing                                |      |

| 5.2.2.2 Schedule Output                               | 55   |

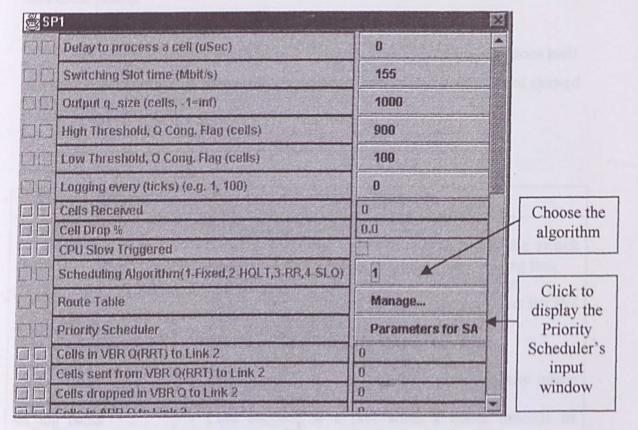

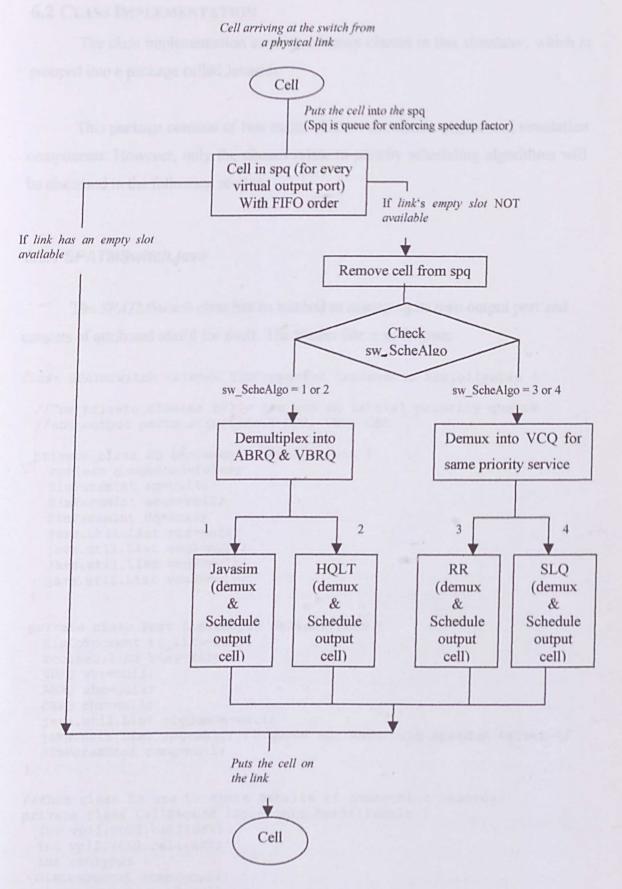

| 5.3 MODULES DESIGN                                    | . 55 |

| 5.4 COMPONENT CLASS DESIGN                            |      |

|                                                       | 4/1  |

| 5.5 CHAPTER SUMMARY                                                                    | 59                   |

|----------------------------------------------------------------------------------------|----------------------|

| CHAPTER 6: IMPLEMENTATION                                                              |                      |

| 6.1 SYSTEM IMPLEMENTATION                                                              | 60                   |

| 6.2.1 SPATMSwitch.java 6.2.2 SimParamPScheduler.java 6.2.3 CBRApp.java                 | 62<br>64<br>65       |

| 6.2.4 VBRApp.java                                                                      | 65                   |

| 6.3 PRIORITY SCHEDULING ALGORITHMS IMPLEMENTATION                                      | 67<br>68             |

| 6.4 CHAPTER SUMMARY                                                                    | 70                   |

| CHAPTER 7: TESTING 7.1 CLASS AND UNIT TESTING                                          | 71                   |

| 7.1.1 SimParamPScheduler Class                                                         | 71<br>73<br>76<br>77 |

| 7.2 SYSTEM TESTING                                                                     | 79                   |

| 7.2.1 Javasim(FCFS & Fixed Priority) vs Hysteresis effect Queue Le<br>Threshold (HQLT) | 80                   |

| 7.3 CHAPTER SUMMARY                                                                    | 83                   |

| CHAPTER 8: CONCLUSIONS                                                                 | 0.4                  |

| CHAPTER 6: CONCLUSIONS                                                                 | 84                   |

| REFERENCES                                                                             | 85                   |

|                                                                                        |                      |

# LIST OF ILLUSTRATIONS

| TABLES                                                                            |        |

|-----------------------------------------------------------------------------------|--------|

| Table 1.1 Project Schedule                                                        | 8      |

| Table 2.1 ATM Service Category Attributes                                         | 18     |

| Table 5.1 Modules Function                                                        | 56     |

| Table 7.1 Simulation Results for Testing of CBR and VBR Applications              | 75     |

| Table 7.2 Values of Output Parameters Generated During Simulation                 | 77     |

| Table 7.3 Data Generated for System Testing of Javasim vs HQLT                    | 81     |

| Table 7.4 Data Generated for System Testing of RR vs SLQ                          | 83     |

|                                                                                   |        |

| FIGURES                                                                           |        |

| Figure 1.1 Traffic Shaping                                                        | 2      |

| Figure 1.2 Three Sub-Fields of Computer Simulation                                | 5      |

| Figure 2.1 The OPNET ATM Model                                                    | 14     |

| Figure 2.2 Continuous Times Shaper Model                                          | 24     |

| Figure 2.3 Minimum Laxity Threshold                                               | 29     |

| Figure 2.4 A Typical C++ Environment                                              | 37     |

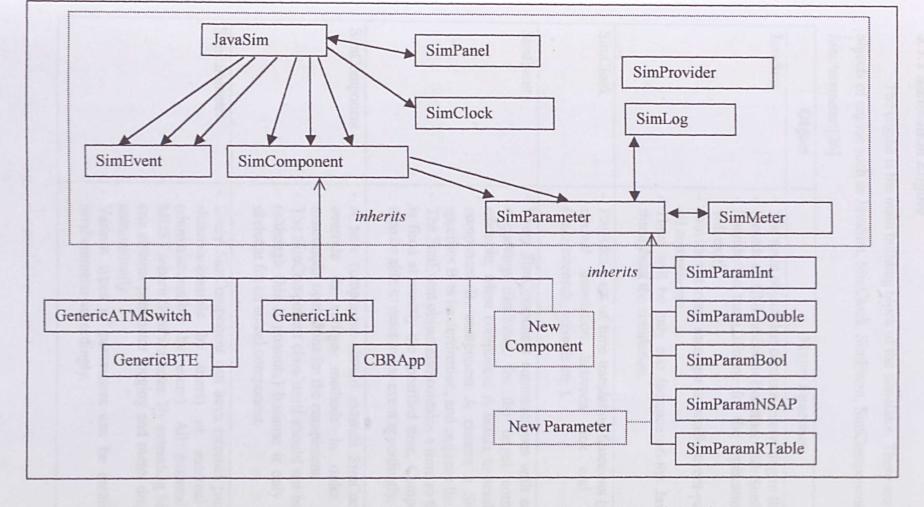

| Figure 3.1 Hierarchy of all the significant objects in the Java Network Simulator | 40     |

| Figure 5.1 Switch Architecture With Output Port Queuing Model                     | 52     |

| Figure 5.2 Methods of Cell Demultiplexing At Output Port (a) Within Diff          | ferent |

| Priority Classes and (b) Within Same Priority Class                               | 54     |

| Figure 5.3 Modules Design                                                         | 55     |

| Figure 5.4 Switch Parameters' List                                                | 56     |

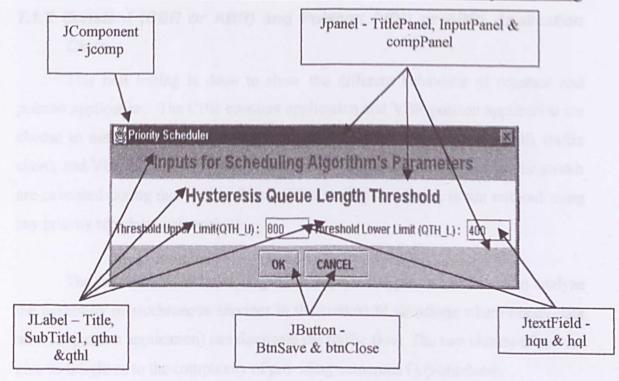

| Figure 5.5 GUI Design for Priority Scheduler's Input Window                       | 56     |

| Figure 6.1 Flow of Cells In Switch                                                | 61     |

| Figure 7.1 Input Window for Priority Scheduler Algorithms' Parameters             |        |

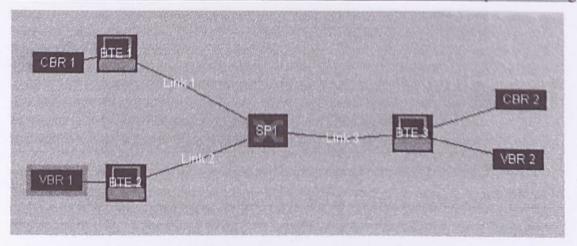

| Figure 7.2 Network Topology for Testing of Constant and Poisson Applications      | 74     |

| igure 7.3 Parameters Input Window for Constant and Poisson Applications           | 74     |

| igure 7.4 Sample Output Data Generate During Simulation                           | 75     |

| igure 7.5 Network Topology for System Testing of HQLT                             |        |

| igure 7.6 Network Topology for System Testing of Javasim vs HQLT                  |        |

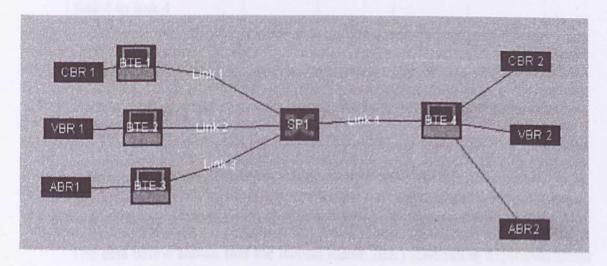

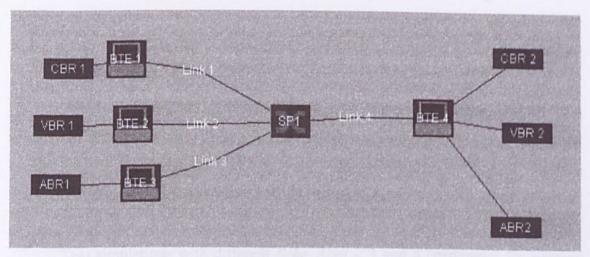

| igure 7.7 Network Topology for System Testing of RR vs SLO                        | 82     |

## **CHAPTER 1: INTRODUCTION**

This chapter begins with an introduction on asynchronous transfer mode (ATM), traffic shaping, scheduling policies and network simulation. The next section included the descriptions of project's objectives, project schedule and report organization.

## 1.1 Introduction to Asynchronous Transfer Mode (ATM)

Asynchronous Transfer Mode (ATM) is a set of international interface & signaling standard define by the ITU-T. ATM is a high performance, cell-oriented switching and multiplexing technology that utilizes fixed-length packets to carry different types of traffic. Furthermore, ATM can handle any kind of information such as voice, data, image, text & video in an integrated manner.

ATM is a connection-oriented packet switching technique in which all packets are of fixed length. ATM is a connection-oriented technology in the sense that before two systems on the network can communicate, they should inform all intermediate switches about their service requirements and traffic parameters.

ATM is a transmission technology that uses fixed and relatively short packets called cells. A cell is a 53 byte packet with 5 bytes of header/descriptor and 48 bytes of payload, or user traffic (voice, data or video) to combine data, voice and video. The reason for choosing a fixed-size packet is to ensure that the switching and multiplexing function could be carried out quickly and easily. The cells are transmitted over a connection called Permanent or Switched Virtual Circuit Connection (PVC or SVC). Even ATM does not protect data from errors, but it able to works well on digital lines with low bit error rates.

ATM is able to reduce infrastructure costs through efficient bandwidth management, operational simplicity and the consolidation of overlay networks. Beside that, it also provides a good bandwidth flexibility and can be used efficiently from desktop computers to local area & wide area networks. Therefore, ATM technology has been implemented in a very broad range of networking devices such

as, PC, workstation, and server network interface cards, workgroup and campus ATM switch, ATM multiplexers and so on.[1]

## 1.2 Introduction to Traffic Shaping

## 1.2.1 Definition Of Traffic Shaping

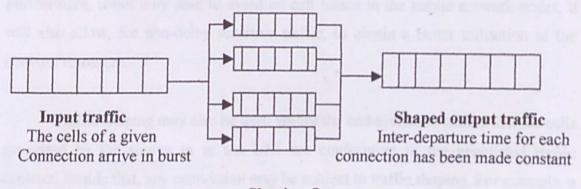

Traffic shaping is a mechanism that alters the traffic characteristics of a stream of cells on a connection to achieve better network efficiency whilst meeting the QoS objectives, or to ensure conformance at a subsequent interface. Traffic shaping mechanism is important in ATM networks, especially those that are interconnected or provide service guarantees.

Traffic shaping attempt to modify the temporal distribution of traffic to ensure that it meets the applicable traffic constraints. Shaping can be used in a source terminal connected to the network, within the network to account for jitter introduced by network element, between interconnected networks, or in a destination terminal to reconstruct timing information for jitter-sensitive applications such as video. A constraint can be apply to a particular connection, source (e.g. for charging), or (intermediate) destination (e.g. for rate adaptation).[2]

Shaping Queue One per connection

Figure 1.1 Traffic Shaping [3]

Examples of traffic shaping are peak cell rate reduction, burst length limiting, reduction of CDV by suitably spacing cells in time, and cell scheduling policy.[2]

## 1.2.2 Advantages Of Traffic Shaping

Traffic shaping, provides an opportunity to boost statistical multiplexing gain by shaping traffic streams into much "smoother" form prior to merging. Also, a shaped traffic stream is predictable, allowing easy use of statistical models for accurate resource allocation. And traffic shaping allows interswitch trunks to operate at a higher level of utilization.

The traffic shaping function is important for the new broadband services that are being deployed. It is because traffic shaping is able to avoid information loss, provide the end user several traffic contract options in terms of bandwidth and insure an use of the communication channels.

In addition, traffic shaping able smoothes the cell stream of every connection to create a more predictable traffic profile. A more predictable traffic profile leads to better fairness, lower cell loss, and less stress on network resources.

With traffic shaping, each VC is prevented from bursting into the output link at an excessive speed. Traffic shaping at the egress of a network reduces CDV (Cell Delay Variation) across the User-to-Network Interface (UNI) to the ATM end system. Furthermore, it not only able to avoiding cell losses in the public network nodes, tt will also allow, for non-delay sensitive traffic, to obtain a better utilisation of the network resources.

Traffic shaping may also be used within the end-system to ensure that the cells generated by the source or at the UNI are conforming to the negotiated traffic contract. Beside that, any connection may be subject to traffic shaping. For example, a network may choose to perform traffic shaping in conjunction with suitable UPC/NPC functions and/or virtual source/destination. [4]

#### 1.3 Introduction to Scheduling Policies

## 1.3.1 The Needs of Scheduling Policies

Scheduling policy is use to determines which queue is given the opportunity to transmit a cell that is stored in the buffer and to divide the available bandwitdh among various contending classes of service. Therefore, in an ATM network, the scheduling policy at each output link has a direct impact on message delays when the aggregate incoming traffic is higher that the output link capacity of an ATM traffic shaper. Thus admission criteria for real-time applications should take into account the specific scheduling policy used.[18]

Scheduling policies maybe implement in 2 way, that are:

- Coarse granularity (per class scheduling) that divide bandwidth among different service classes.

- Fine level granularity (per Virtual Circuit scheduling) that divide bandwidth between various connections in a service class.[5]

The scheduling policies strongly influence the cell delay which is most important for delay sensitive services. It is because the scheduling policies are able to maintain a queue containing all packets of cells which waiting for transmission.

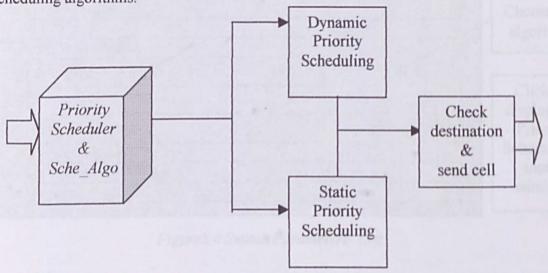

There are different algorithms for scheduling policies such as first come first serve, round robin, select largest queue and so on. However, overall the scheduling policies can be divided into two main categories: static or dynamic.[6]

## 1.3.2 Priority Scheduling

Priority scheduling is used to determine which connections are served first.

The main design objectives for this scheduling policy are:

- Fairness: The scheduling policy must serve egress network connections of the same priority class with equal probability.

- Little delay: The scheduling policy should minimize the cell delay for all service categories [7]

By priority scheduling, one may serve first cells that can tolerate less delay. Besides, priority scheduling coupled with a certain amount of buffering is able to improve the resource utilization efficiency and met the service quality requirements for all services.

#### 1.4 Introduction to Computer Simulation

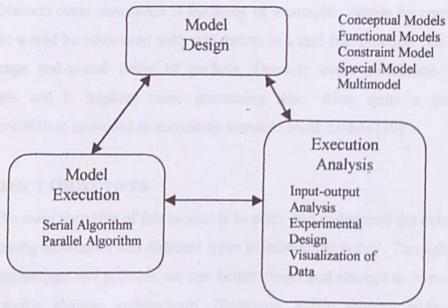

Computer simulation is the discipline of designing a model of an actual or theoretical physical system, executing the model on a digital computer, and analyzing the execution output. Simulation embodies the principle of "learning by doing" - to learn about the system a model must be built and then operate the model. To understand reality and all of its complexity, artificial objects must be built and dynamically act out roles with them. Within the overall task of simulation, there are three primary sub-fields: model design, model execution and model analysis [8].

Figure 1.2 Three Sub-Fields of Computer Simulation

## 1.4.1 Advantages and Disadvantages of Simulation

The advantages of simulation are described as below:

- Economical and quick to assemble.

- Given sufficient computing resources, can do large-scale tests.

- · Tests are controlled, reproducible.

However, certain problems exist with simulation too:

- Need to redo code for simulation environment.

- · Simulation implementation may differ considerably from real one.

- Synthetic environment may also poorly represent real one [9].

## 1.4.2 Types of Simulation

Essentially there are two forms of network simulation: Analytical modeling and Discrete event simulation.

Analytical modeling is a mathematical technique that characterizes a network as a set of equations. The main disadvantage associated with analytical models is that it is over simplistic view of the network and their inability to simulate the dynamic nature of a computer network.

Discrete event simulation is the study of a complex system by computing the times that would be associated with real events in a real-life situation. This could be the average end-to-end delay of packets. Discrete event simulation has many advantages and it requires more processing time. Also, quite a considerable investment of time is needed to accurately simulate most models [10].

#### 1.5 PROJECT OBJECTIVES

The main objective of this project is to study and understand the existing ATM traffic shaping techniques and different types of scheduling policy. Through the study of these techniques and policies, we can better model and attempt to improve on the existing traffic shaping architectures. Numerous traffic shaping techniques and scheduling policies have been proposed since the implementation of the ATM network. The thesis begins with a study on the current traffic shaping techniques and scheduling policies.

The second objective is to develop an ATM traffic shaper simulator which is uses to provide different scheduling policies. Object-oriented approach is uses to develop the simulator in order to take advantage of the features such as modularity,

extensibility, reusability and others. Moreover, applying multithreading into a simulator design can be used to closely model the real ATM traffic shaper.

The final objective is the creation of a portable, cross-platform and webenabled simulator.

# 1.6 PROJECT SCHEDULE

## **Project Schedule**

| Task                            | Start     | Finish     | June                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | July                                     | Aug | Sept      | Oct        | Nov             | Dec                       | Jan     |

|---------------------------------|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----------|------------|-----------------|---------------------------|---------|

| Research and Review             | 7/6/2000  | 18/8/2000  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |     | 9 8       |            | 1101            | Dec                       | Jan     |

| 2. Requirement & Analysis       | 1/7/2000  | 7/9/2000   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |     |           | Markey and | To the state of | atthydauai<br>T athydauai | 100000  |

| 3. System Design                | 1/9/2000  | 31/10/2000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | THE REAL PROPERTY.                       |     |           |            |                 |                           | 1 88 88 |

| 4. Modules Development *        | 1/10/2000 | 15/12/2000 | The state of the s | THE IS NOT THE                           |     |           |            |                 |                           |         |

| 5. System Integration & testing | 1/12/1999 | 15/1/2001  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | See Balletin                             |     | or design |            |                 |                           |         |

| 6. Documentation                | 1/9/1999  | 22/1/2001  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Tata ta |     |           |            |                 |                           |         |

<sup>\*</sup> Modules Development includes modules design and coding.

Table 1.1 Project Schedule

#### 1.7 REPORT ORGANIZATION

Chapter 1 gives an overview of ATM and the definition of traffic shaping and scheduling policies in ATM networks. Brief description on computer simulation is also available. Chapter 2 introduces several types on simulator available currently and studies are put on to their simulators. Also, different types and examples of traffic shaping and scheduling policies are discussed in this chapter.

Chapter 3 explains the programming language and development tools that will be used in assisting the development of the system. Further details of the functional and non-functional requirement for the system development also explained in this chapter. Beside that, an overall of system design will be shown in this chapter, followed by module design, objects design, user interface design and others.

First section of Chapter 4 discusses the two important part of Javasim ATM Simulator: Simulator Engine and Simulator Components. The second section discusses proposed priority scheduling algorithms to schedule the outgoing cells at the output port of a switch for different class of service and same class of service.

Chapter 5 discusses the programming language and development tools chosen to create the network simulator components. Beside that, brief description about functionality requirements, non-functionality requirements and development tools for simulation is also available.

Chapter 6 discusses implementation of priority scheduling algorithms at output ports of the switch for the simulator. Classes with important data items and its associate data are discussed further in the implementation section. Further more, the details implementation for the proposed algorithms also included.

Description of class, unit and system testing that had been done for the simulator is included in Chapter 7. Beside that, different priority scheduling algorithms also can be compare base on the simulation results of the system testing. Finally, an overview conclusion of this project is included at Chapter 8 of this report.

## **CHAPTER 2: LITERATURE REVIEWS**

#### 2.1 STUDY OF EXIST ATM SIMULATORS

As the emerging of speeds and dynamic of the computer networks today, management of the network traffic is highly important.

Therefore, there are a few simulation packages to describe a number of simulation experiments performed on the number of different configurations without the expanse of building a real network. The simulator actually offers a practical means of obtaining accurate information on which to plan and design a new system. Simulation is a useful technique for computer systems to perform analysis for high-speed network, especially for ATM.

#### 2.1.1 NIST ATM/HFC Network Simulator

The ATM/HFC network simulator is a tool to analyze the behavior of ATM and HFC networks without the expense of building a real network. This simulator was developed at the National Institute of Standards and Technology (NIST). This simulator is written in C Language whereby it is written in structural programming approach. Typically, the simulator program includes a graphical interface which provides the user with a means to display the topology of the network, define the parameters and connectivity of the network, log data, and to save and load the network configuration. In addition to the user interface, the simulator has an event manager, I/O routines, and various tools that can be used to build components [11].

## Advantages

The user can create different network topologies, adjust the parameters of each component's operation, measure network activity, save/load different simulation configuration and log data during simulation execution. The simulator is equipped with graphical user interface.

#### Limitations

Users of the simulator might face problems setting up the network topology because of the requirement to consider a large number of parameters.

User or programmers needs to have strong foundation in C programming language to customize the simulator's components. Besides, it is using procedural approach whereby the components have overlapped functions between the components. This is not supposed to happen in object-oriented programming approach.

The simulator only can run is UNIX or LINUX platform. This makes the simulator can only run in limited platforms and it is not widely used.

#### 2.1.2 REAL Network Simulator

The REAL network simulator is a network simulator designed for testing on congestion and flow control mechanisms. The simulator takes as input a scenario, which is description of network topology, protocols, workload and control parameters. It produce as output statistics such as the number of packets sent by each source of data, the queuing point, the number of dropped and retransmitted packets and other similar information. This simulator has many different versions.

For REAL version 5.0, it provides users with a way of specifying such networks and to simulate their behavior. It provides around 30 modules (written in C) that exactly emulate the action of several well-known flow control protocols (such as TCP), and 5 research scheduling discipline (such as Fair Queuing and Hierarchical Round Robin). Besides, it includes a graphical user interface (GUI) written in Java. This allows users to quickly build simulation scenarios with a point-and-click interface [12].

This REAL 5.0 simulator runs on Sun3s, Sparcs, MIPS boxes, Vaxen and 3B2, under 4.3BSD-like operating systems: SunOS, IRIX, UMIPS, Ultrix etc. Besides, the REAL version 4.0 has been successfully ported to i386/FreeBSD 2.0.5 platform and the Linux (Red Hat Release) platform [9].

The files in REAL 5.0 can be divided into the following logical classes:

- Node functions: These are the functions that execute protocols in nodes.

- Queue management and routing: These manage buffers in nodes and gateways,

and perform packet switching.

Node functions implement computation at each of the nodes in the network. There are three types of node function: source, router and sink.

The queue management functions are written in an object oriented and layered style. The queue objects are manipulated by a small set of functions. Each layer provides services that the layer above uses to provide its own services. Packets are buffered in a per-conversation linked list and are accessed by two pointers: one points to the packet at the head of the queue, and another points to the tail. Each packet has a field, which points to the next packet in the queue.

Comparing REAL 5.0 to REAL 4.0 in October 1993, and in the last four years, many changes have been made. These include

- many new simulation modules

- a Java-based GUI.

- · faster, smaller, cleaner simulation engine

- ports to FreeBSD, Solaris, and Digital Unix (OSF/3)

- simulation exercises based on my book

- minor bug fixes

## Advantages

This simulator provides a flexible testbed for studying the dynamic behaviour of flow and congestion control schemes in packet switch data networks. Besides, the user can modify the simulator software to accommodate network components.

#### Limitations

Some of the REAL version's network simulator does not give user an interactive modelling environment with a graphical user interface (GUI) representation capabilities but it is available in REAL version 5.0. This version includes a graphical user interface (GUI) written in Java and it allows users to quickly

build simulation scenarios with a point-and-click interface. Besides, knowledge of C programming language and different platforms is a must for programmers to make changes from the source code provided because this simulator only will run in several platforms.

#### 2.2 STUDY ON SEVERAL NETWORK SIMULATION MODELS

A survey is made on several network simulation and management models done by several researchers, master and phD students of universities, which are available on many journals and papers. In this survey, there are a few simulator models, which will be discussed: An object-oriented network model for development of modeling traffic management In ATM networks with OPNET and an ATM switch simulation tool based on the C++ object-oriented programming language. Basically, the models are mainly based on object-oriented approaches.

## 2.2.1 Modeling Traffic Management In ATM Networks With OPNET

This paper [13], describe the OPNET models that have been developed for ATM and ABR design and analysis.

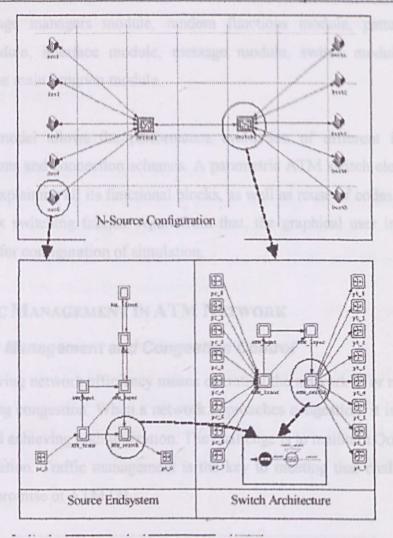

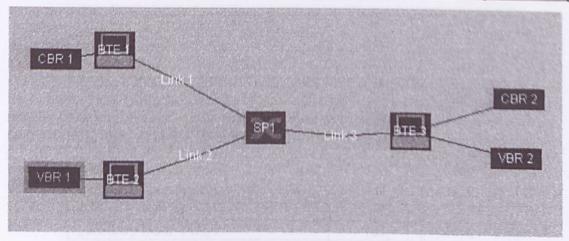

The example network topology used for the design and development of traffic management functions within AMS represents an N-source configuration shown in *Figure 2.1*. Source and destination end-systems are connected to a pair of ATM switches that communicate via a bottleneck link.

Figure 2.1 The OPNET ATM Model

The OPNET process modeling methodology was used in the development of the switch process model that delivered basic capabilities of the core ATM switching fabric, ABR feedback control, buffer management and scheduling. The key steps of this modeling methodology include: definition of the system context, identifying interdependent modules, enumeration of events, selection of states of a process, construction of an event response table and construction of the finite state machine.

# 2.2.2 ATM Switch Simulation Tool based on C++ Object-oriented Programming Language

In [14], a software package to simulate ATM switches written in C++ programming language is presented and its main modules and objects are described. The package consists of several modules: General purposed module, input/output

module, storage managers module, random functions module, pattern module, buffering module, interface module, message module, switch module, statistics module and the main program module.

This model allows the performance evaluation of different input traffic characterizations and connection schemes. A parametric ATM switch element model is described explaining all its functional blocks, as well as reuse of codes to construct more complex switching fabrics. Apart from that, the graphical user interface also implemented for configuration of simulation.

## 2.3 TRAFFIC MANAGEMENT IN ATM NETWORK

## 2.3.1 Traffic Management and Congestion Control

Achieving network efficiency means operating the network at or near capacity — approaching congestion. When a network approaches congestion, it is functioning efficiently and achieving high utilization. The challenge is to maintain QoS in the face of high utilization. Traffic management is the key to meeting that challenge and to realizing the promise of ATM.[2]

Traffic management is concerned with ensuring that users get their desired quality of service. The problem is especially difficult during periods of heavy load particularly if the traffic demands cannot be predicted in advance. This is why congestion control, although only a part of the traffic management issues, is the most essential aspect of traffic management.

When two bursts arrive simultaneously at a node, the queue lengths may become large very fast resulting in buffer overflow. Also, the range of link speeds is growing fast as higher speed links are being introduced in slower networks of the past. At the points, where the total input rate is larger than the output link capacity, congestion becomes a problem.

Proper traffic management and congestion control helps ensure efficient and fair operation of networks in spite of constantly varying demand. This is particularly important for the data traffic which has very little predictability and, therefore, cannot reserve resources in advance as in the case of voice telecommunications networks.[15]

## 2.3.2 Service Categories

#### 2.3.2.1 Definition For Service Categories

#### Constant Bit Rate (CBR) Service Category

This category is used for emulating circuit switching. The cell rate is constant. Cell loss ratio is specified for CLP=0 cells and may or may not be specified for CLP=1 cells. Examples of applications that can use CBR are telephone, video conferencing, and television (entertainment video).[15]

#### Real-Time Variable Bit Rate (rt-VBR) Service Category

The real-time VBR service category is intended for real-time applications, i.e., those requiring tightly constrained delay and delay variation, as would be appropriate for voice and video applications. rt-VBR connections are characterized in terms of a Peak Cell Rate (PCR), Sustainable Cell Rate (SCR), and Maximum Burst Size (MBS).[15]

## Non-Real-Time Variable Bit Rate (nrt-VBR) Service Category

The non-real-time VBR service category is intended for non-real-time applications which have bursty traffic characteristics and which are characterized in terms of a PCR, SCR, and MBS. For those cells which are transferred within the traffic contract, the application expects a low cell loss ratio. Non-real-time VBR service may support statistical multiplexing of connections. No delay bounds are associated with this service category.[15]

## Unspecified Bit Rate (UBR) Service Category

This category is designed for those data applications that want to use any leftover capacity and are not sensitive to cell loss or delay. Such connections are not rejected on the basis of bandwidth shortage (no connection admission control) and not policed for their usage behavior. During congestion, the cells are lost but the sources are not expected to reduce their cell rate. In stead, these applications may have their own higher-level cell loss recovery and retransmission mechanisms. Examples of applications that can use this service are email, file transfer, news feed, etc. Of course, these same applications can use the ABR service, if desired.[15]

## Available Bit Rate (ABR) Service Category

This category is designed for normal data traffic such as file transfer and email. Although, the standard does not require the cell transfer delay and cell loss ratio to be guaranteed or minimized, it is desirable for switches to minimize the delay and loss as much as possible. Depending upon the congestion state of the network, the source is required to control its rate. The users are allowed to declare a minimum cell rate, which is guaranteed to the VC by the network. Most VCs will ask for an MCR of zero. Those with higher MCR may be denied connection if sufficient bandwidth is not available.[15]

#### Guaranteed Frame Rate (GFR) Service Category Definition

The GFR service category is intended to support non-real-time applications. It is designed for applications that may require a minimum rate guarantee and can benefit from accessing additional bandwidth dynamically available in the network. It does not require adherence to a flow control protocol. The service guarantee is based on AAL-5 PDUs (frames) and, under congestion conditions, the network attempts to discard complete PDUs instead of discarding cells without reference to frame boundaries.[2]

## 2.3.2.2 ATM Service Categories Parameters and Attributes

Table 2-1 provides a list of ATM attributes (traffic parameters, QoS parameters, and feedback characteristics) and identifies whether and how these are supported for each service category.

| stems and the nerv        | ATM Layer Service Category         |               |           |             |            |             |  |  |

|---------------------------|------------------------------------|---------------|-----------|-------------|------------|-------------|--|--|

| Attribute                 | CBR                                | rt-VBR        | nrt-VBR   | UBR         | ABR        | GFR         |  |  |

| Traffic Parameters,:      |                                    |               |           | unumi pende | anner bei  |             |  |  |

| PCR and CDVT <sub>3</sub> | Specified                          |               |           | Specified . | Specified, | Specified   |  |  |

| SCR. MBS, CDVT,           | n/a                                | Spe           | cified    | n/a         |            |             |  |  |

| MCR                       |                                    | n             | Specified | n/a         |            |             |  |  |

| MCR, MBS, MFS,<br>CDVT,   | Delay Variation (peak-to-peak CDV) |               |           |             |            | Specified   |  |  |

| QoS Parameters,:          | A AMERICA                          | A Deservation |           |             |            |             |  |  |

| Peak-to-peak CDV          | Specified                          |               |           | Unspecified |            |             |  |  |

| MaxCTD                    | Specified                          |               |           | Unspecified |            |             |  |  |

| CLR                       | Specified                          |               |           | Unspecified | See Note 1 | See Note 7  |  |  |

| Other Attributes:         |                                    |               |           |             |            |             |  |  |

| Feedback                  | Unspecified                        |               |           |             | Specified. | Unspecified |  |  |

## Table 2.1 ATM Service Category Attributes

#### Notes:

- CLR is low for sources that adjust cell flow in response to control information.

Whether a quantitative value for CLR is specified is network specific.

- 2. Might not be subject to CAC and UPC procedures.

- 3. Represents the maximum rate at which the ABR source may ever send. The actual rate is subject to the control information.

- These parameters are either explicitly or implicitly specified for PVCs or SVCs.

- CDVT refers to the Cell Delay Variation Tolerance (see Section 4.4.1). CDVT

is not signaled. In general, CDVT need not have a unique value for a

connection. Different values may apply at each interface along the path of a

connection.

- 6. See Section 2.4.

- CLR is low for frames that are eligible for the service guarantee. Whether a

quantitative value for CLR is specified is network specific. [2]

## 2.3.3 Quality of Service Parameter

Six QoS parameters that correspond to network performance objectives are identified in this specification. Three of these may be negotiated between the end-

systems and the networks. One or more values of the QoS parameters may be offered on a per connection basis, corresponding to the number of related performance objectives supported by the network. Support of different performance objectives can be done by routing the connection to meet different objectives, or by implementation-specific mechanisms within individual network elements.

The following QoS parameters are negotiated:

- Peak-to-peak Cell Delay Variation (peak-to-peak CDV)

- Maximum Cell Transfer Delay (maxCTD)

- Cell Loss Ratio (CLR)

The following QoS parameters are not negotiated:

- Cell Error Ratio (CER)

- Severely Errored Cell Block Ratio (SECBR)

- Cell Misinsertion Rate (CMR) [2]

# 2.3.3.1 Peak-to-peak Cell Delay Variation (peak-to-peak CDV)

The peak-to-peak CDV is the difference between the  $(1 - \alpha)$  quantile of the CTD and the fixed CTD that could be experienced by any delivered cell on a connection during the entire connection holding time. The term "peak-to-peak" refers to the difference between the best and worst case of CTD, where the best case is equal to the fixed delay, and the worst case is equal to a value likely to be exceeded with probability no greater than a. Assuming that the fixed delay is the reference delay for the two point CDV, the range of the distribution of the two-point CDV is the same as the peak-to-peak CDV. Refer to UNI Signaling 4.0 for the coding of peak-to-peak CDV.

Networks have a finite ability to control peak-to-peak CDV. Therefore, endsystems cannot expect to negotiate arbitrarily small values of peak-to-peak CDV as their sole means of meeting jitter and wander tolerances.[2]

## 2.3.3.2 Maximum Cell Transfer Delay (maxCTD)

The maximum Cell Transfer Delay (maxCTD) specified for a connection is the  $(1 - \alpha)$  quantile of CTD. The CLR at connection request time is used to place an

upper bound on a. When a switch accumulates maxCTD or CDV it may choose a smaller  $\alpha$  which may have the effect of over-estimating the cumulative maxCTD or CDV. The assumed relationship between CLR and  $\alpha$  is for further study.[2]

#### 2.3.3.3 Cell Loss Ratio (CLR)

The Cell Loss Ratio is defined for a connection as:

$$CLR = \frac{Lost Cells}{Total Transmitted Cells}$$

Lost and transmitted cells counted in severely errored cell blocks should be excluded from the cell population in computing cell loss ratio. Each ATM cell has a "Cell Loss Priority (CLP)" bit in the header. During congestion, the network first drops cells that have CLP bit set. Since the loss of CLP=0 cell is more harmful to the operation of the application, CLR can be specified separately for cells with CLP=1 and for those with CLP=0.[2]

## 2.3.3.4 Cell Error Ratio (CER)

The Cell Error Ratio (CER) is defined as follows for a connection:

$$CER = \frac{Errored Cells}{Successfully Transferred Cells + Errored Cells}$$

Successfully transferred cells and errored cells contained in cell blocks counted as severely errored Cell Blocks should be excluded from the population used in calculating cell error ratio.[2]

## 2.3.3.5 Severely Errored Cell Block Ratio (SECBR)

The Severely Errored Cell Block Ratio (SECBR) is defined as follows for a connection:

A cell block is a sequence of N cells transmitted consecutively on a given connection. A severely errored cell block outcome occurs when more than M errored cells, lost cells, or misinserted cell outcomes are observed in a received cell block.

For practical measurement purposes, a cell block will normally correspond to the number of user information cells transmitted between successive OAM cells. Refer to ITU-T Recommendation I.610 for the size of cell blocks.[2]

## 2.3.3.6 Cell Misinsertion Rate (CMR)

The Cell Misinsertion Rate (CMR) is defined as follows for a connection:

$$CMR = \frac{Misinserted Cells}{Time Interval}$$

Severely Errored Cell Blocks should be excluded from the population when calculating the cell misinsertion rate. Cell misinsertion on a particular connection is most often caused by an undetected error in the header of a cell being transmitted on a different connection. This performance parameter is defined as a rate (rather than the ratio) since the occurrence of misinserted cells is independent of the number of transmitted cells received on the corresponding connection.[2]

## 2.3.4 Function and Procedures for Traffic Management

The following functions form a framework for managing and controlling traffic and congestion in ATM networks and may be used in appropriate combinations depending on the service category.[2]

Connection Admission Control (CAC) is defined as the set of actions taken

by the network during the call set-up phase in order to determine whether a

connection request can be accepted or should be rejected (or whether a request for re-allocation can be accommodated).

- Feedback controls are defined as the set of actions taken by the network and by end-systems to regulate the traffic submitted on ATM connections according to the state of network elements. This specification defines one network feedback control mechanism: the ABR flow control. The ABR flow control may be used to adaptively share the available bandwidth among participating users.

- Usage Parameter Control (UPC) is defined as the set of actions taken by the network to monitor traffic and enforce the traffic contract at the User Network. Network Parameter Control (NPC) is a similarly defined set of actions at the Network Node Interface. The main purpose of UPC and NPC is to protect network resources from malicious as well as unintentional misbehavior, which can affect the QoS of other already established connections, by detecting violations of negotiated parameters and taking appropriate actions. Such actions may include cell discard and cell tagging.

- Cell Loss Priority control: For some service categories the end system may generate traffic flows of cells with Cell Loss Priority (CLP) marking. The network may follow models which treat this marking as transparent or as significant. If treated as significant, the network may selectively discard cells marked with a low priority to protect, as far as possible, the QoS objectives of cells with high priority.

- Traffic Shaping: Traffic shaping mechanisms may be used to achieve a

desired modification to the traffic characteristics of a connection. The

objectives of this function are to achieve a better network efficiency whilst

meeting the QoS objectives and/or to ensure connection traffic conformance at

a subsequent interface.

- Network Resource Management: The service architecture allows logical separation of connections according to service characteristics. Although cell scheduling and resource provisioning are implementation and network specific, they can be utilized to provide appropriate isolation and access to resources. Virtual Paths are a useful tool for resource management.

- Frame Discard: A congested network that needs to discard cells may discard

at the frame level rather than at the cell level.

#### 2.4 EXAMPLES OF TRAFFIC SHAPER

## 2.4.1 CMOS 0.35 ATM Traffic Shaper

The design and implementation of CMOS 0.35 ATM Traffic Shaper was outlined in this paper [3]. The main function of this ATS is the collection of low bit rate traffics to fill a higher bit rate pipe in order to reduce the cost of ATM based services, nowadays mainly influenced by transmission cost. The chip was designed with a Top-Down methodology using as HDL, Verilog.

The ATS circuit is sort of queue administrator; it stores each cell in a different queue according to its connection identifier. The time interval between two consecutive cells from the same queue can be programmed independently for every active connection.

The chosen shaping mechanism is based on a memory-less algorithm: the outcoming bit rate for each connection (queue) is calculated in terms of the speed that can be handled by the link (network connection).

$$V_c = V_1 \cdot \frac{N}{2^k}$$

with  $N \in [0, 2^k]$  and  $V \in [V_1, \frac{V_1}{2^k}]$

When  $V_c$  in the connection speed,  $V_1$  the link speed, N is the parameter used to specify the connection speed.

#### 2.4.2 Cell-Space Shaper

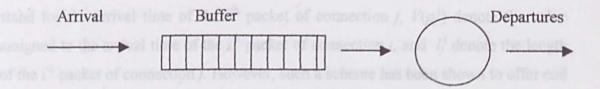

The proposed cell-space shaper [16] is modeled as a FIFO server. The service time depends on the interarrival times of the arrival process, and on whether the shaper is empty upon arrival. The service time is optimized, assuming the shaper is empty, so that the interdeparture time variance of cells leaving the shaper queue, heuristics are included in the optimization.

In order to shape sources where the cell arrival process is known and is analytically tractable, a continuous time shaper model is discussed. On the other hand, for cases when the cell arrival process is intractable, or only a cell interarrival histogram is available, a discrete time version of the shaper model is discussed too.

The shaper can represented as a queue, as shown below:

Figure 2.2 Continuous Times Shaper Model

This simple traffic shaping model found an optimal shaping parameter of source, based on its statistical characteristics. Using this parameter, cell arrivals were delayed, as needed, in order to realise a less bursty source. The reduction in burstiness was characterised by a reduction in the cell interarrival variance of the source.

#### 2.5 Types of Scheduling Policies

## 2.5.1 Dynamic Scheduling Algorithms

Scheduling with real-time constraints requires dynamic algorithms to increase utilization and for advanced processing of multiple class traffics. Dynamic Scheduling Algorithms policy provides a very efficient scheme for real time traffic and non real time traffic.

#### 2.5.1.1 Earliest Deadline First (EDF)

With EDF scheduling, each connection  $i \in N$  is assigned a delay bound  $d_j$ , where the delay bound maybe different for each connection. A n EDF scheduler selects packets for transmission in increasing order of packet deadlines, where the deadlines are calculated as the sum of arrival time and delay bound of the packet. EDF is relatively difficult to implement and entails significant overhead.

EDF is optimal with respect top Lateness, but Locke's experiments have shown that the algorithm performs very poorly in overhead conditions. This is because it gives highest priority to packets that are close to missing their deadlines.[6]

#### 2.5.1.2 Virtual Clock

The virtual clock scheduling algorithm assigns each packet a value upon its arrival and transmits packets. Let  $p_j^i$  stand for the  $i^{th}$  packet of connection j,  $A(p_j^i)$  stand for the arrival time of the  $i^{th}$  packet of connection j,  $V(p_j^i)$  denote the value assigned to the arrival time of the  $i^{th}$  packet of connection j, and  $l_j^i$  denote the length of the  $i^{th}$  packet of connection j. However, such a scheme has been shown to offer end to end delay deadline by effecting a trade-off between bandwidth and buffer space. The ratio of this trade-off is inflexible, and can not be altered due to the nature of the algorithm.[6]

## 2.5.1.3 Dynamically Weighted

The dynamically weighted priority scheduling algorithm provides a means to design a traffic shaper that is priority based but contains a delay sensitive portion to prevent starvation of data. The dynamically weighted priority scheduling algorithm provides a mechanism for simultaneously improving the balance of cell loss and delay.

We consider a time dependent "instantaneous priority index" Pj(t) for a jth class of service (a queue) at a given time t to be

$$P_{j}(t) = \frac{U_{j}}{[W_{j}(t)]}$$

Where Uj is the associated fixed priority number, a lower Uj means a higher priority, and Wj(t) is the amount of time the oldest cell in the j th class has waited in queue j. In our implementation of this algorithm, the priority index for each queue is recalculated for every output time slot (based on the speed of the outbound link). The queue with the lowest value of priority index is awarded the time slot and is permitted to transmit a cell during that time. The fixed priority values, Uj, can be chosen arbitrarily (given that the higher priority queue gets the smaller number). For example, we can choose the values 1 and 2 for CBR and VBR classes, respectively. The value for Wj is specified in units of 1/100 th of a microsecond. Note that for  $\beta=0$  we have a fixed priority scheduling where Pj(t)=Uj. For a very large  $\beta$ , Pj(t) is heavily influenced by the wait time of the cell and the scheduling mechanism behaves as a FIFO. This algorithm can be considered a *dynamically weighted priority* scheme where the weights depend on the state of the queues at a given time. [5]

#### 2.5.1.4 Minimum Laxity Threshold

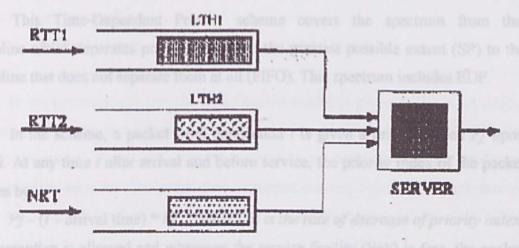

The Minimum Laxity Threshold algorithm gives priority to the real time traffic when the minimum laxity of a real time cell is less than or equal to a threshold, LTH: otherwise priority is given to the non real-time traffic (NRT). The minimum laxity is defined as the amount of time until the first deadline of all queued real time cells expires.[17]