ACW-2834 Kepintaran Brotan

PERPUSTAKAAN UNIVERSITI MALAYA

# **Dynamic Modelling of A Two-Stage**

# **ATM Tandem Banyan Switch**

# THAM HON LOKE

# **Faculty of Computer Science and Information Technology University of Malaya**

2002

Abstract

# ABSTRACT

This dissertation studies the dynamic modelling of Two-State ATM Tandem Banyan Switch. First of all, ATM technology and ATM switch are introduced, then the ATM switch's architecture and its functions are discussed in detail. A Two-State ATM Tandem Banyan Switch has been selected as a model to be simulated. MATLAB's Simulink tool has been used to dynamically model the ATM switch. The ATM switch simulated is a simple two-stage Banyan Switch. It consists of 2 Inports x 2 Outports, with a switching algorithm included. The algorithm covers all cell flow patterns that are possible in a 2 Inports x 2 Outports Banyan Switch. The objective is to keep the cell loss rate at a minimum level. Lastly, this project presents an example of dynamic simulation, which will examine the cell flow patterns, cell loss rate and the switch performance. Discussion and overall conclusion are made based on the simulation results.

# ACKNOWLEDGEMENTS

I have learnt a great deal in the process of completing this dissertation. A lot of people have contributed to it. I would like to take this opportunity to express my appreciation to all of them.

First of all, I would like to thank Assoc. Prof. Dr. Selvanathan Narainasamy, my supervisor for his invaluable guidance and advice throughout the writing of this dissertation. Special thanks to the exam panel for taking their time to go through this dissertation.

Thanks to my fellow course mates for sharing their knowledge generously and their company throughout the time in University Malaya.

Not forgetting, my dearest family members, I am grateful to them for their continuous support in my pursuit of this course and my endeavour.

Last but not the least, to my girl friend who always stands by me, giving me the strength I need to complete this dissertation successfully.

# TABLE OF CONTENTS

| ABSTRACT                                                               | i    |

|------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                       | ii   |

| TABLE OF CONTENTS                                                      | iii  |

| LIST OF FIGURES                                                        | vii  |

| LIST OF TABLES                                                         | viii |

| ACRONYMS                                                               | ix   |

| CHAPTER 1: INTRODUCTION TO ATM SWITCH AND ATM SIMULATION SOFTWARE      | 1    |

| 1.1 INTRODUCTION TO ASYNCHRONOUS TRANSFER MODE (ATM) TECHNOLOGY        | 1    |

| 1.1.1Quality of Service and Service Categories                         | 2    |

| 1.1.2 ATM Cell Format                                                  | 3    |

| 1.2 ATM Switch                                                         | 4    |

| 1.2.1 ATM Switch Functions                                             |      |

| 1.3 ATM SWITCH SIMULATION                                              | 6    |

| 1.3.1Simulation                                                        | 6    |

| 1.3.2 Simulation Software                                              | 6    |

| 1.4 INTRODUCTION TO SIMULINK                                           |      |

| 1.5 OBJECTIVES OF THE DISSERTATION                                     | 9    |

| 1.6 SCOPE OF THE PROJECT                                               | 10   |

| 1.7 THE STRUCTURE OF THE DISSERTATION                                  | 11   |

| CHAPTER 2: ATM SWITCH ARCHITECTURE, FUNCTIONALITY AND DESIGN PRINCIPLE | 12   |

| 2.1 Switching Functions                                                | 12   |

| 2.1.1 User Plane                                                       | 12   |

| 2.1.2 Control Plane                                                    | 12   |

| 2.1.3 Management Plane                                                 | 13   |

| 2.1.4 Traffic Control Functions                                        | 13   |

| 2.2 A GENERIC ATM SWITCHING ARCHITECTURE                               | 13   |

# Table of Contents

| 2.2.1 Switch Interface                                             |    |

|--------------------------------------------------------------------|----|

| 2.2.2 Cell Switch Fabric                                           |    |

| 2.2.3 Connection Admission Control (CAC)                           |    |

| 2.2.4 Switch Management                                            |    |

| 2.3 THE CELL SWITCH FABRIC                                         | 17 |

| 2.3.1 Concentration, Expansion and Multiplexing                    |    |

| 2.3.2 Routing and buffering                                        |    |

| 2.4 SWITCH DESIGN PRINCIPLES                                       |    |

| 2.4.1 Internal Blocking                                            |    |

| 2.4.2 Buffering Approaches                                         |    |

| 2.4.3 Buffer Sharing                                               |    |

| 2.5 BANYAN NETWORK                                                 | 29 |

| 2.5.1 Tandem Banyan Switch Architecture                            |    |

| 2.5.2 Knockout Switching Architecture                              |    |

| 2.6. SUMMARY                                                       |    |

|                                                                    |    |

| CHAPTER 3: SIMULATION AND SIMULINK                                 |    |

| 3.1 INTRODUCTION TO SIMULATION                                     | 35 |

| 3.1.1 Basic Concepts                                               |    |

| 3.1.2 Continuous versus Discrete                                   |    |

| 3.1.3 Stochastic versus Deterministic                              |    |

| 3.1.4 Discrete Event Simulation                                    |    |

| 3.1.5 Event-Driven versus Time-Driven in Discrete Event Simulation |    |

| 3.1.6 Computer Simulation                                          |    |

| 3.2 MODELLING AND SIMULATION                                       |    |

| 3.2.1 Modelling and Simulation Cycle                               |    |

| 3.2.2 Simulate ATM Tandem Banyan Switch Model                      |    |

| 3.2.3 Assumption and Performance Issue                             |    |

| 3.3 COMPUTER SIMULATION USING SIMULINK                             | 45 |

| 3.3.1 What is Simulink                                             |    |

| 3.3.2 Why use Simulink?                                            |    |

| 3.3.3 Application in Simulink Toolboxes                            |    |

| 3.4 ADVANTAGE OF USING SIMULINK                                    |    |

| 3.5 SUMMARY                                                        |    |

|                                                                    |    |

#

# Table of Contents

| 4.1.1 Two-State ATM Tandem Banyan Switch Model       52         4.1.2 Modelling and simulation of A Two-State ATM Tandem Banyan Switch Model       53         4.2 CHARACTERISTIC OF MODEL TWO STAGES ATM TANDEM BANYAN SWITCH       54         4.3 IMPLEMENTATION ISSUE       56         4.3.1 How models are represented in Simulink tool.       56         4.3.2 How models are built in Simulink.       56 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2 CHARACTERISTIC OF MODEL TWO STAGES ATM TANDEM BANYAN SWITCH       54         4.3 IMPLEMENTATION ISSUE       56         4.3.1 How models are represented in Simulink tool.       56                                                                                                                                                                                                                        |

| 4.3 IMPLEMENTATION ISSUE       56         4.3.1 How models are represented in Simulink tool.       56                                                                                                                                                                                                                                                                                                         |

| 4.3.1 How models are represented in Simulink tool                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4 3 2 How models are built in Simulink                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.3.3 How models are connected among each other                                                                                                                                                                                                                                                                                                                                                               |

| 4.3.4 How simulation works                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3.5 Important Simulink blocks that make this simulation project works                                                                                                                                                                                                                                                                                                                                       |

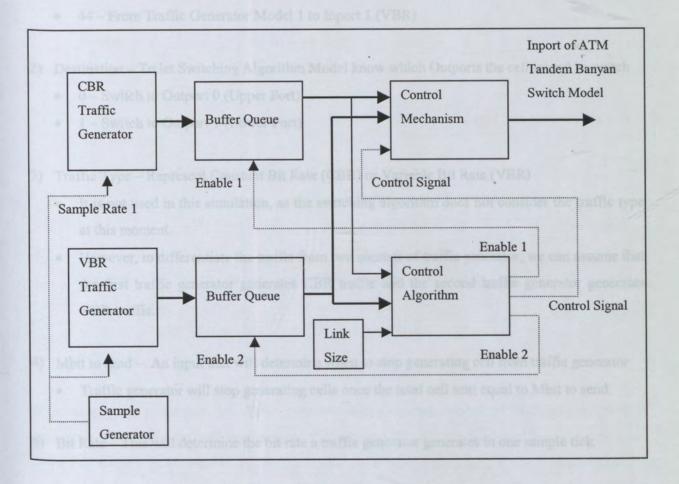

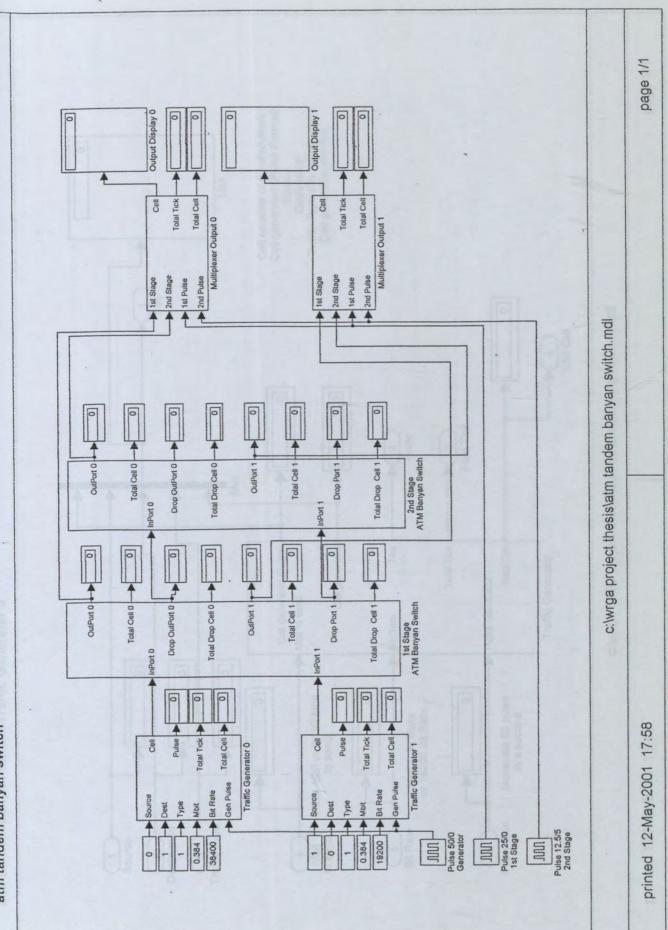

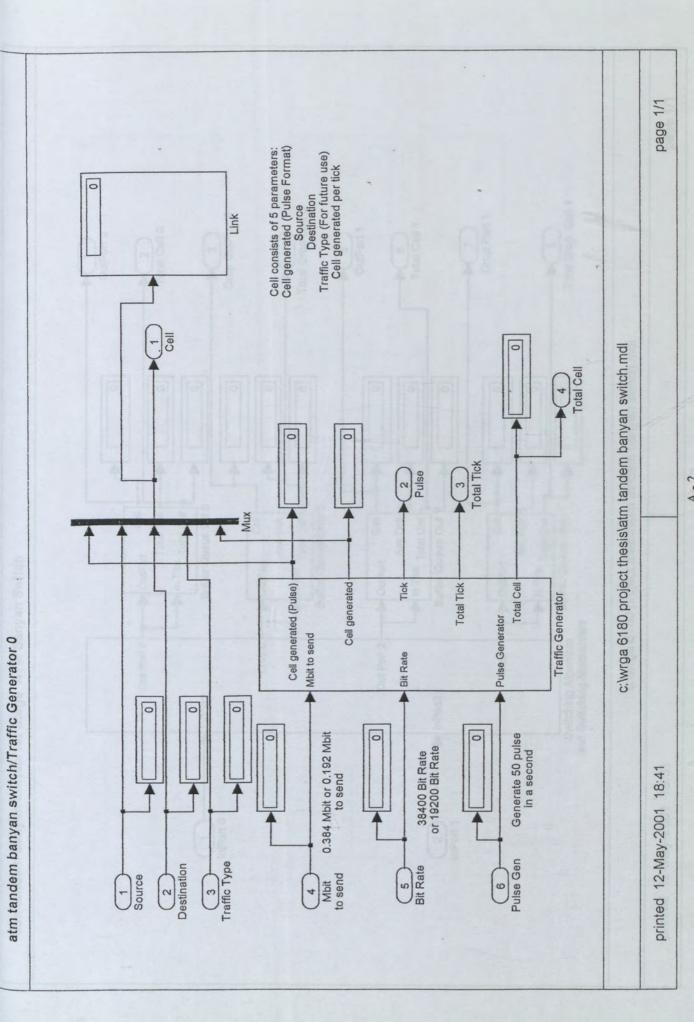

| 4.4 TRAFFIC GENERATOR MODEL                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.4.1 Traffic Generator Model                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.4.2 Sample Generator Model                                                                                                                                                                                                                                                                                                                                                                                  |

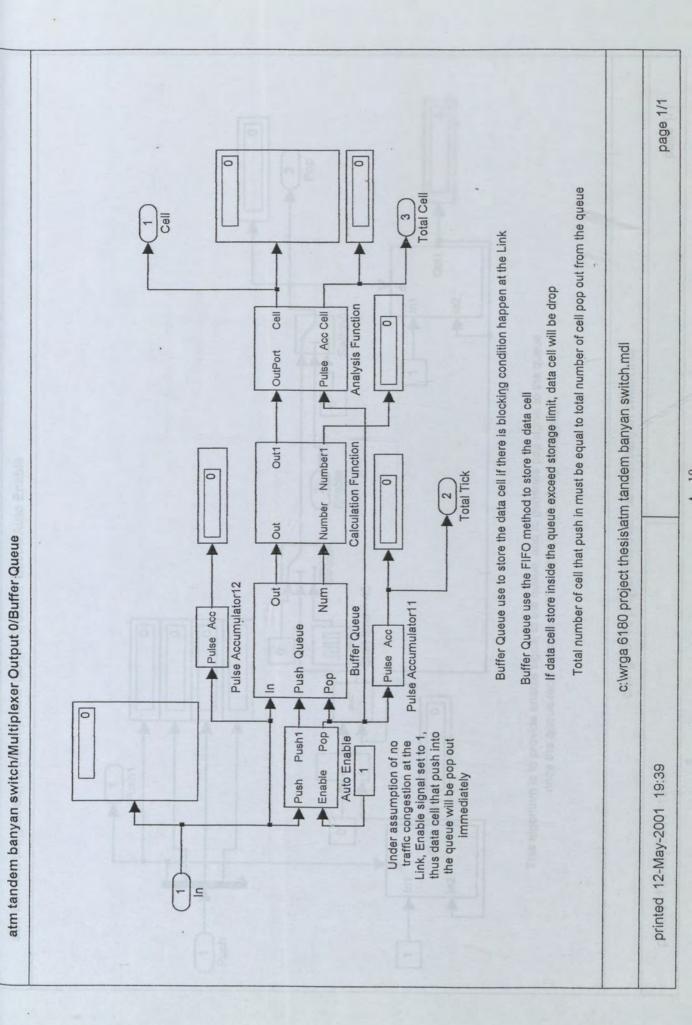

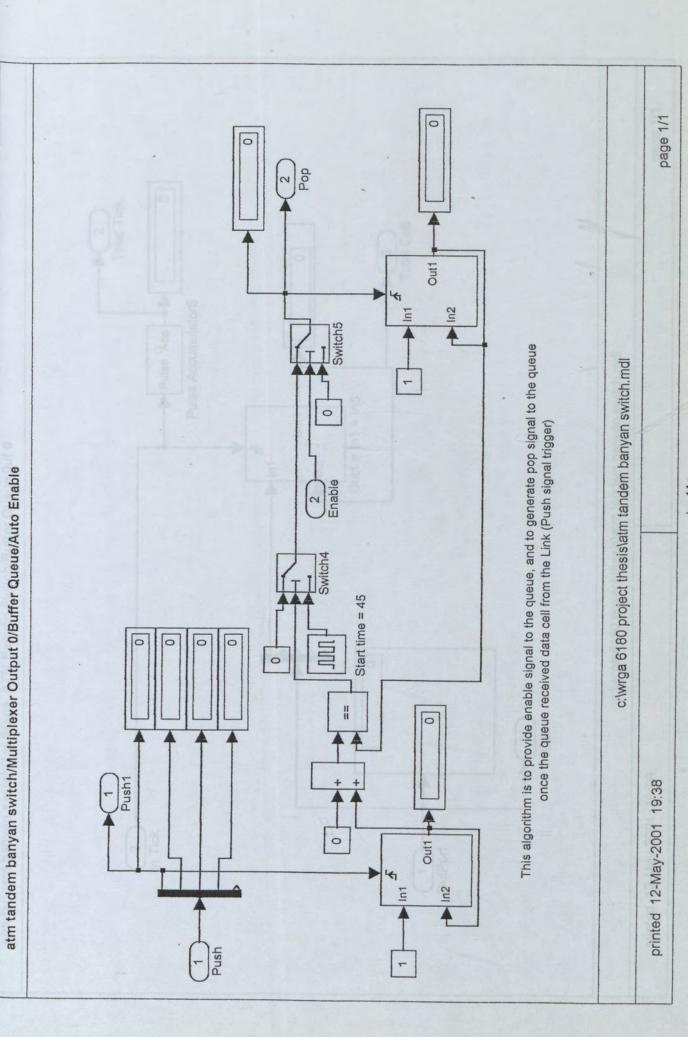

| 4.4.3 Buffer Queue Model                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.4.4 Link Size Model                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.4.5 Control Algorithm Model                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.4.5 Control Mechanism Model                                                                                                                                                                                                                                                                                                                                                                                 |

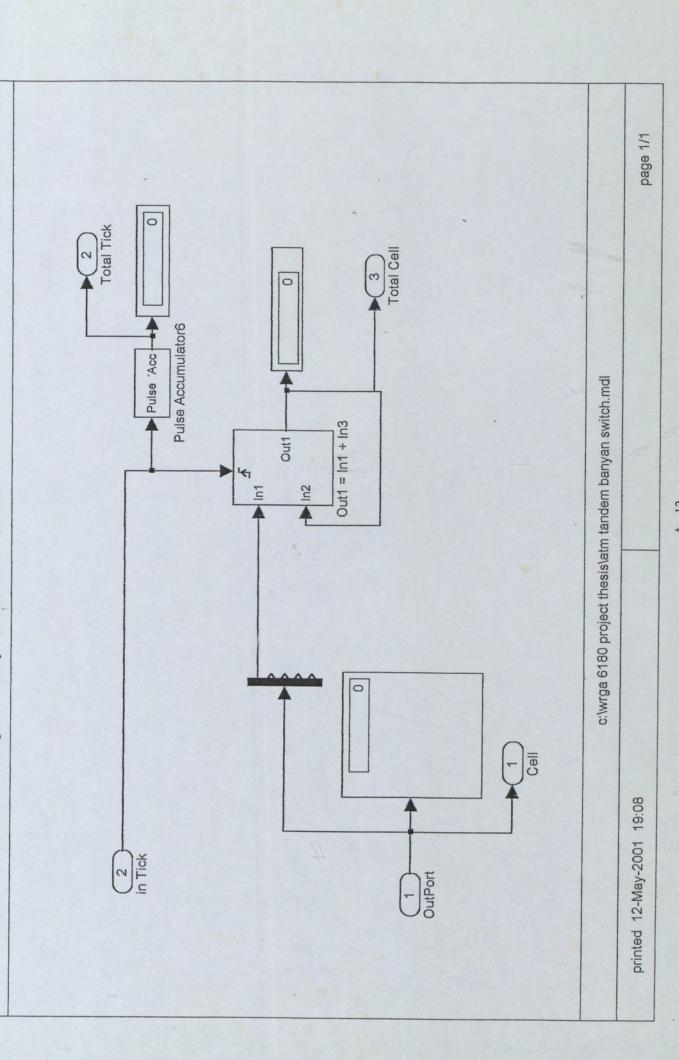

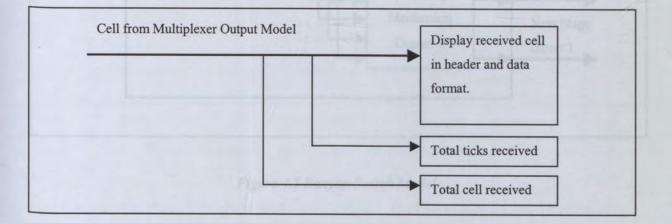

| 4.5 OUTPUT DISPLAY MODEL                                                                                                                                                                                                                                                                                                                                                                                      |

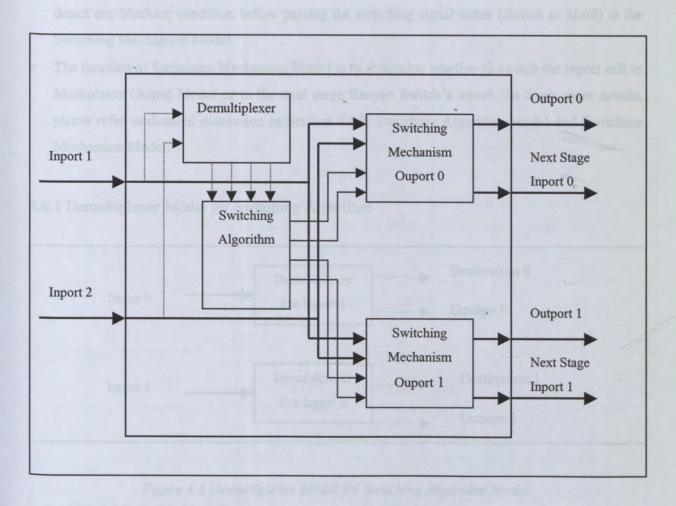

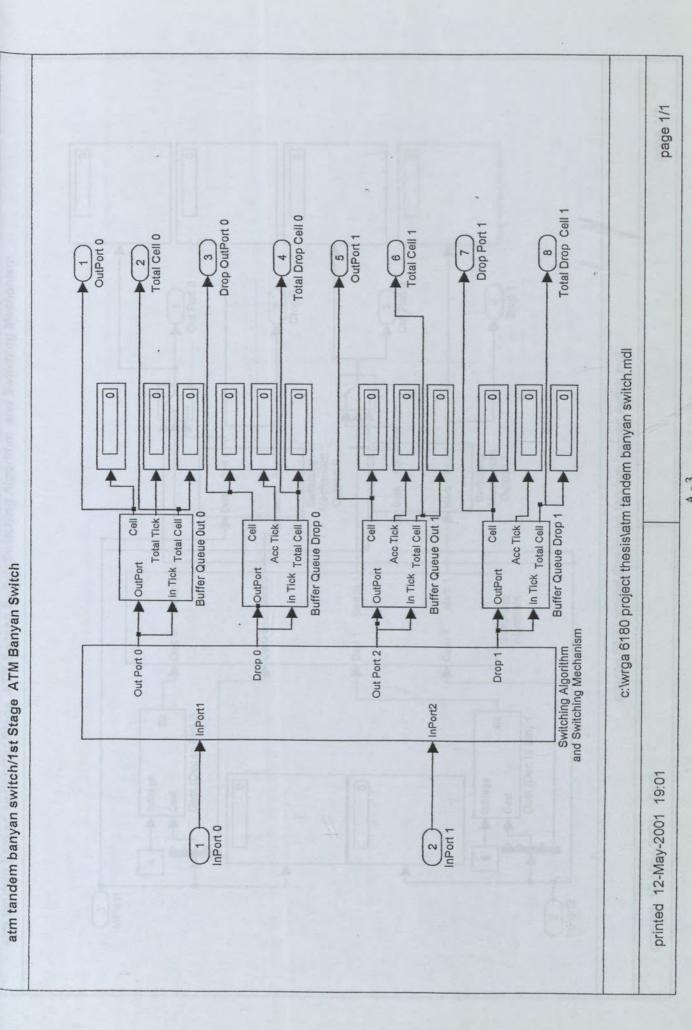

| 4.6 BANYAN SWITCH MODEL                                                                                                                                                                                                                                                                                                                                                                                       |

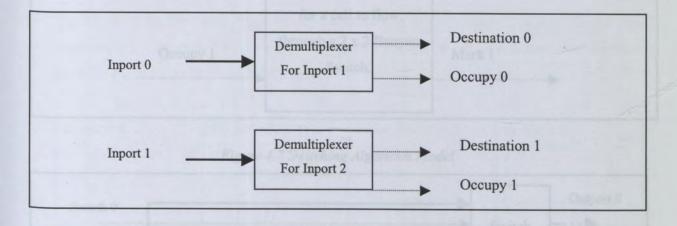

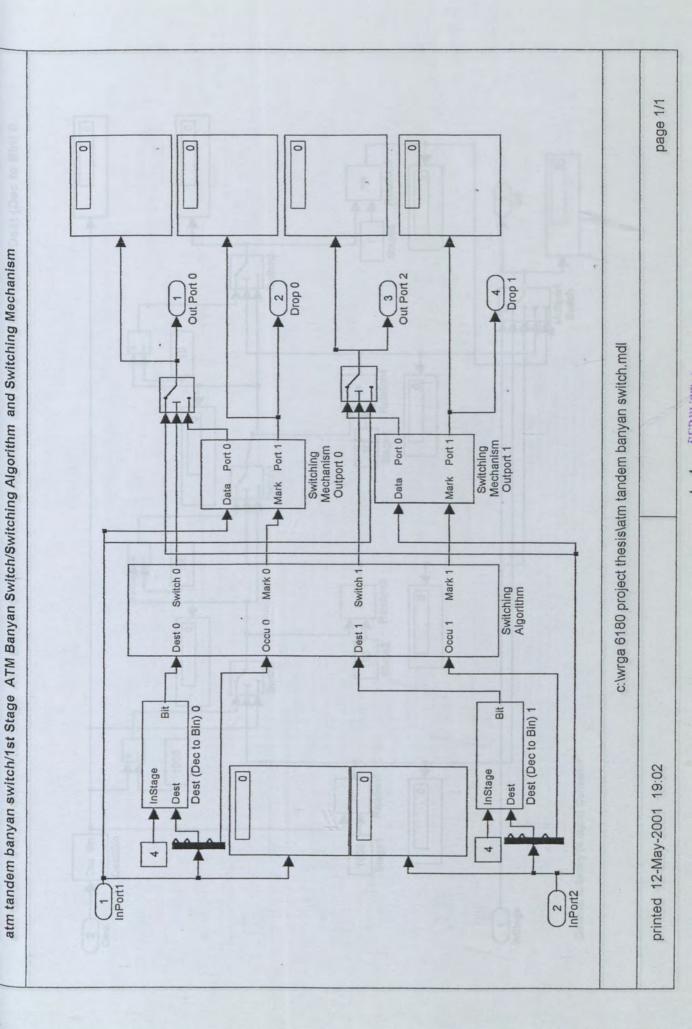

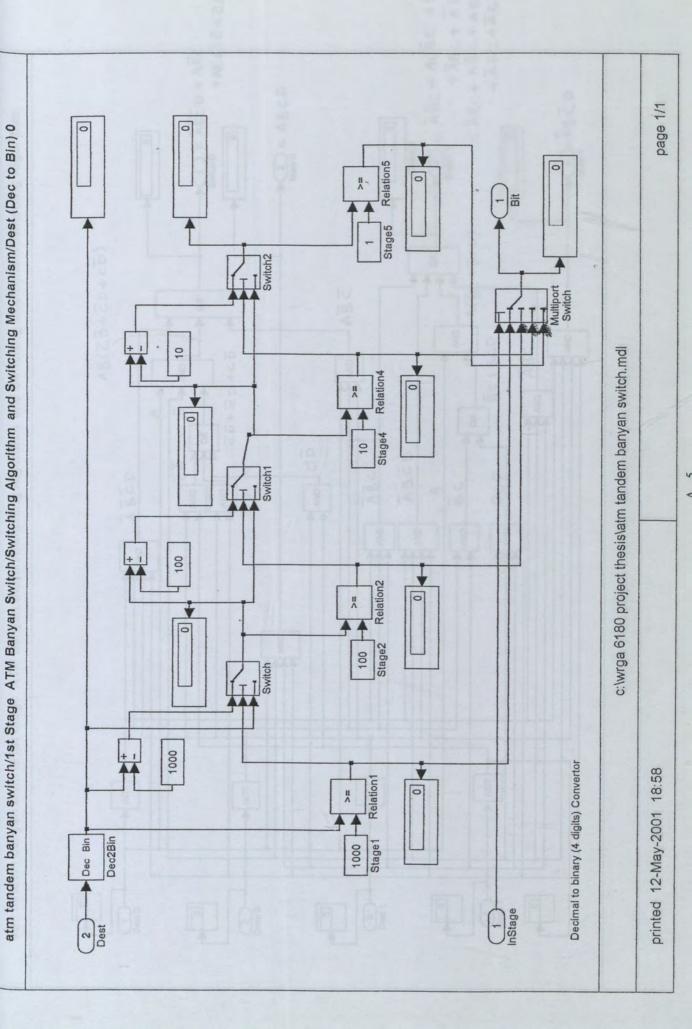

| 4.6.1 Demultiplexer Model for Switching Algorithm                                                                                                                                                                                                                                                                                                                                                             |

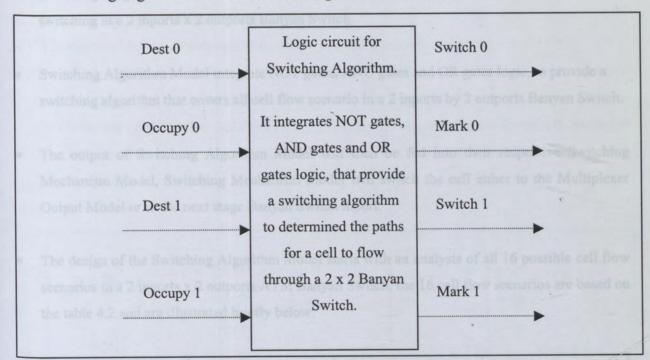

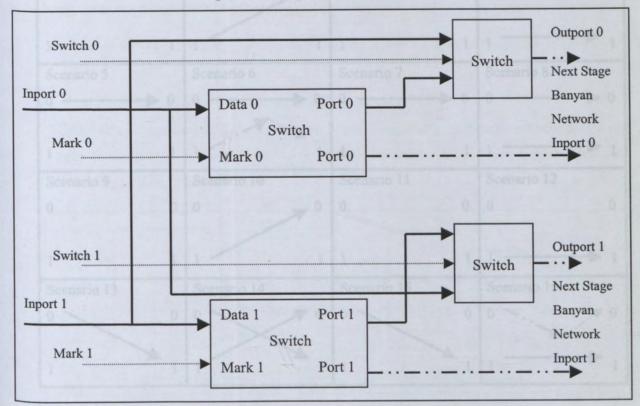

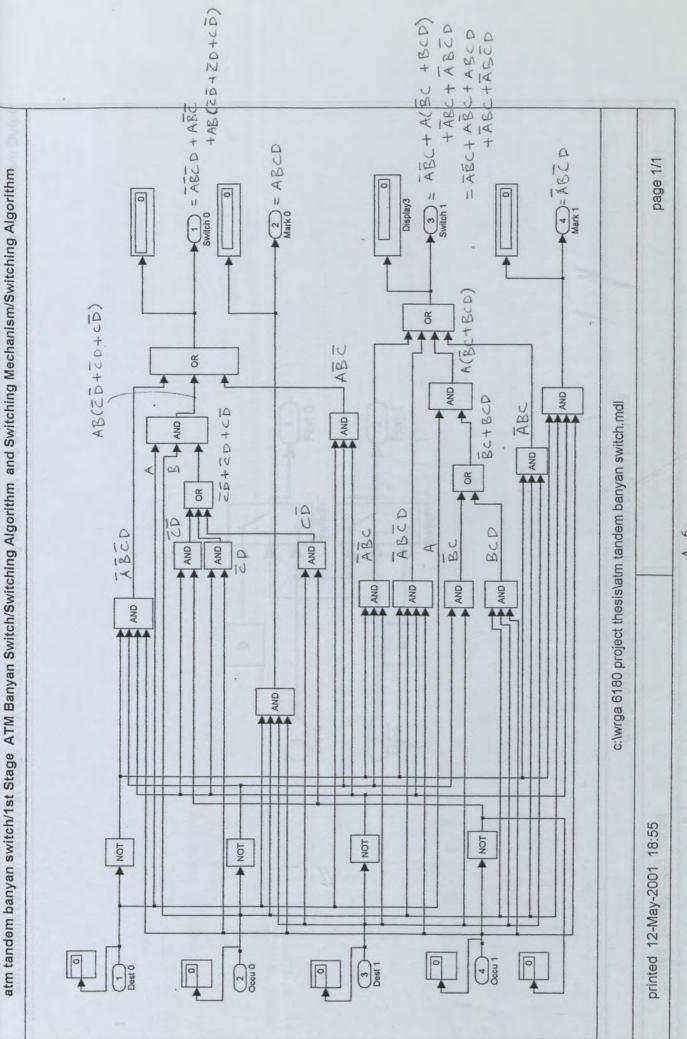

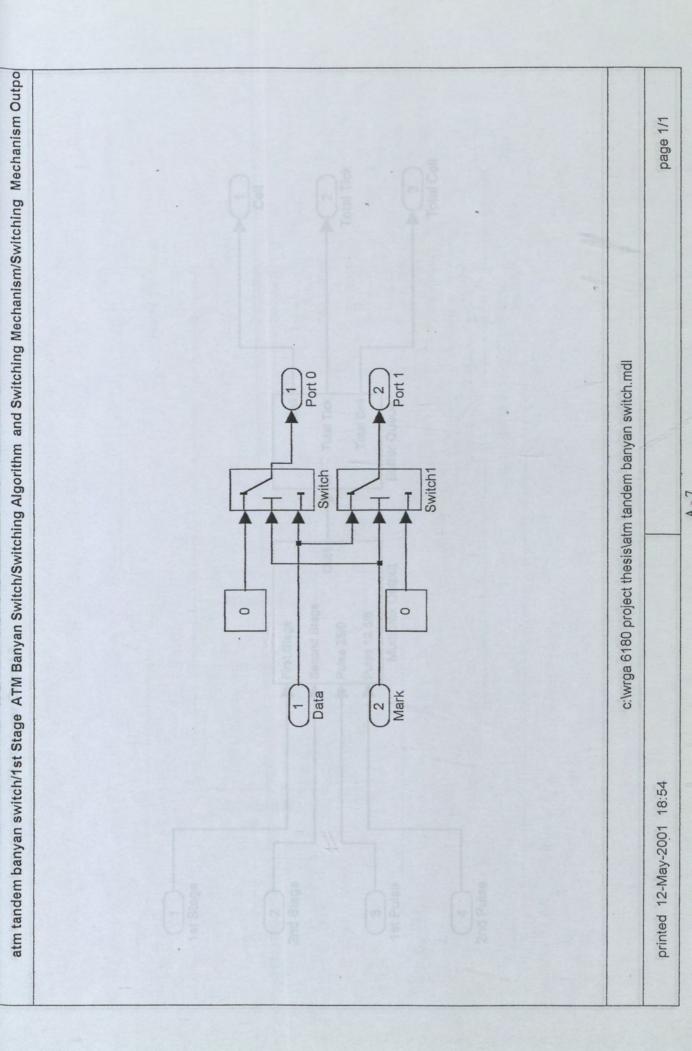

| 4.6.2 Switching Algorithm Model and Switching Mechanism Model                                                                                                                                                                                                                                                                                                                                                 |

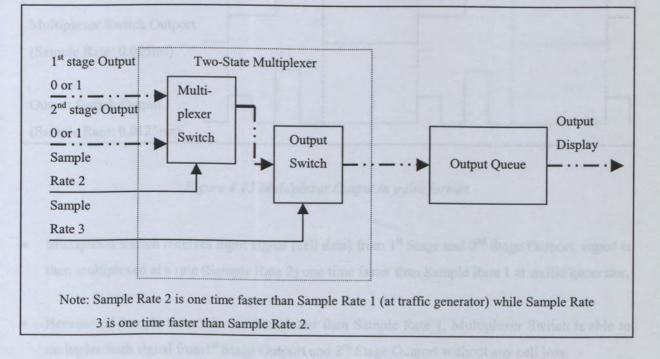

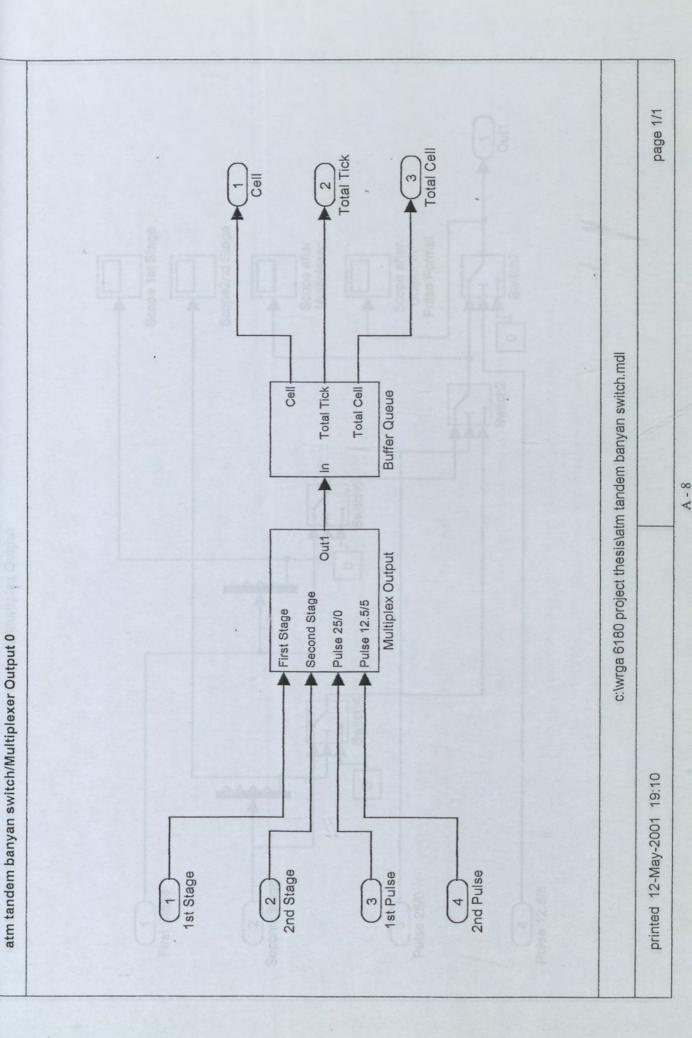

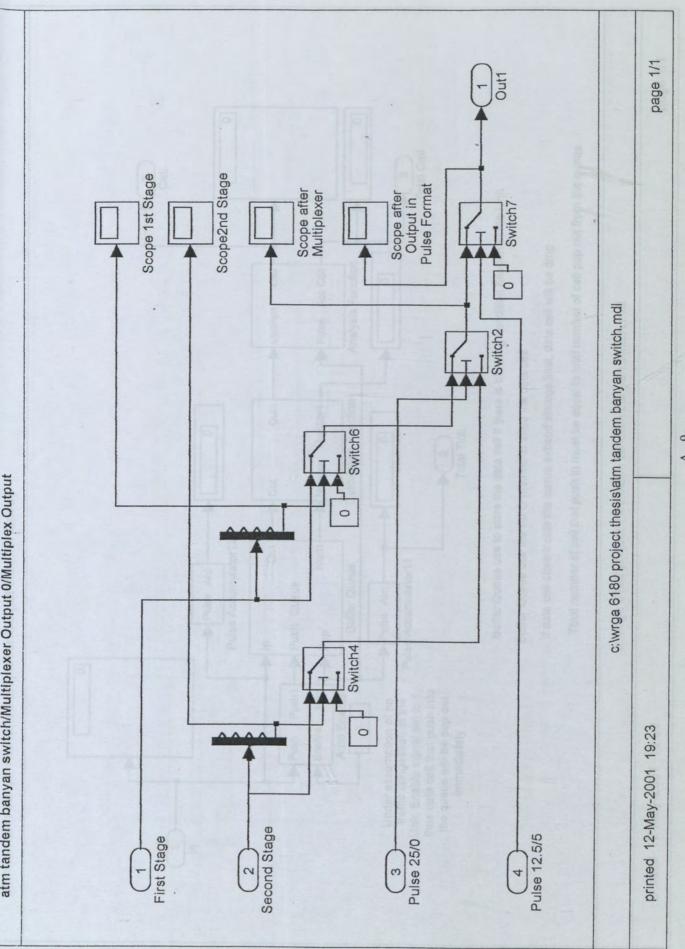

| 4.6.3 Multiplexer Output Model                                                                                                                                                                                                                                                                                                                                                                                |

| CHAPTER 5 DISCUSSIONS AND CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                         |

| 5.1 TWO STAGE ATM TANDEM BANYAN SWITCH SIMULATION                                                                                                                                                                                                                                                                                                                                                             |

| 5.1.1 No cell flow between Inport and Outport of the switch                                                                                                                                                                                                                                                                                                                                                   |

| 5.1.2 Cell flow from one inport to one outport                                                                                                                                                                                                                                                                                                                                                                |

| 5.1.3 Cell flow from two inports to two different outports                                                                                                                                                                                                                                                                                                                                                    |

| 5.1.4 Cell flow from two inports to the same outports                                                                                                                                                                                                                                                                                                                                                         |

| 5.2 DISCUSSION ON SIMULATION RESULT                                                                                                                                                                                                                                                                                                                                                                           |

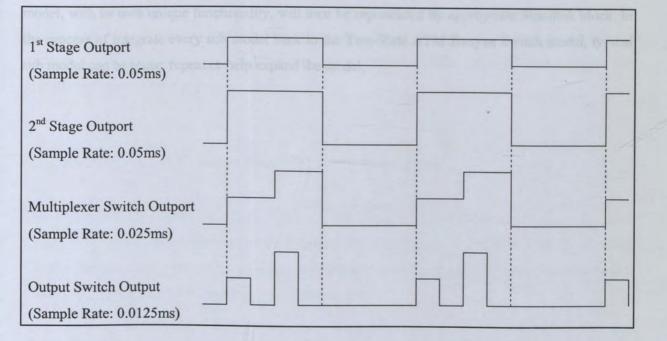

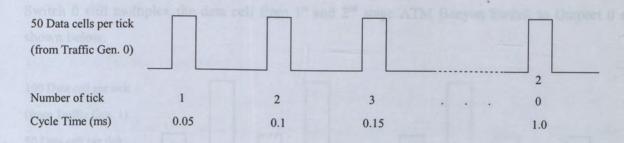

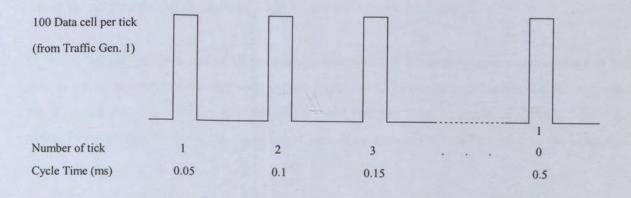

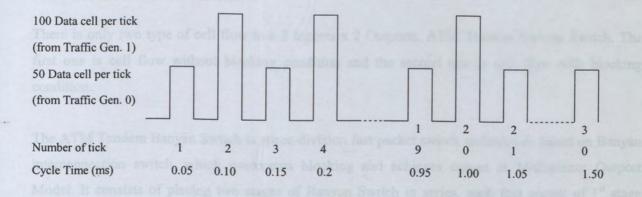

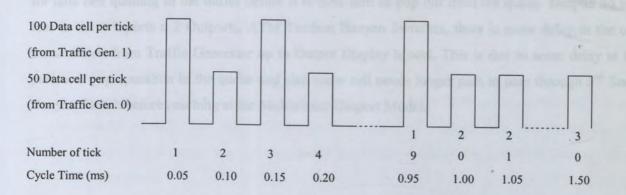

| Tick defined as cycle time for a specific sample rate. For example:                                                                                                                                                                                                                                                                                                                                           |

| Sample Rate 1 (0.05ms) at Banyan Switch means one tick will required 0.05ms                                                                                                                                                                                                                                                                                                                                   |

| Sample Rate 2 (0.025ms) at Multiplexer Switch means one tick will only required 0.025ms                                                                                                                                                                                                                                                                                                                       |

| 5.2.1 Example of Cell Flow without Blocking Condition                                                                                                                                                                                                                                                                                                                                                         |

| 5.2.2 Example of Cell Flow with Blocking Condition                                                                                                                                                                                                                                                                                                                                                            |

| 5.2.3 Overall Result Discussion                                                                                                                                                                                                                                                                                                                                                                               |

## Table of Contents

| 5.3 ASSUMPTIONS                                          |    |

|----------------------------------------------------------|----|

| 5.4 ADVANTAGE OF DYNAMIC MODELLING AN ATM BANYAN SWTICH  |    |

| 5.5 LIMITATION OF DYNAMIC MODELLING AN ATM BANYAN SWITCH |    |

| 5.6 AREAS OF ENHANCEMENTS                                |    |

| 5.7 OVERALL CONCLUSION                                   | 86 |

| BIBLIOGRAPHY                                             |    |

# LIST OF FIGURES

| FIGURE 1.1 THE CELL FORMAT FOR UNI (LEFT) AND NNI (RIGHT)                                          | 3  |

|----------------------------------------------------------------------------------------------------|----|

| - ALTRONOMICS CONTRACTOR                                                                           |    |

| FIGURE 2.1: A GENERIC SWITCHING MODEL                                                              | 14 |

| FIGURE 2.2 BASIC STRUCTURE OF A SHARED-MEMORY SWITCH                                               | 19 |

| FIGURE 2.3 A SHARED BUS SWITCH.                                                                    | 20 |

| FIGURE 2.4 A FULLY INTERCONNECTED SWITCH                                                           | 21 |

| FIGURE 2.5 SWITCHING ELEMENT, 4X4 BANYAN NETWORK AND 8X8 BANYAN NETWORK                            | 23 |

| FIGURE 2.6 THE VARIOUS BUFFERING APPROACHES.                                                       | 26 |

| FIGURE 2.7 EXAMPLE OF SWITCH ARCHITECTURE                                                          | 29 |

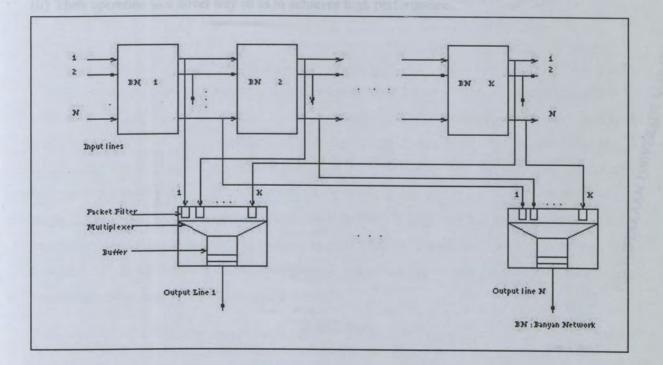

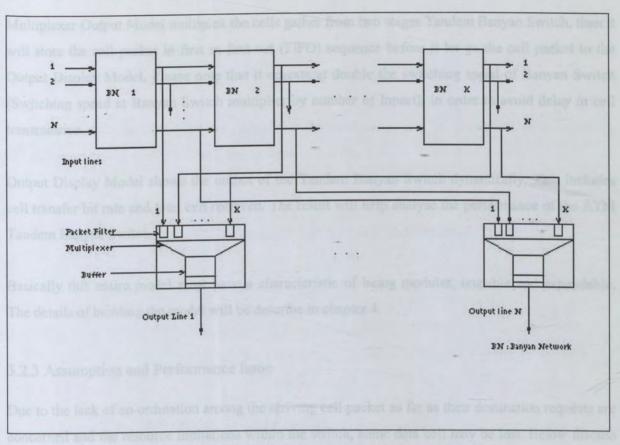

| FIGURE 2.8 ATM TANDEM BANYAN SWITCH ARCHITECTURE                                                   |    |

| FIGURE 2.9 KNOCKOUT SWITCHING ELEMENT.                                                             | 32 |

| FIGURE 2.10 KNOCKOUT BUS INTERFACE                                                                 | 33 |

|                                                                                                    |    |

| FIGURE 3.1 MODELLING AND SIMULATION CYCLE.                                                         | 39 |

| FIGURE 3.2 ARCHITECTURE OF AN ATM TANDEM BANYAN SWITCH                                             | 42 |

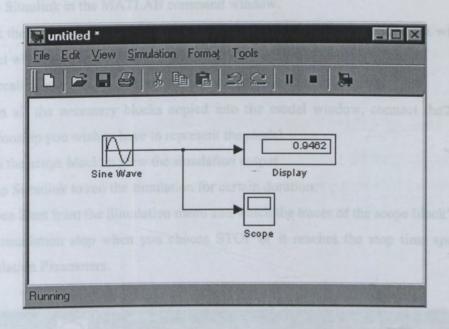

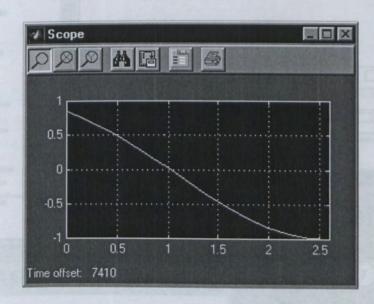

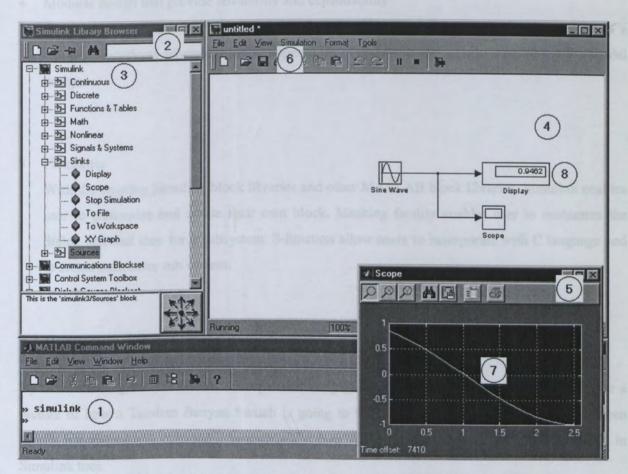

| FIGURE 3.3 SIMULINK BLOCK LIBRARY                                                                  | 47 |

| FIGURE 3.4 AN EXAMPLE OF SIMPLE SIMULINK MODEL                                                     | 48 |

| FIGURE 3.5 AN EXAMPLE OF SCOPE                                                                     | 48 |

| FIGURE 3.6 LAYOUT OF SIMULINK SOFTWARE ON THE COMPUTER SCREEN                                      | 49 |

|                                                                                                    |    |

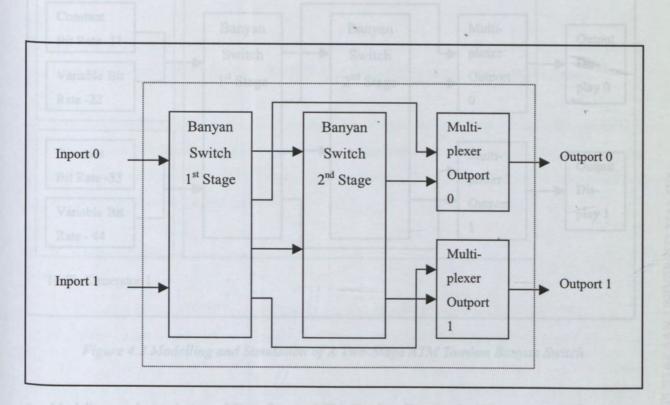

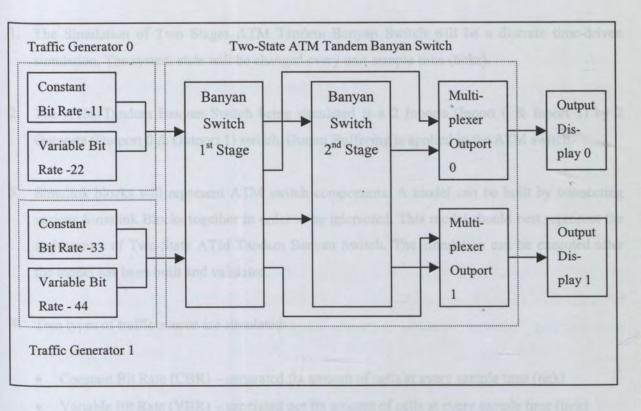

| FIGURE 4.1: TWO-STAGE ATM TANDEM BANYAN SWITCH MODEL.                                              | 52 |

| FIGURE 4.2 MODELLING AND SIMULATION OF A TWO-STAGE ATM TANDEM BANYAN SWITCH.                       | 53 |

| FIGURE 4.3 TRAFFIC GENERATOR MODEL                                                                 | 59 |

| FIGURE 4.4 OUTPUT DISPLAY MODEL                                                                    | 53 |

| FIGURE 4.5 BANYAN SWITCH MODEL                                                                     | 54 |

| FIGURE 4.6 DEMULTIPLEXER MODEL FOR SWITCHING ALGORITHM MODEL                                       | 55 |

| FIGURE 4.7 SWITCHING ALGORITHM MODEL                                                               | 56 |

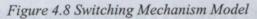

| FIGURE 4.8 SWITCHING MECHANISM MODEL                                                               | 56 |

| FIGURE 4.9 ALL 16 POSSIBLE CELL FLOW SCENARIOS IN A 2 INPORTS X 2 OUTPORTS ATM BANYAN SWITCH       | 57 |

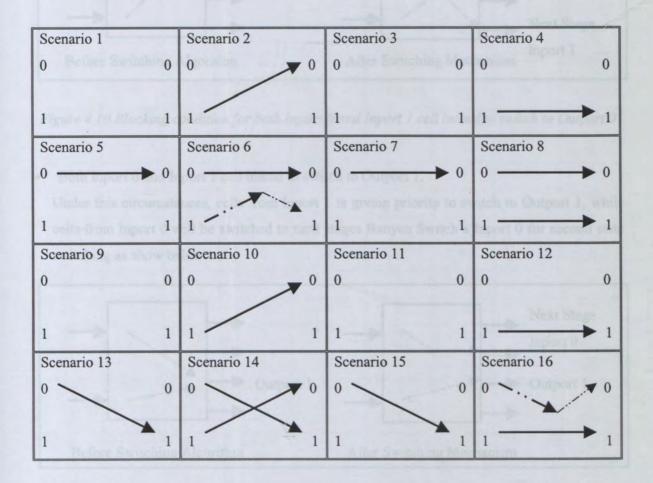

| FIGURE 4.10 BLOCKING CONDITION FOR BOTH INPORT 0 AND INPORT 1 CELL INTEND TO SWITCH TO OUTPORT 0.0 | 58 |

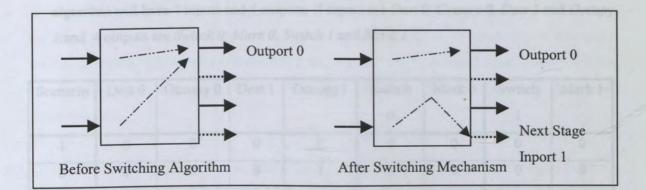

| FIGURE 4.11 BLOCKING CONDITION FOR BOTH INPORT 0 AND INPORT 1 CELL INTEND TO SWITCH TO OUTPORT 1.0 | 58 |

| FIGURE 4.12 MULTIPLEXER OUTPUT MODEL                                                               | 71 |

| FIGURE 4.13 MULTIPLEXER OUTPUT IN PULSE FORMAT                                                     | 72 |

# LIST OF TABLES

| TABLE 4.1 N | MOSTLY USED SIMULINK BLOCK                                |

|-------------|-----------------------------------------------------------|

| TABLE 4.2 L | LOGIC EXPRESSION FOR SWITCHING ALGORITHM MODEL THAT COVER |

| A           | ALL 16 CELL FLOW SCENARIOS                                |

TABLE 5.1 CELL FLOW PATTERN FOR A 2 INPORTS X 2 OUTPORTS ATM BANYAN SWITCH

77

| Ceil Transfer Delay       |  |

|---------------------------|--|

|                           |  |

|                           |  |

|                           |  |

| Hender Error Control      |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

| Synchronous Transfer Mode |  |

|                           |  |

|                           |  |

|                           |  |

Acronyms

# ACRONYMS

| ATM   | Asynchronous Transfer Mode                     |

|-------|------------------------------------------------|

| ABR   | Available Bit Rate                             |

| CAC   | Connection Admission Control                   |

| CBR   | Constant Bit Rate                              |

| CDV   | Cell Delay Variation                           |

| CLR   | Cell Loss Ratio                                |

| CTD   | Cell Transfer Delay                            |

| DEMUX | Demultiplexer                                  |

| FIFO  | First In First Out                             |

| GUI   | Graphical User Interface                       |

| HEC   | Header Error Control                           |

| IM    | Input Module                                   |

| ISDN  | Integrated Services Digital Network            |

| ITU   | International Telecommunication Union          |

| LAN   | Local Area Network                             |

| MINs  | Multistage Interconnection Networks            |

| MUX   | Multiplexer                                    |

| NIST  | National Institute of Standards and Technology |

| NNI   | Network-Node Interface                         |

| NPC   | Network Parameter Control                      |

| OAM   | Operation and Maintenance                      |

| ОМ    | Output Module                                  |

| OPNET | Optimised Network Engineering Tool             |

| QoS   | Quality of Services                            |

| SM    | Switch Management                              |

| SONET | Synchronous Optical Network                    |

| STM   | Synchronous Transfer Mode                      |

| TBSA  | Tandem Banyan Switch Architecture              |

| TDM   | Time Division Multiplexing                     |

| UBR   | Unspecified Bit Rate                           |

|       |                                                |

Acronyms

| UNI  | Unified Network Interface    |                                                |

|------|------------------------------|------------------------------------------------|

| UPC  | Usage Parameter Control      |                                                |

| VC   | Virtual Connection           |                                                |

| VCC  | Virtual Channel Connection   |                                                |

| VCI  | Virtual Channel Identifier   |                                                |

| VoIP | Voice over Internet Protocol | anation appreciate Listy, the superity and the |

| VPI  | Virtual Path Identifier      |                                                |

| www  | World Wide Web               |                                                |

|      |                              |                                                |

Asynchronome Transfer Mode (ATM) is based on the switching and multiplexing technique selected by the International Telecommunication Union (ITU) for the broadband secess for ISDN. ATM transports information in fixed size packets that are commonly known as ATM cells. ATM cell is fixed-size packet that is 53 outers. The 53-byte cell is divided into 5-byte header and 45-byte data. When the physical data transfer becomes extremely reliable, as in ATM, it makes more sense to do the relaying of packets in the lower layers. This reduces the extra overhead ensociated with the more traditional networking protocols designed for unreliable physical lines.

By using a fixed-size will, ATM protocol contributes to the following adventages [CHKO 99]

Simple hardware implementation for switching ATM cells.

This is a big advantage, because the system only needs to take care about 53 byte cells with 5byte fixed beaders. The data contain inside the beatler will provide information to ATM switch whether so route that particular cell or not when it comes to a congestion simution.

Efficient use of available bandwidth for autive connections.

Fixed see header and data enable ATM switch to efficiently plan the switch logic by comparing the priority bit in the 5-byte header.

Fair sharing of the available bandwidth among applications.

Because of the fixed short size cell, ATM does not take over the handwidth availability too long when compared with the protocol that has variable size data packets. It is also ensier to

# **Chapter 1: Introduction to ATM Switch and ATM Simulation Software**

This chapter briefly explains ATM technology and the Simulation concepts. ATM technology and ATM Switch are introduced here, this is followed by the introduction of the simulation concepts, Simulink tools and some examples of ATM simulation application. Lastly, the objective and the organisation of this dissertation will be introduced.

# 1.1 Introduction to Asynchronous Transfer Mode (ATM) Technology

Asynchronous Transfer Mode (ATM) is based on the switching and multiplexing technique selected by the International Telecommunication Union (ITU) for the broadband access for ISDN. ATM transports information in fixed-size packets that are commonly known as ATM cells. ATM cell is fixed-size packet that is 53 octets. The 53-byte cell is divided into 5-byte header and 48-byte data. When the physical data transfer becomes extremely reliable, as in ATM, it makes more sense to do the relaying of packets in the lower layers. This reduces the extra overhead associated with the more traditional networking protocols designed for unreliable physical links.

By using a fixed-size cell, ATM protocol contributes to the following advantages [CHIO 99]:

Simple hardware implementation for switching ATM cells.

This is a big advantage, because the system only needs to take care about 53-byte cells with 5byte fixed headers. The data contain inside the header will provide information to ATM switch whether to route that particular cell or not when it comes to a congestion situation.

Efficient use of available bandwidth for active connections.

Fixed size header and data enable ATM switch to efficiently plan the switch logic by comparing the priority bit in the 5-byte header.

• Fair sharing of the available bandwidth among applications.

Because of the fixed short size cell, ATM does not take over the bandwidth availability too long when compared with the protocol that has variable size data packets. It is also easier to

implement the fair share of the bandwidth when queuing is needed, because each cell represents a fixed amount of data.

Robust and efficient end-to-end data loss recovery.

As each cell that is received at the destination is labelled uniquely, loss cell can be easily identified, only this loss cell needs to be sent back to sender, this reduces the amount of data need to be re-sent.

• Suitability for all kinds of information traffic.

By using 53-octet cells, ATM can give fair access to information traffic likes voice, video and data. No one traffic type can take over the line to an extent that hinders other traffic types. Sequential deliveries of cells allow certain types of information transfer to continue operation, even though a particular cell was lost. Guaranteed rate can provide quality service to certain traffic types like voice, that requires a steady, constant transfer rate.

Better accommodation of LAN Bursty Traffic.

LAN traffic is bursty in nature and uses whatever bandwidth is available. ATM, with its fair use of the bandwidth, guaranteed rate, and priority mode, will benefit LAN to extend its performance beyond other traffic types.

# 1.1.1 Quality of Service and Service Categories

A set of parameters is negotiated when a connection is set up on ATM networks. These parameters are used to measure the Quality of Service (QoS) of a connection and quantify end-to-end network performance at the ATM layer. The network should guarantee the QoS by meeting certain values likes Cell Transfer Delay (CTD), Peak-to-peak Cell Delay Variation (CDV) and Cell Loss Ratio (CLR). ATM is able to provide desired QoS for different applications. For example, voice is delay-sensitive but not loss sensitive, data is loss-sensitive but not delay sensitive, while some other applications may be both delay-sensitive and loss-sensitive [LUFA 95]. Those ATM service categories such as Constant Bit Rate (CBR) and Variable Bit Rate (VBR) services allow ATM to accommodate fixed-rate, least-line types of connections (i.e. voice and video) as well as bursty-style LAN connections. VBR service allows a certain sustainable for LANs. The Unspecified Bit Rate

(UBR) and Available Bit Rate (ABR) provide the options to use available bandwidth in the network [CHIO 99].

# 1,1.2 ATM Cell Format

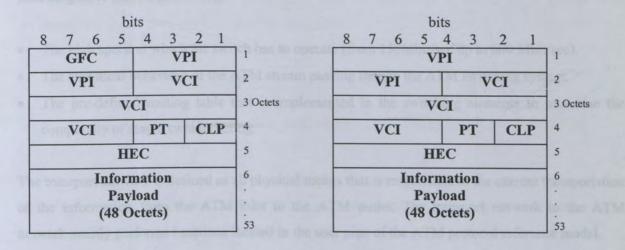

ATM layer supports cell switching based on ATM cells. An ATM cell contains 53 octets and has two parts: a 5-octets header and a 48-octet payload or information field. Some of the important bits like source bit, destination bit and priority bit is contained in the header. ATM protocol has two interface definitions: UNI and NNI. A minor difference exists between the cell header format for UNI and NNI [CHIO 99], as show in Figure 1.1.

Figure 1.1 The cell format for UNI (left) and NNI (right)

ATM network service is connection-oriented by establishing a virtual connection (VC) between a source and a destination. The VC is dedicated to the pair of source and destination. More than one VC can be established through a physical link. The VCs are referred as virtual channel connections (VCCs). VCCs that have same end points are grouped together to become a single virtual path connection (VPC). Each VCC has virtual channel identifier (VCI) and pair with a virtual path identifier (VPI), the VCC will have a unique connection identifier [TAYS 00]. In this dissertation, VCI can be considered as the source bit for the Inport or destination bit for Outport.

# 1.2 ATM Switch

ATM switches are used to connect ATM host and networks. Each switch contains a routing table that consists of in/out pair of switch port and connection identifiers. Switching happens in the switches where incoming channels will be mapped to appropriate outgoing channels.

An ATM switching system is much more than a fabric that simply routes and buffers cells, rather it comprises an integrated set of modules. Switching systems not only relay cells, but also perform control and management functions. Furthermore, they must support a set of traffic control requirements Thus a good design of ATM switching architecture takes into consideration the following three factors [BIRA 94]:

- The high speed at which the switch has to operate (from 150Mbit/sec up to 600 Mbit/sec).

- The statistical behaviour of the ATM stream passing though the ATM switching system.

- The pre-defined routing table that is implemented in the switching elements to minimise the complexity of single switch routing.

The transport network is defined as all physical means that is responsible to the current transportation of the information from the ATM inlet to the ATM outlet. The transport network in the ATM network mainly performs functions located in the user plan of the ATM protocol reference model.

The control part of the switch is that which controls the transport network. It decides for instance, which inlet to connect to which outlet. The decision is based on incoming signalling information. The control network mainly performs functions located in the control plane of the ATM protocol reference model.

# 1.2.1 ATM Switch Functions

ATM is connection oriented. All cells belong to a virtual connection pre-established by the transport network. The ATM cell is 53 bytes long, built of 48 payload bytes and a 5-byte header. Each cell's header contains a VCI (Virtual Channel Identifier) that identifies the virtual connection to which the cell belongs. ATM switch has several main tasks [BIRA 94]:

VCI Translation

The established connection on the ATM network defines the virtual path through different switches across the network. The VCI is local to each switch port. As each cell travels across an ATM switch, the VCI is translated into a new value. The switch has to build a new cell header containing the new VCI (any possibly new VPI – virtual path identifier).

Switching – Cell transport from its input to its output.

The transportation of the information (cell) from an incoming logical ATM channel (Inport) to an outgoing logical ATM channel (Outport) is also the responsibility of the ATM switch. Two identifiers characterise the logical ATM channel:

- a) The physical Inport/Outport which is characterised by a physical port number.

- b) The logical channel on the physical port, which is identified by the VCI and/or the VPI.

In order to provide the switching function, both physical and logical identifiers of the incoming cell have to related to physical and logical identifiers of the outgoing cell. Two functions have to be implemented in the ATM switching system.

The first function is the space switching function. The space switching is the one which allows the connection between inputs. An important aspect of space switching is the internal routing. This means how the information is routed internally in the switch. The internal structure of the switch must allow connect between input and output.

The second function is time switching. Since ATM is working in an asynchronous mode, cells, which had arrived in various time slots from the different inputs, can be delivered from different outputs in different time slots (There is no time identifier in ATM as it is in STM). Since there is no preassigned time slot connection, a contention problem arises if more than two logical channels are connected to the same output at the same time slot. However, implement a queuing function in the ATM switch system will solve this problem in the ATM switch.

# **1.3 ATM Switch Simulation**

ATM Switch Simulation helps form an idea to the ATM Switch design in the complex network architectures and topologies. Even though the advent of high speed ATM switching solutions, ATM switch simulations allow designers to make informed decisions without need to invest in the physical hardware. Designers can carry out the performance related studies using simulation and therefore avoid the burden of the "trial and error" implementations.

## 1.3.1 Simulation

Simulation is the basic tool to help making a correct decision. Decisions are formulated based on the information resulting from the simulation A number of factor influences the probability of making a correct decision. These are summarised as below [OPNE 99]:

- The level of understanding of a problem A problem should be well defined and manageable. A clear understanding of the problem is essential before a simulation model can be developed.

- Correct Model It is paramount that the model correctly simulates the problem. A software

model may be often be syntactically correct but might not accurately simulate the problem area

being addressed. It is essential that the model being designed and simulated in such a way that

allow the various experiments to be carried out and an appropriate simulation results to be

generated.

- Interpretation of Results The simulation model simply produces output data. This data must be manipulated and interpreted by the developer. The correct interpretation of this data is dependent on the usefulness of the output data and also the user's understanding of statistical methods.

# 1.3.2 Simulation Software

In the research field and software simulation market, quite a number of simulation software has been developed for ATM Network simulation, This simulation software allows designers or network planners to simulate network that they plan to set up. Simulation of ATM switch is normally part of the module in the simulation software. OPNET Simulator and ATM-NIST Network Simulator are the two examples.

OPNET, or Optimised Network Engineering Tool, can be described as a set of decision support tools, providing a comprehensive environment for the specification, simulation and performance analysis of communication networks, computer systems and applications, and distributed systems. OPNET has been designed to support the modelling and simulation of a large range of communication systems. Discrete event simulations are used as the means of analysing system performance and their behaviour. This sophisticated package comes complete with a range of tools which allows developers specify models in great detail, identify the elements of the model of interest, execute the simulation and analyse the generated output data [OPNE 99].

The key features of OPNET are summarised here as below:

- Objects Orientation OPNET is object oriented, where each object has a defined set of attributes. These configurable attributes result in a highly flexible development environment.

- Hierarchical Modelling OPNET perform modelling in a hierarchical approach, to describe any

communication network. Each level of the hierarchy, to describes different aspects of the model

being simulated. Models at the higher-level, to use model developed at one level lower of the

hierarchy. This lead to a highly flexible simulation environment where generic models can be

developed and it help to increase the reusability and expandability.

Another example of ATM network simulator is ATM NIST Network Simulator, it was developed at the National Institute of Standards and Technology (NIST) to provide a flexible test-bed for studying and evaluating the performance of ATM networks.

The ATM NIST Network Simulator allows users to create different network topologies, set the parameters of component operation, for example, users can select constant bit rate data to be generated, number of byte of data to be send, start time, end time and etc. All these parameters can be saved as different simulated configurations. While the simulation is running, various instantaneous performance measures, for example cell received and cell loss rate, can be displayed in graphical/text form or saved to files for subsequent analysis [NIST 94].

There are two major uses for the simulator. The first is as a tool for ATM network planning and the second is as a tool for ATM protocol performance analysis.

- As a planning tool, a network planner can run the simulator with various network configurations and traffic loads to obtain statistics such as utilisation of network links and throughput rates of virtual circuits.

- As a protocol analysis tool, a researcher or protocol designer could study the total system effect of a particular protocol. For example, one could investigate the effectiveness of various flow control mechanisms for ATM networks and address mechanisms such as: fair bandwidth allocation, protocol overhead, bandwidth utilisation, etc.

# **1.4 Introduction to Simulink**

Simulink is an extension to Matlab that uses an icon driven interface for construction of block diagram representation of a process. Matlab integrates computation, visualisation, and programming in an easy-to-use environment where problems and solutions are expressed in familiar mathematical notation. Matlab provide an interactive system that allows many technical-computing problems, such as mathematics formulation in the block function to be solved.

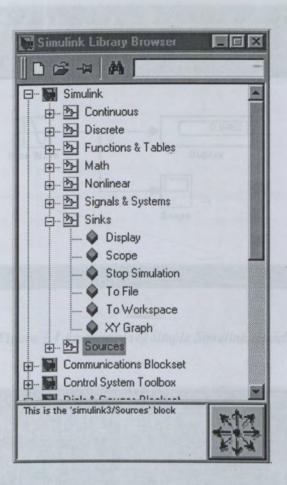

Simulink is an interactive tool that has a capability for modelling, simulating, and analysing dynamical system. Using Simulink, virtual prototypes can be built and tested quickly. This will help to minimise the effort of exploring the design concepts at any level of detail. Simulink provides an interactive, block diagram environment for modelling and simulating dynamic system. It includes an extensive library of predefined blocks that can be used to build graphical models of the system. Supported model type includes linear, non-linear, continuous time, discrete-time, multi-rate, conditionally executed, and hybrid system. Simulink provides a graphical user interface (GUI) for building models as block diagram, using click-and drag mouse operations. A comprehensive block library of sinks, sources, linear and non-linear components, and connectors has been included for the building of block diagram. Models are hierarchical, thus, model can build using both top-down and bottom-up approaches to create a simplified view of components or subsystem [SIMU 99].

Simulink provides a complete set of modelling tools that can be used to develop details block diagram model of a system. Features such as block libraries, hierarchical modelling, signal labelling, and subsystem "masking" provide a powerful set of capabilities for creating, modifying, and

maintaining block diagrams. The Simulink block library consists of over one hundred blocks, providing an extensive set of standard components. After studying various network simulation tools, it was concluded that Simulink would be an ideal tool for dynamically modelling the ATM switch operation.

# 1.5 Objectives of the Dissertation

The main objective of this dissertation is to dynamically model a simple ATM Tandem Banyan Switch. Different bit rate cell is flowed through the switch, and cell received at the switch's outport are being monitored for analysis. Throughout this dissertation, we have to achieve the objectives below:

- To discuss various ATM switching functions and requirements.

- To focus in depth, the cell switch fabric functionality.

- To study the switch design principle.

- To study the ATM Tandem Banyan Switch, focusing on the cell switch fabric and its sub components.

- To model the cell fabrics sub component using MATLAB Simulink software.

- To develop a dynamic modelling of a two-state ATM Tandem Banyan Switch simulation software.

- To run the simulation software and monitor the simulation result, change the process parameters and monitor the cell flow pattern change, compare and analyse the result.

- To discuss the results and conclude on the overall performance of the dissertation.

# 1.6 Scope of the Project

The followings are the scope of the project.

- The ATM switch consists of 2 Inports x 2 Outports.

- The ATM switch is Two-state Tandem Banyan type.

- Constant Bit Rate type and Variable Bit Rate type data are generated to pass through the ATM switch.

- Cell received at Outport can be monitored for its contents. For example, type of data, cell bit rate and Inport address.

# 1.7 The Structure of the Dissertation

The structure of this dissertation shall organise as below:

- Chapter 1 Introduction to ATM switch and ATM simulation software The ATM technology, ATM switch and ATM Simulation Software will be explored in this chapter, so that basic knowledge and concepts can be gained before go in depth at the following chapter.

- Chapter 2 ATM switch architecture, functionality, and design principle. ATM switch architecture, functionality and design principle are discussed here. The parameter that determines the performance of the switch is introduced here. Two type of Banyan Network is introduced, that is Tandem Banyan Switch and Knockout Switch.

# Chapter 3 Introducing to MATLAB Simulink tool. The MATLAB Simulink tool is explained in this chapter. This includes the introduction to the Simulink tool, the advantage of using Simulink tool, the modelling concept, the Simulink toolbox and its basic Simulink block that is used in this project.

Chapter 4 Development of ATM switch simulation using MATLAB Simulink. Development of ATM switch simulation using MATLAB-Simulink is discussed in detail. This includes determination of the simulation requirement and assumption, structure of the ATM switch functional block, determines the simulation parameter, builds the function block using Simulink tool, and test runs the simulation.

# Chapter 5 Discussion and Conclusion

The testing result of the switch simulation is discuss and analyse here. Conclusion will be made on the overall performance of the switch simulation, which is run by MATLAB-Simulink. Area of enhancement and suggestion will be make if there is any.

# **Chapter 2: ATM Switch Architecture, Functionality and Design Principle**

In the first chapter, basic knowledge of ATM technology, ATM switch, simulation and Matlab-Simulink Tool have been introduced. Chapter 2 will explain the ATM switch in more detail. This includes ATM switch function, various ATM switch architecture, cell switch fabric and designs principle.

## 2.1 Switching Functions

An ATM switch contains a set of input ports and output ports, through which it is interconnected to users, other switches, and other network elements. It might also have other interfaces to exchange control and management information with special purpose networks. In general, the switch is assumed to perform cell relay and support control and management functions.

It is useful to examine the switching functions in the three-plane contexts, which is mentioned in the B-ISDN model [FAHM 95]:

#### 2.1.1 User Plane

The main function of an ATM switch is to relay data cells from input ports to the appropriate output ports. The switch processes only the cell headers and the payload is carried transparently. As soon as the cell comes in through the input port, the Virtual Path Identifier/Virtual Channel Identifier (VPI/VCI) information is derived and used to route the cells to the appropriate output ports. This function can be divided into three functional blocks: the input module at the input port, the cells switch fabric that performs the actual routing, and the output modules at the output ports.

#### 2.1.2 Control Plane

This plane represents functions related to the establishment and control of the VP/VC connections. Unlike the data cells, information in the control cells payload is not transparent to the network. The switch identifies signalling cells, and even generates some itself. The Connection Admission Control (CAC) carries out the major signalling functions required. Signalling information may not pass through the cell switch fabric, or maybe exchanged through a signalling network such as SS7.

#### 2.1.3 Management Plane

The management plane is concerned with monitoring and controlling the network to ensure its correct and efficient operation. These operations can be subdivided as fault management functions, performance management functions, configuration management functions, security management functions, accounting management function and traffic management function. These functions can be represented as being performed by the functional block Switch Management. The Switch Management is responsible for supporting the ATM layer Operations and Maintenance (OAM) procedures. OAM cells may be recognised and processed by the ATM switch. The switch must identify and process OAM cells, OAM cells may/may not pass through cell switch fabric.

## 2.1.4 Traffic Control Functions

The switching system may support connection admission control (CAC), usage/network parameter control (UPC/NPC), and congestion control. UPC/NPC functions are handled by the input modules, congestion control functions as handled by the Switch Management, while special buffer management actions (such as cell scheduling and discarding) are supervised by the Switch Management, but performed inside the cell switch fabric where the buffers are located.

# 2.2 A Generic ATM Switching Architecture

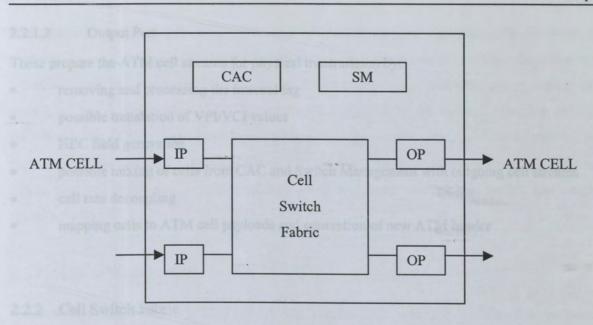

It will be useful to adopt a functional block model to simplify the discussion of various design alternatives. Switch functions defined previously can be divided according to its functional blocks such as input modules, output modules, cell switch fabric, connection admission control, and switch management. Figure 2.1 illustrates this switching model. These functional blocks are service-independent, and the partitioning does not always have well-defined boundaries between the functional blocks [CHEN 95].

IM = Input Port OM = Output Port CAC = Connection Admission Control SM = Switch Management

Figure 2.1 A generic switching model

# 2.2.1 Switch Interface

## 2.2.1.1 Input Port

The Input Port or Inport terminates the incoming signal and extracts the ATM cell stream. These involve signal conversion and recovery, processing ATM cell header, cell delineation and rate decoupling. After that, for each ATM cell the following functions should be performed:

- error checking the header using the Header Error Control (HEC) field

- validation and translation of VPI/VCI values

- determination of the destination output port

- passing signalling cells to CAC, and OAM cells to Switch Management

- usage/network parameter control (UPC/NPC) for each VPC/VCC

- internal tag containing internal routing and performance monitoring information for use only within the switch

#### 2.2.1.2 Output Port

These prepare the ATM cell streams for physical transmission by:

- removing and processing the internal tag

- possible translation of VPI/VCI values

- HEC field generation

- possible mixing of cells from CAC and Switch Management with outgoing cell streams

- cell rate decoupling

- mapping cells to ATM cell payloads and generation of new ATM header

## 2.2.2 Cell Switch Fabric

The cell switch fabric is primarily responsible for routing of data cells and possibly signalling and management cells as well. The next section (2.3) will focus on the cell switch fabric.

## 2.2.3 Connection Admission Control (CAC)

Establishes, modifies and terminates virtual path/channel connections. More specifically, it is responsible for:

- high-layer signalling protocols

- signalling ATM Adaptation Layer (AAL) functions to interpret or generate signalling cells

- interface with a signalling network

- negotiation of traffic contracts with users requesting new VPCs/VCCs

- renegotiations with users to change established VPCs/VCCs

- allocation of switch resources for VPCs/VCCs, including route selection

- admission/rejection decisions for requested VPCs/VCCs

- generation of UPC/NPC parameters

If the CAC is centralised, a single processing unit would receives signalling cells from the input modules, interpret them, and perform admission decisions and resource allocation decisions for all the connections in the switch. CAC functions may be distributed to blocks of input modules where each CAC has a smaller number of input ports. This is much harder to implement, but solves the connection control processing bottleneck problem for large switch sizes, by dividing this job to be performed by parallel CACs. Some of the distributed CAC functions can also be distributed among output modules which can handle encapsulation of high-layer control information into outgoing signalling cells.

#### 2.2.4 Switch Management

Handles physical layer OAM, ATM layer OAM, configuration management of switch components, security control for the switch database, usage measurements of the switch resources, traffic management, administration of a management information base, customer-network management, interface with operations systems and finally support of network management.

Switch Management must perform a few basic tasks. It must carry out:

- specific management responsibilities

- collect and administer management information

- communicate with users and network managers

- supervise and co-ordinate all management activities

Management functions include:

- fault management

- performance management

- configuration management

- accounting management

- security management

- traffic management

Carrying out these functions entails a lot of intra-switch communication between the switch management and other functional blocks.

A centralised switch management can be a performance bottleneck, if it is overloaded by processing demands. Hence, switch management functions can be distributed among input modules, but a lot of co-ordination would be required. Each distributed input module switch management unit can monitor the incoming user data cell streams to perform accounting and performance measurement. Output module switch management units can also monitor outgoing cell streams [CHEN 95].

Below is shown a literature study on the ATM Switching Technique. It is presented at Section 2.3 (Cell Switch Fabric function) and Section 2.4 (Switch Design Principle). This study is based on the article, "A survey of ATM Switching Techniques" presented by Sonia Fahmy. The detail of the article can be obtained at <u>http://www.cis.ohio-state.edu/~jain/cis788-95/atm\_switching/</u> [FAHM 95].

## 2.3 The Cell Switch Fabric

The cell switch fabric is primarily responsible for transferring cells between other functional blocks, this include routing of data cells and possibly signalling and management cells as well. Other possible functions include:

- cell buffering

- traffic concentration and multiplexing

- redundancy for fault tolerance

- multicasting or broadcasting

- cell scheduling based on delay priorities

- congestion monitoring

## 2.3.1 Concentration, Expansion and Multiplexing

Traffic needs to be concentrated at the inputs of the switching fabric to better utilise the incoming link connected to the switch. The concentrator aggregates the lower variable bit rate traffic to higher bit rate for switching matrix to perform the switching at standard interface speed. The concentration ratio is highly correlated with the traffic characteristics, so it needs to be dynamically configured. The concentrator can also aid in dynamic traffic distribution to multiple routing and buffering planes, and duplication of traffic for fault tolerance. At the outputs of the routing and buffering fabric, traffic can be expanded and redundant traffic can be combined.

# 2.3.2 Routing and buffering

The routing and buffering functions are the two major functions performed by the cell switch fabric. The input module attaches a routing tag to each cell, and the switch fabric simply routes the arriving cells from its inputs to the appropriate outputs. Arriving cells may be aligned in time by means of single-cell buffers. Because cells may be addressed to the same output simultaneously, buffers are needed. Several routing and buffering switch designs have aided in setting the important switch design principles. All current approaches employ a high degree of parallelism, distributed control, and the routing function is performed at the hardware level.

Before examining the impact of the various design alternatives, we need to consider the essential criteria for comparing among them. The basic factors are:

- 1. throughput (total output traffic rate/input traffic rate)

- 2. utilisation (average input traffic rate/maximum possible output traffic rate)

- 3. cell loss rate

- 4. cell delays

- 5. amount of buffering

- 6. complexity of implementation

Traditionally switching has been defined to encompass either space switching or time switching or combinations of both techniques. The classification adopted here is slightly different in the sense that it divides the design approaches under the following four broad categories:

- 1. shared memory

- 2. shared medium

- 3. fully interconnected

- 4. space division

For simplicity, the ensuing discussion will assume a switch with N input ports, N output ports, and all port speeds equal to V cells/s. Multicasting and broadcasting will be addressed with the other issues in the next section, so they will be temporarily ignored in this discussion.

Chapter 2

#### 2.3.2.1 Shared Memory Approach

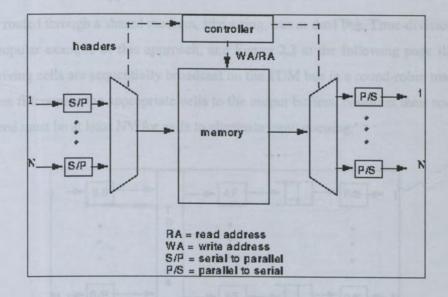

Figure 2.2 below illustrates the basic structure of a shared memory switch. Here incoming cells are converted from serial to parallel form, and written sequentially to a dual port Random Access Memory. A memory controller decides the order of cells read out of the memory, based on the cell headers with internal routing tags. Outgoing cells are de-multiplexed to the outputs and converted from parallel to serial form.

Figure 2.2 Basic structure of a shared-memory switch

This approach is an output queuing approach, where the output buffers, all physically belong to a common buffer pool. This approach is attractive because it achieves 100% throughput under heavy load. The buffer sharing minimises the amount of buffers needed to achieve a specified cell loss rate. This is because if a large burst of traffic is directed to one output port, the shared memory can absorb as much as possible of it.

This approach, however, suffers from a few drawbacks. The shared memory must operate N times faster than the port speed because cells must be read and written one at a time. As the access time of memory is physically limited, the approach is not very scalable. The product of number of port multiplier port speed NV is limited. In addition, the centralised memory controller must process cell headers and routing tags at the same rate as the memory. This is difficult for multiple priority classes, complicated cell scheduling, multicasting and broadcasting.

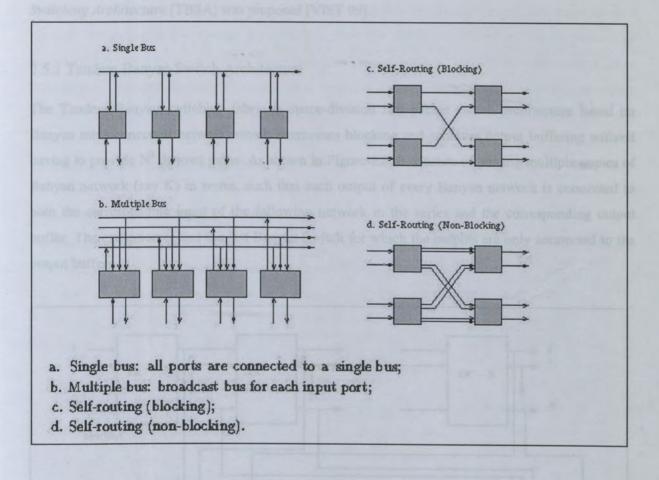

#### 2.3.2.2 Shared Medium Approach

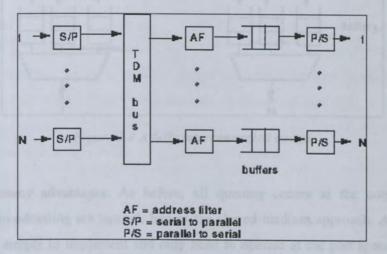

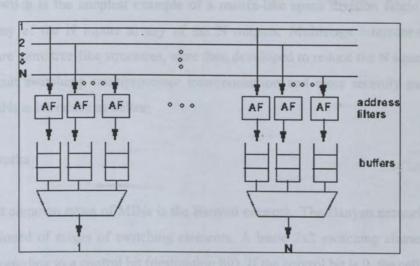

Cells may be routed through a shared medium, like a ring, bus or dual bus. Time-division multiplexed buses are a popular example of this approach, and Figure 2.3 at the following page illustrates their structure. Arriving cells are sequentially broadcast on the TDM bus in a round-robin manner. At each output, address filters pass the appropriate cells to the output buffers, based on their routing tag. The TDM bus speed must be at least NV for cells to eliminate input queuing.

Figure 2.3 A shared bus switch

The outputs are modular, which makes address filters and output buffers easy to implement. Also the broadcast-and-select nature of the approach makes multicasting and broadcasting straightforward. As a result, many such switches have been implemented, such as IBM's Packetized Automated Routing Integrated System (PARIS) and PLANET, NEC's ATM Output Buffer Modular Switch (ATOM), and Fore Systems' ForeRunner ASX-100.

However, because the address filters and output buffers must operate at the shared medium speed, which is N times faster than the port speed, this places a physical limitation on the scalability of the

approach. In addition, unlike the shared memory approach, output buffers are not shared, which requires more total amount of buffers for the same cell loss rate.

# 2.3.2.3 Fully Interconnected Approach

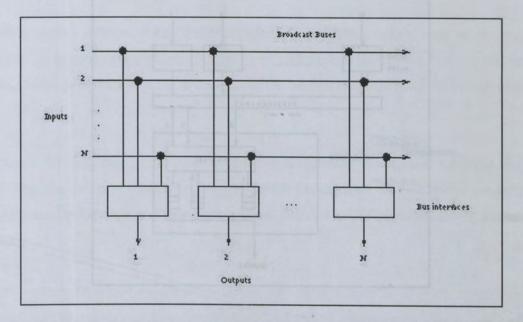

In this approach, independent paths exist between all N squared possible pairs of inputs and outputs. Hence arriving cells are broadcast on separate buses to all outputs and address filters pass the appropriate cells to the output queues. This architecture is illustrated in Figure 2.4 as show in the next page.

Figure 2.4 A fully interconnected switch

This design has many advantages. As before, all queuing occurs at the outputs. In addition, multicasting and broadcasting are natural, like in the shared medium approach. Address filters and output buffers are simple to implement and only need to operate at the port speed. Since all of the hardware operates at the same speed, the approach is scalable to any size and speed. Fujitsu's bus matrix switch and GTE Government System's SPANet are examples of switches in which this design was adopted.

Unfortunately, the quadratic growth of buffers limits the number of output ports for practical reasons. However, the port speed is not limited except by the physical limitation on the speed of the address filters and output buffers. The *Knockout* switch developed by AT&T was an early prototype where the amount of buffers was reduced at the cost of higher cell loss. Instead of N buffers at each output, it was proposed to use only a fixed number of buffers L for a total of NxL buffers. This technique was based on the observation that it is unlikely that more than L cells will arrive for any output at the same time. It was argued that selecting the L value of 8 was sufficient for achieving a cell loss rate of 1/1 Million under uniform random traffic conditions for large values of N [ROBE 93].

## 2.3.2.4 Space Division Approach

The *crossbar* switch is the simplest example of a matrix-like space division fabric that physically interconnects any of the N inputs to any of the N outputs. Multistage interconnection networks (MINs) which are more tree-like structures, were then developed to reduce the N squared cross points needed for circuit switching, multiprocessor interconnection and more recently packet switching. Two type of MINs is introduce as below:

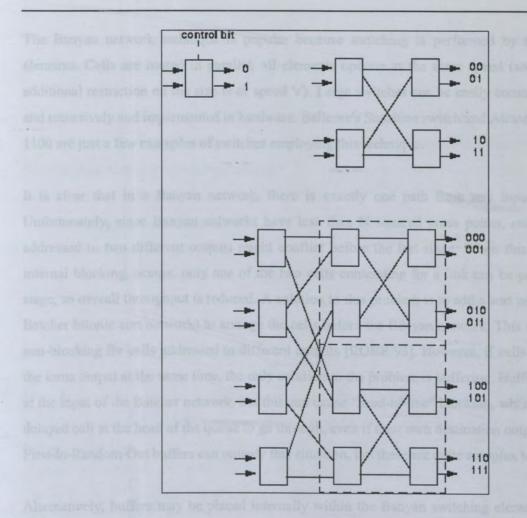

#### (I) Banyan networks

One of the most common types of MINs is the Banyan network. The Banyan network is constructed of interconnectioned of stages of switching elements. A basic 2x2 switching element can route an incoming cell according to a control bit (destination bit). If the control bit is 0, the cell is routed to the upper port address, otherwise it is routed to the lower port address.

To be an understand the conversition of Darran networks, consider forming a 4 by 4 Encyce network Figure 2.5 shows the nep-by step interconnection of awarshing elements to form and, and then 8x8 Banyin networks. The interconnection of two stoges of 2x3 switching elements can be done by using the first bit of the output address to denote which writching elements to must to, and shen using the hist bit to the output address to denote which writching elements to must to, and shen using the hist bit to the output address to denote which writching elements to must to, and shen using the hist bit to the output address to denote which writching element to must to, and shen to due the cell through the first stage, either to the upper or lower dash network, and then using the last 2 buts to route the cell through the dash activers to the upper or lower dash network, and then using the last

In general, to construct a NaM Danyan network, the n<sup>2</sup> single same the  $n^2$  bit of the companyation in rothe the cell. For N = 2 to the power of n, the Banyan will consist at  $n = \log n$  the base 2 of N ranges, each consisting of N/2 switching elements (ROBE 93).

#### Chapter 2

Figure 2.5 Switching element, 4x4 Banyan network and 8x8 Banyan network

To better understand the composition of Banyan networks, consider forming a 4 by 4 Banyan network. Figure 2.5 shows the step-by-step interconnection of switching elements to form 4x4, and then 8x8 Banyan networks. The interconnection of two stages of 2x2 switching elements can be done by using the first bit of the output address to denote which switching element to route to, and then using the last bit to specify the port. 8x8 Banyans can be recursively formed by using the first bit to route the cell through the first stage, either to the upper or lower 4x4 network, and then using the last 2 bits to route the cell through the 4x4 network to the appropriate output port.

In general, to construct a NxN Banyan network, the  $n^{th}$  stage uses the  $n^{th}$  bit of the output address to route the cell. For N = 2 to the power of n, the Banyan will consist of n = log to the base 2 of N stages, each consisting of N/2 switching elements [ROBE 93].

The Banyan network technique is popular because switching is performed by simple switching elements. Cells are routed in parallel, all elements operate at the same speed (so that there is no additional restriction on the size N or speed V). Large switches can be easily constructed modularly and recursively and implemented in hardware. Bellcore's Sunshine switch and Alcatel Data Networks' 1100 are just a few examples of switches employing this technique.

It is clear that in a Banyan network, there is exactly one path from any input to any output. Unfortunately, since Banyan networks have less than N squared cross points, routes of two cells addressed to two different outputs might conflict before the last stage. When this situation, called internal blocking, occurs, only one of the two cells contending for a link can be passed to the next stage, so overall throughput is reduced. A solution to this problem is to add a sort network (such as a Batcher bitonic sort network) to arrange the cells before the Banyan network. This will be internally non-blocking for cells addressed to different outputs [ROBE 93]. However, if cells are addressed to the same output at the same time, the only solution to the problem is buffering. Buffers can be placed at the input of the Batcher network, but this can cause "head-of-line" blocking, where cells wait for a delayed cell at the head of the queue to go through, even if their own destination output ports are free. First-In-Random-Out buffers can remedy this situation, but these are quite complex to implement.

Alternatively, buffers may be placed internally within the Banyan switching elements. Thus if two cells simultaneously attempt to go to the same output link, one of them is buffered within the switching element. This internal buffering can also be used to implement a backpressure control mechanism, where queues in one stage of the Banyan will hold up cells in the preceding stage by a feedback signal. The backpressure may eventually reach the first stage, and create queues at the Banyan network inputs. It is important to observe that internal buffering can cause head-of-line blocking at each switching element, and hence it does not achieve full throughput. Chen, Xing have designed a delta-based ATM switch with backpressure mechanism capable of achieving a high throughput while significantly reducing the overall required memory size [CHXI 94].

A third alternative is to use a recirculating buffer external to the switch fabric. This technique has been adopted in Bellcore's Sunshine and AT&T's Starlite wideband digital switch [ROBE 93]. Here output conflicts are detected after the Batcher sorter, and a trap network selects a cell to go through, and recirculates the others back to the inputs of the Batcher network. Unfortunately, this approach

requires complicated priority control to maintain the sequential order of cells and increases the size of the Batcher network to accommodate the recirculating cells.

As discussed before, output buffering is the most preferable approach. However, Banyan networks cannot directly implement it, since at most one cell per cell time is delivered to every output. Possible ways to work around this problem include:

- increase the speed of internal links

- route groups of links together

- use multiple Banyan planes in parallel

- use multiple Banyan planes in tandem or adding extra switching stages

# 2.4 Switch Design Principles

From the preceding section, it can be seen that each design alternative has its own merits, drawbacks, and considerations. The general design principles and issues exposed in the last section are analysed in more detail here.

# 2.4.1 Internal Blocking

A fabric is said to be internally blocking if a set of N cells addressed to N different outputs can cause conflicts within the fabric. Internal blocking can reduce the maximum possible throughput. Banyan networks are blocking, while TDM buses where the bus operates at least N times faster than the port speed are internally nonblocking. By the same concept, shared memory switches which can read and write at the rate of NV cells per second are internally non-blocking, since if N cells arrive for N different outputs, no conflicts will occur. Hence, to prevent internal blocking, shared resources must operate at some factor greater than the port speed. Applying this to Banyan networks, the internal links need to run square root of N times faster than the highest speed incoming link [ONVU 95]. This factor limits the scalability and throughput of the switch.

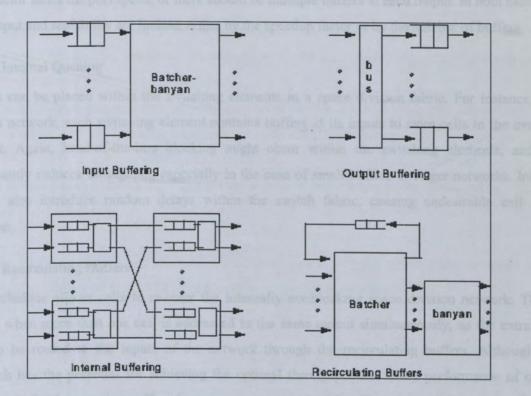

## 2.4.2 Buffering Approaches

Buffering is necessary in all design approaches. For instance, in a Banyan network, if two cells addressed to the same output successfully reach the last switching stage at the same time, output contention occurs and must be resolved by employing buffering. The location and size of buffers are important issues that must be decided.

There are four basic approaches to the placement of buffers. These basic approaches are illustrated in Figure 2.6. A lot of comparative studies of these approaches together with numerous queuing analyse and result has been examined although each approach has its own merits and drawbacks, output queuing is the preferred technique so far.

Figure 2.6 The various buffering approaches

### 2.4.2.1 Input Queuing

Buffers at the input of an internally nonblocking space division fabric (such as Batcher Banyan network) illustrate this type of buffering. This approach suffers from head-of-the-line blocking. When two cells arrive at the same time and are destined to the same output, one of them must wait in the input buffers, preventing the cells behind it from being admitted. Thus capacity is wasted.

Several methods have been proposed to tackle the head-of-the-line blocking problem, but they all exhibit complex design. Increasing the internal speed of the space division fabric by a factor of four, or changing the First-In-First-Out (FIFO) discipline are two examples of such methods.

### 2.4.2.2 Output Queuing

This type of buffering can be evident by examining the buffers at the output ports of a shared bus fabric. This approach is optimal in terms of throughput and delays, but it needs some means of delivering multiple cells per cell time to any output. Hence, either the output buffers must operate at some factor times the port speed, or there should be multiple buffers at each output. In both cases, the throughput and scalability are limited, either by the speedup factor or by the number of buffers.

### 2.4.2.3 Internal Queuing

Buffers can be placed within the switching elements in a space division fabric. For instance, in a Banyan network, each switching element contains buffers at its inputs to store cells in the event of conflict. Again, head-of-the-line blocking might occur within the switching elements, and this significantly reduces throughput, especially in the case of small buffers or larger networks. Internal buffers also introduce random delays within the switch fabric, causing undesirable cell delay variation.

### 2.4.2.4 Recirculating Buffers