## Faculty of Computer Science & Information Technology

0

Perpustakaan SKTM

**VHDL Description for IP Engine**

**WXES3182**

Name: Zellal Bathich

Matrix: WEK010401

Supervisor : Mr. Noorzaily Mohd. Noor

Moderator : Mr. Yamani Mohd. Idna Idris

## **Table Of Contents**

Abstract

Acknowledgement

Chapter 1: Introduction

| 1.1 Introduction         |

|--------------------------|

| 1.2 Problems Definitions |

| 1.3 Scope                |

| 1.4 Objectives           |

| 1.5 Constraints          |

| 1.6 Scheduling           |

## Chapter 2: Literature Review

| 2.1 Introduction                                             | 8   |

|--------------------------------------------------------------|-----|

| 2.2 Network Protocol Layer                                   | 8   |

| 2.3 Layering Models                                          | 9   |

| 2.4 The TCP/IP Stack                                         | .10 |

| 2.5 TCP/IP Protocols                                         | .13 |

| 2.6 Internet Protocol                                        | .14 |

| 2.7 IP Address                                               | .16 |

| 2.8 IP Address Classes                                       | 17  |

| 2.9 Netmasks                                                 | .18 |

| 2.10 Subnet Address                                          | 18  |

| 2.11 Direct Broadcast Address                                | 19  |

| 2.12 limited Broadcast Address                               | 19  |

| 2.13 IP Routing                                              | 19  |

| 2.14 ARP                                                     | 20  |

| 2.15 IP Packet Structure                                     | 21  |

| 2.16 IP Packet Processing                                    | .24 |

| 2.17 IP Fragmentation Processing at a Router                 | .26 |

| 2.18 IP Fragmentation Processing at the receiving End System | .27 |

| 2.19 Reception of a Frame form The Ethernet                  | 27  |

|                                                              | 30  |

|                                                              | 30  |

|                                                              | .31 |

|                                                              | 33  |

| 2.20.4 IP Engine                                             | .36 |

| Chapter 3: Methodology |   |  |

|------------------------|---|--|

|                        | - |  |

| 3.1 Methodology        |   |  |

Chapter 4: System Analysis

| 4.1 VHDL                        | 40 |

|---------------------------------|----|

| 4.2 What Is VHDL                |    |

| 4.3 VHDL Advantages             |    |

| 4.4 VHDL And Verilog Comparison |    |

## Chapter 5: System Design

| 5.1 System Design           |  |

|-----------------------------|--|

| 5.2 IP Engine Block Diagram |  |

| 5.3 Internal Block Diagram  |  |

| 5.4 Process Flow            |  |

## Chapter 6: System Implementation

| 6.1 Introduction    |  |

|---------------------|--|

| 6.2 Design Entry    |  |

| 6.3 Modeling Enity  |  |

| 6.4 Model Analysis. |  |

| 6.5 Synthesis       |  |

Chapter 7: System Testing And Evaluation

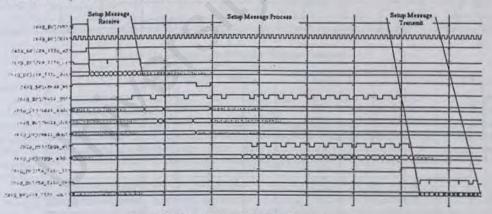

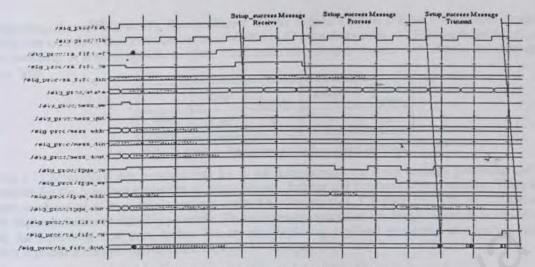

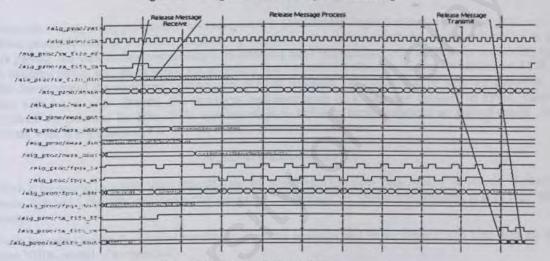

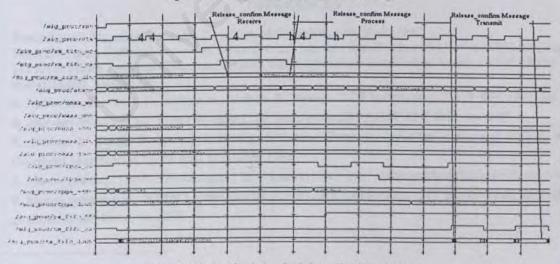

| 7.1 Simulation and Testing | 70 |

|----------------------------|----|

| 7.2 Cycle Simulation       | 72 |

| 7.3 System Testing         | 73 |

## **WXES3182**

| Chapter 8: Discussion               | 75 |

|-------------------------------------|----|

| Chapter 9: Conclusion               |    |

| References                          |    |

| Appendices A : VHDL Source Code     |    |

| Appendices B : PeakFPGA User Manual |    |

Appendices C : Main References

## Abstract

Developing hardware support for network layer protocol processing is a very complex and demanding task. However, for optimal performance hardware acceleration can be required. To cope with the situation, this project present a high-level design approach, which targets the development of configurable and reusable components. Therefore it obtains the integration of advanced tools for the development of the IP Engine into the design environment.

This process is illustrated based on a TCP/IP header analysis and validation component for which initial performance results are presented. The development of this Engine is embedded in an approach to develop flexible and configurable protocol engines that can be optimized for specific application.

By implementing the IP Engine in hardware it will help reducing communication bottlenecks replacing expensive software solutions, which are based on 32 bit processor cores. With its small footprint design it will improve low power-consumption, highly cost-effective solution to Perform all protocol functions of TCP/IP and UDP/IP connections for sustained bit rates of up to 100 Mbps independent of packet payload sizes and other connection parameters.

## Acknowledgment

Utter most gratitude goes to the almighty Allah for all the confidence and patience in the completion of part 1 and part 2 of the thesis. I wish to record my indebtedness and appreciation to everyone who has been so helpful and supportive in this project work and brought it to success.

I would like to express my deep gratitude to my supervisor Mr Noorzaily Mohd. Noor for the tremendous help he has given me during this project, technical advice and thoughtful comment. And also to my examiner Mr. Yamani Mohd. Idna Idris for his guidance and sharing his experience and knowledge. The valuable advice and motivation will be cherished thus to develop a personal values of mine in the future.

Also taking this opportunity expressing my thanks to all fellow members and especially the family of Computer Science and Networking for their constructive criticism and support to face the difficulties and challenging time.

Finally, last but not least, I am much obliged to my dear parents who have been given invaluable support and inspiration to me throughout my university life. My gratefulness also goes to all the unnamed others who directly or indirectly helped me to complete this interesting and challenging project. With this sheet of paper, I can only say thank you with all my heart.

## In Distance I willing

Most systems today, which require Endedded Internationactivity, picks use of a \$2.66

success and and pression of TCPTP on Loss made in partners,

This methods have been seen after a second proceeding performance provides and have

system or any first had a configuration had

Towards improving particularies, an analytical a limitance implymentation of speciality

# **Chapter 1**

thereas all preserved functions of TUPAP and UITPAP presenteers for namediation has presented by

## Introduction

and a second second

· stard time multility

\* complete TEP-IP solution

#### Introduction

**WXES3182**

## **1.1 Introduction**

Most systems today, which require embedded Internet connectivity, make use of a 32-bit processor core and implement the TCP/IP protocol stack in software.

This realization however often results in strong processor performance requirements and keeps system costs for Internet application high.

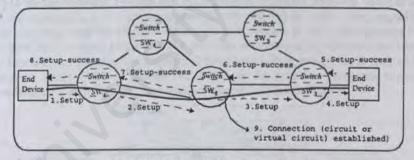

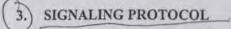

Towards improving performance, we undertook a hardware implementation of a signaling protocol to eliminate the burden on the host CPU, dramatically reduce bottlenecks in the server and help in faster and accuarate data transmission in a tremendous netwok environment.

The system is designed to enhance performance and power consumtions of embedded systems. It performs all protocol functions of TCP/IP and UDP/IP connections for sustained bit rates of up to 100 Mbps independent of packet payload sizes and other connection parameters. It provides IP connectivity even without any external processor interaction, which makes it also an ideal internet access solution for existing applications.

The system will support:

- 100 mb/s throughput for all packet sizes

- support of up to 64K connections

- stand-alone capability

- complete TCP/IP solution

## **1.2 Problem Definition**

Through the analysis process of the project I discovered few problems that should be overcomed which are:

- Limited references

- Limited given time to finish the first part of the project, which is to analysis and design the system.

- The difficulties of implementing theoretical definitions and approaches into real system.

- The execution of the overall system is hard to implement because of other different protocols, which is included.

## 1.3 Scope

The project scope determines part of the project process, which will overcome the burden of the overall system development.

By implementing the Internet Protocol (IP) engine in hardware which off-loads performance intensive Internet protocols from processor sub-systems and allows for separate system optimization.

#### Introduction

Several options to overcome the large cost of the hardware implementation:

**Simulation**: Simulation is one of the important steps of complex hardware design. Open Hardware designers may simulate their designs only without implementing them. In this way they did the design using free simulators without the cost of implementation.

The use of Programmable Logic: These days the programmable logic devices become very popular and have lot of hardware resources that can compete old ASICs. These devices showed some good examples of real complex designs built using them. They can be programmed in field using a PC or small programmer. This approach becomes too close to the software designs, since any one can design his/her own hardware and program it on one of these devices.

The entire IP Engine can be constructed out of interrelated sub modules, but this is very complicated when it is implemented directly. It's difficult to follow which input lines correspond to certain variables and what their values would be. It's more efficient to use some other method to construct the IP Engine that models it in a method that is easier to understand. It is for this reason that programmable logic language like VHDL were created. VHDL is a very popular language for describing modeling and synthesis of digital circuits and systems. Its powerful but narrow field of usage makes it difficult to find software packages that easily implement testing of the VHDL code.

## 1.4 Objectives

While software implementations require very fast processors to follow Ethernet transmission speeds, it provides a sustained bit rate of 100 Mbps up to the TCP/UDP layer of the Internet protocol stack. Instead of assigning considerable resources to interrupt driven processor context switches and memory access operations, the protocol processor implements a hardware architecture, which directly operates on the communication data stream. With a total of 100k logic gates and an operating frequency of only 25MHz, this hardware engine consumes less power and provides a competitive, small footprint solution.

The main objectives of implementing the Internet Protocol Engine in hardware are:

- Improving price, performance and power consumption of embedded systems.

- Reducing network latency

- Reducing system overhead

- Accelerates network performance to full wire speed

- 100 Mb/s throughput for all packet sizes

- Support of up to 64k connections

- Complete TCP/IP solution

## **1.5 Constraints**

The expected constraints will be faced during system development are:

- Take a lot of time (including VHDL or Verilog design and simulation).

- There are several key limitations to the design of the IP stack, most of which are due to the limited amount of hardware, RAM and buffer space available on an FPGA (assuming the IP stack shouldn't take up over half the FPGA in size).

- The lack of buffer space also creates problems if multiple datagrams are being received and reassembled at once, or if the transport layer protocols are busy then datagrams will have to be dropped as no IP buffers will be free unless more IP buffers or transport layer buffers are allocated. Increasing the number buffers results in a large increase of memory usage and logic needed for controlling them.

- Require a robust FPGA.

## 1.6 Scheduling

The bar chart below shows the activities of each process phase that will be carried out through the development of the system. It will take an approximate time of 9 months to finish the whole thesis project. Starting on the first phase, which is system analysis from June until July. At this phase, information is collected on systems available and study is made on the methodology that will be used in this project.

The second phase starts from August until September, which is working on the system design. At the beginning of October the second part of the thesis will be started by the implementation of the system, which is the system coding. System testing will be carried out at the middle of December until the end of January. The system will be tested to check if it's free from errors.

The last phase of system development is the system evaluation. It starts at the end of January until the end of February. The required system output will be checked in this phase.

| THE R | Trail             |            |            |         |                                                           | and and a | U.S.A. |  | and the second second | and the second second | and and a |  |  |  |  |  | No. |  | and the second | il and | 10 const | a.e. | ar 200 alg |

|-------|-------------------|------------|------------|---------|-----------------------------------------------------------|-----------|--------|--|-----------------------|-----------------------|-----------|--|--|--|--|--|-----|--|----------------|--------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B     | Teak Name         | Sart       | Finiah     | Dutelon | 1 400 448 78 79 500 170 100 100 100 100 100 100 100 100 1 |           |        |  |                       |                       |           |  |  |  |  |  |     |  |                |        |          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1     | Syntam Analyzia   | 6/19/2003  | 1725/2003  | 5.4m    |                                                           |           |        |  |                       |                       |           |  |  |  |  |  |     |  |                |        |          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1     | System Design     | 1/28/2001  | \$/19/2093 | h       |                                                           |           |        |  |                       |                       |           |  |  |  |  |  |     |  |                |        |          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3     | Implementation    | 8/22/2003  | 12/18/2003 | 12.44   |                                                           |           |        |  |                       |                       |           |  |  |  |  |  |     |  |                |        |          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| +     | System Testing    | 12/17/2003 | 1/27/2004  | 61      |                                                           |           |        |  |                       |                       |           |  |  |  |  |  |     |  |                |        |          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5     | System Evaluation | 1/28/2994  | 1/9/2004   | 5.3n    |                                                           |           |        |  |                       |                       |           |  |  |  |  |  |     |  |                |        |          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Figure 1.1 Activities Schedule Bar Chart

## 11 Introduction

A permana a an princip and convenienc and in impose a manified, description in the second state of the sec

exclusives and provide place between two computers taking the start provided.

Transmitting data and an exemption seconds in an and prove task. Naming of Out

# **Chapter 2**

## **Literature Review**

e par manene de la la la company den entre entre partie de la radio de partie de la segue de la company de la compan

where an a service of the service in a service of the service of t

the places. A hiperographic acts the division and provides the constraint hims

## 2.1 Introduction

A **protocol** is set of rules and conventions used to impose a standardized, structured language for the communication between multiple parties. For example, a protocol might define the order in which information is exchanged between two parties. In fact, a data exchange can *only* take place between two computers using the same protocol.

Transmitting data across computer networks is an arduous task. Network functionality has been decomposed into modules called **layers** to simplify and separate the tasks associated with data transmission. Each layer is a unit of code that performs a small, well-defined set of tasks. A **protocol suite** (or **protocol stack**) is a set of many such layers, and is usually a part of the operating system kernel on machines connected to the Internet.

A protocol stack is organized such that the highest level of abstraction resides at the top layer. For example, the highest layer may deal with streaming audio or video frames, whereas the lowest layer deals with raw voltages or radio signals. Every layer in a stack builds upon the services provided by the layer immediately below it.

## 2.2 Network Protocol Layers

Computers on a network communicate in agreed upon ways called protocols. The complexity of networking protocol software calls for the problem to be divided into smaller pieces. A layering model aids this division and provides the conceptual basis for

8

understanding how software protocols together with hardware devices provide a powerful communication system.

## 2.3 Layering Models

In the early days of networking, before the rise of the ubiquitous Internet, the International Organization for Standardization (ISO) developed a layering model whose terminology persists today.

|         | Name of Layer | Purpose of Layer                                                                      |

|---------|---------------|---------------------------------------------------------------------------------------|

| Layer 7 | Application   | Specifies how a particular application uses a network.                                |

| Layer 6 | Presentation  | Specifies how to represent data.                                                      |

| Layer 5 | Session       | Specifies how to establish communication with a remote system.                        |

| Layer 4 | Transport     | Specifies how to reliably handle data transfer.                                       |

| Layer 3 | Network       | Specifies addressing assignments and how packets are forwarded.                       |

| Layer 2 | Data Link     | Specifies the organization of data into frames and how to send frames over a network. |

| Layer 1 | Physical      | Specifies the basic network hardware.                                                 |

Table 2.1. ISO 7-Layer Reference Model

The 7-layer model has been revised to the 5-layer TCP/IP reference model to meet the current needs of protocol designers.

## 2.4 The TCP/IP Stack

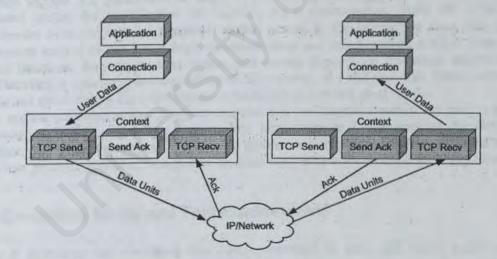

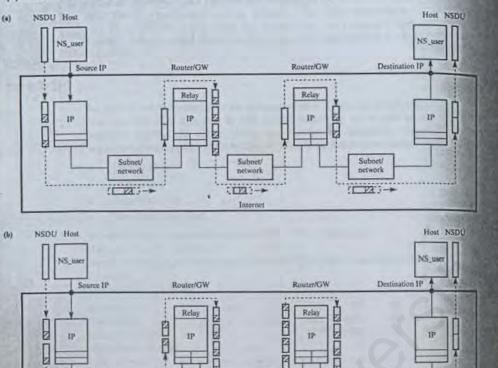

The picture below is an example of a simple data transfer between 2 computers and shows how the data is sent and received through the TCP/IP stack.

|            |            |           |        |      |        | Lu               | omputer |  |

|------------|------------|-----------|--------|------|--------|------------------|---------|--|

|            |            |           |        |      |        | data convert     | ed for  |  |

|            |            |           |        |      | Uppe   | Upper layer data |         |  |

|            |            |           |        | TCP  | Header | Upper lay        | er data |  |

|            |            | IP        | Header | TCP  | Header | Upper lay        | er data |  |

| MAC Header | LLC Header | IP Header | TCP He | ader | Upper  | ayer data        | FCS     |  |

Figure 2.1. Shows Data Sent and Received through the Stack

The computer in the above diagram needs to send some data to another computer. The Application layer is where the user interface exists, here the user interacts with the application he or she is using, and then this data is passed to the Presentation layer and then to the Session layer. These three layers add some extra information to the original data that came from the user and then passes it to the Transport layer. Here the data is

broken into smaller pieces (one piece at a time transmitted) and the TCP header is added. At this point, the data at the Transport layer is called a *segment*.

Each segment is sequenced so the data stream can be put back together on the receiving side exactly as transmitted. Each segment is then handed to the Network layer for network addressing (logical addressing) and routing through the Internet network. At the Network layer, we call the data (which includes at this point the transport header and the upper layer

information) a *packet*. The Network layer adds its IP header and then sends it off to the Data link layer. Here we call the data (which includes the Network layer header, Transport layer header and upper layer information) a *frame*.

The Data link layer is responsible for taking packets from the Network layer and placing them on the network medium (cable). The Data link layer encapsulates each packet in a frame that contains the hardware address (MAC) of the source and destination computer (host) and the LLC information, which identifies to which protocol in the previous layer (Network layer) the packet should be passed when it arrives to its destination. Also, at the end, we will notice the FCS field that is the Frame Check Sequence. This is used for error checking and is also added at the end by the Data link layer.

If the destination computer is on a remote network, then the frame is sent to the router or gateway to be routed to the destination. To put this frame on the network, it must be put into a digital signal. Since a frame is really a logical group of 1's and 0's, the Physical

layer is responsible for encapsulating these digits into digital signals, which is red by devices on the same local network.

At the receiving process, computer will synchronize the digital signal by reading the few extra 1's and 0's as mentioned above. Once the synchronization is complete and it receives the whole frame it will passes it to the layer above it, which is the Data link layer.

The Data link layer will do a Cyclic Redundancy Check (CRC) on the frame. This is a computation, which the computer does, and if the result it gets matches the value in the FCS field, then it assumes that the frame has been received without any errors. Once that's out of the way, the Data link layer will strip off any information or header, which was put on by, the remote system's Data link layer and pass the rest (now we are moving from the Data link layer to the Network layer, so we call the data a *packet*) to the above layer which is the Network layer.

At the Network layer the IP address is checked and if it matches (with the machine's own IP address) then the Network layer header is stripped off from the packet and the rest is passed to the above layer, which is the Transport layer. Here the rest of the data is now called a *segment*.

The segment is processed at the Transport layer, which rebuilds the data stream (at this level on the sender's computer it was actually split into pieces so they can be transferred) and acknowledges to the transmitting computer that it received each piece. It is obvious

that since we are sending an ACK back to the sender from this layer that we are using TCP and not UDP.

We will find that when analyzing the way data travels from one computer to another most people never analyze in detail any layers above the Transport layer. This is because the whole process of getting data from one computer to another involves usually layers 1 to 4 (Physical to Transport) or layer 6 (Session) at the most, depending on the type of data.

## 2.5 TCP/IP Protocols

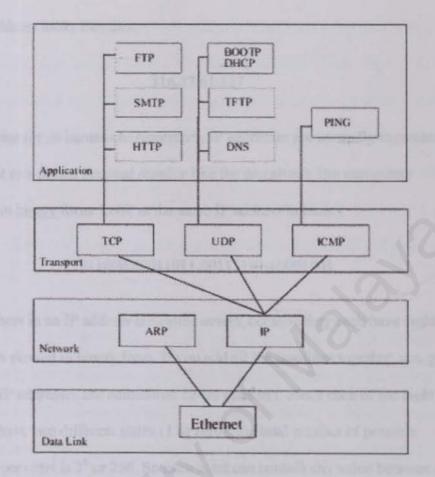

This chapter discusses the protocols available in the TCP/IP protocol suite. The following figure shows how they correspond to the 5-layer TCP/IP Reference Model. This is not a perfect one-to-one correspondence for instance, Internet Protocol (IP) uses the Address Resolution Protocol (ARP), but is shown here at the same layer in the stack.

Figure 2.2. TCP/IP Protocol Flow

## 2.6 Internet Protocol (IP)

Every machine on the Internet has a unique identifying number, called an **IP Address**. The IP stands for **Internet Protocol**, which is the language that computers use to communicate over the Internet. A protocol is the pre-defined way that someone who wants to use a service talks with that service. The "someone" could be a person, but more often it is a computer program like a Web browser.

A typical IP address looks like this:

#### 216.27.61.137

To make it easier for us humans to remember, IP addresses are normally expressed in decimal format as a *dotted decimal number* like the one above. But computers communicate in <u>binary</u> form. Look at the same IP address in binary:

## 11011000.00011011.00111101.10001001

The four numbers in an IP address are called **octets**, because they each have eight positions when viewed in binary form. If you add all the positions together, you get 32, which is why IP addresses are considered 32-bit numbers. Since each of the eight positions can have two different states (1 or zero), the total number of possible combinations per octet is 2<sup>8</sup> or 256. So each octet can contain any value between zero and 255. Combine the four octets and you get 2<sup>32</sup> or a possible 4,294,967,296 unique values!

Out of the almost 4.3 billion possible combinations, certain values are restricted from use as typical IP addresses. For example, the IP address 0.0.0.0 is reserved for the default network and the address 255.255.255.255 is used for <u>broadcasts</u>.

The octets serve a purpose other than simply separating the numbers. They are used to create **classes** of IP addresses that can be assigned to a particular business, government or other entity based on size and need. The octets are split into two sections: **Net** and **Host**. The Net section always contains the first octet. It is used to identify the network that a

computer belongs to. Host (sometimes referred to as **Node**) identifies the actual computer on the network. The Host section always contains the last octet. There are five IP classes plus certain special addresses. When the Internet was in its infancy, it consisted of a small number of computers hooked together with modems and telephone lines. You could only make connections by providing the IP address of the computer you wanted to establish a link with. For example, a typical IP address might be 216.27.22.162. This was fine when there were only a few hosts out there, but it became unwieldy as more and more systems came online.

The first solution to the problem was a simple text file maintained by the Network Information Center that mapped names to IP addresses. Soon this text file became so large it was too cumbersome to manage. In 1983, the University of Wisconsin created the **Domain Name System** (DNS), which maps text names to IP addresses automatically. This way you only need to remember www.um.edu.my, for example, instead of UM's IP address.

## 2.7 IP Address

IP defines an addressing scheme that is independent of the underlying physical address (e.g. 48-bit MAC address). IP specifies a unique 32-bit number for each host on a network. This number is known as the Internet Protocol Address, the IP Address or the Internet Address. These terms are interchangeable. Each packet sent across the Internet contains the IP address of the source of the packet and the IP address of its destination. For routing efficiency, the IP address is considered in two parts: the prefix, which identifies the physical network, and the suffix, which identifies a computer on the network. A unique prefix is needed for each network in an Internet. For the global Internet, network numbers are obtained from Internet Service Providers (ISPs). ISPs coordinate with a central organization called the Internet Assigned Number Authority (IANA).

## 2.8 IP Address Classes

The first four bits of an IP address determine the class of the network. The class specifies how many of the remaining bits belong to the prefix (aka Network ID) and to the suffix (aka Host ID). The first three classes, A, B and C, are the primary network classes.

| Class | First 4 Bits | Number Of<br>Prefix Bits | Max Of<br>Networks | Number Of<br>Suffix Bits | Max Of Hosts<br>Per Network |

|-------|--------------|--------------------------|--------------------|--------------------------|-----------------------------|

| A     | 0xxx         | 7                        | 128                | 24                       | 16,777,216                  |

| В     | 10xx         | 14                       | 16,384             | 16                       | 65,536                      |

| С     | 110x         | 21                       | 2,097,152          | 8                        | 256                         |

| D     | 1110         | Multicast                |                    |                          | a de la companya            |

| E     | 1111         | Reserved for fu          |                    |                          | the state of                |

Table 2.2. IP addressing classes

#### **WXES3182**

When interacting with mere humans, software uses dotted decimal notation; each 8 bits is treated as an unsigned binary integer separated by periods. IP reserves host address 0 to denote a network. 140.211.0.0 denotes the network that was assigned the class B prefix 140.211.

#### 2.9 Netmasks

Netmasks are used to identify which part of the address is the Network ID and which part is the Host ID. This is done by a logical bitwise-AND of the IP address and the netmask. For class A networks the netmask is always 255.0.0.0; for class B networks it is 255.255.0.0 and for class C networks the netmask is 255.255.255.0.

## 2.10 Subnet Address

All hosts are required to support subnet addressing. While the IP address classes are the convention, IP addresses are typically subnetted to smaller address sets that do not match the class system. The suffix bits are divided into a subnet ID and a host ID. This makes sense for class A and B networks, since no one attaches as many hosts to these networks as is allowed. Whether to subnet and how many bits to use for the subnet ID is determined by the local network administrator of each network.

If subnetting is used, then the netmask will have to reflect this fact. On a class B network with subnetting, the netmask would not be 255.255.0.0. The bits of the Host ID that were used for the subnet would need to be set in the netmask.

## 2.11 Directed Broadcast Address

IP defines a directed broadcast address for each physical network as all ones in the host ID part of the address. The network ID and the subnet ID must be valid network and subnet values. When a packet is sent to a network's broadcast address, a single copy travels to the network, and then the packet is sent to every host on that network or subnetwork.

## 2.12 Limited Broadcast Address

If the IP address is all ones (255.255.255.255), this is a limited broadcast address; the packet is addressed to all hosts on the current (sub)network. A router will not forward this type of broadcast to other (sub)networks.

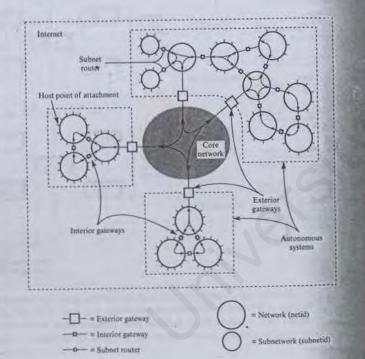

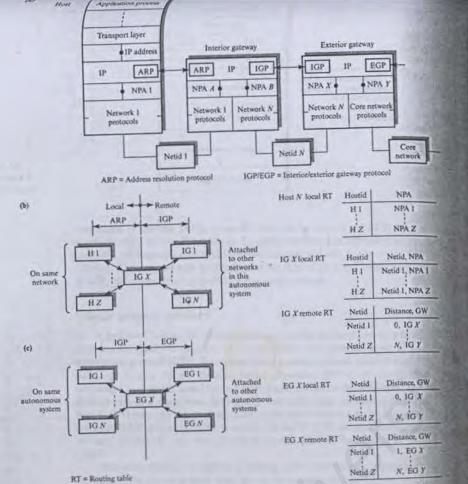

## 2.13 IP Routing

Each IP datagram travels from its source to its destination by means of routers. All hosts and routers on an Internet contain IP protocol software and use a routing table to determine where to send a packet next. The destination IP address in the IP header contains the ultimate destination of the IP datagram, but it might go through several other IP addresses (routers) before reaching that destination.

Routing table entries are created when TCP/IP initializes. The entries can be updated manually by a network administrator or automatically by employing a routing protocol such as Routing Information Protocol (RIP). Routing table entries provide needed

information to each local host regarding how to communicate with remote networks and hosts. When IP receives a packet from a higher-level protocol, like TCP or UDP, the routing table is searched for the route that is the closest match to the destination IP address. The most specific to the least specific route is in the following order:

- A route that matches the destination IP address (host route).

- A route that matches the network ID of the destination IP address (network route).

- The default route. If a matching route is not found, IP discards the datagram

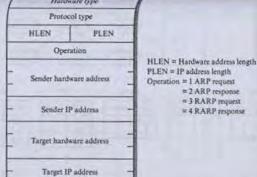

## 2.14 ARP

The Address Resolution Protocol is used to translate virtual addresses to physical ones. The network hardware does not understand the software-maintained IP addresses. IP uses ARP to translate the 32-bit IP address to a physical address that matches the addressing scheme of the underlying hardware (for Ethernet, the 48-bit MAC address).

TCP/IP can use any of the three. ARP employs the third strategy, message exchange. ARP defines a request and a response. A request message is placed in a hardware frame (e.g., an Ethernet frame), and broadcast to all computers on the network. Only the computer whose IP address matches the request sends a response.

## 2.15 IP Packet Structure

Before introducing the system proposed and compare it with the existing system it is more helpful to study the IP packet structure and learn how different fields effect the processing of datagrams.

All IP packets or datagrams consist of a header part and a text part. The IP Header consists of a 20-byte fixed part plus a variable part. Its size is optimized to maximize the packet-processing rate without utilizing excessive resources. The header begins with a 4bit version field that keeps track of the version of the IP protocol to which the datagram belongs. This field helps smooth the transition from one version of IP to another, which can take months or even years. All IP packets are structured the same way - an IP header followed by a variable-length data field.

| 00  | 01 02          | 03 04 | 4 05 06   | 07 | 08 0     | 9 10     | 11 | 12  | 13    | 14   | 15  | 16              | 7    | 18  | 19              | 20 2 | 1 22 | 23 | 24   | 25  | 26   | 27  | 28 | 29 | 30 | 31 |

|-----|----------------|-------|-----------|----|----------|----------|----|-----|-------|------|-----|-----------------|------|-----|-----------------|------|------|----|------|-----|------|-----|----|----|----|----|

|     | rsion          |       | IHL       |    |          |          |    |     |       |      |     | Total length    |      |     |                 |      |      |    |      |     |      |     |    |    |    |    |

|     | Identification |       |           |    |          |          |    |     |       |      |     |                 | ags  | . [ | Fragment offset |      |      |    |      |     |      |     |    | 1  |    |    |

| TTL |                |       |           |    |          | Protocol |    |     |       |      |     | Header checksum |      |     |                 |      |      |    |      |     |      |     |    |    |    |    |

|     |                |       |           | K  |          |          |    |     | Sou   | irce | IP  | add             | ress | 5   |                 |      |      |    |      | -   |      |     |    | -  |    |    |

|     |                | =10   |           |    | 10       |          | 4  | D   | estin | nati | on  | IP a            | idro | ess |                 | -    | 4    | 1  | 50 8 | be  |      | 12. |    |    |    |    |

|     |                |       | The state | 12 | - Harris |          |    | - ( | pp    | URS. | 376 | i pa            | ktij | 415 | 1000            | 3 32 | 100  |    |      | ne. | Tel. | 30  | 1  | R  |    |    |

Figure 2.3 Packet Structure

Version: The Version field indicates the format of the Internet header.

**IHL**: Internet Header Length is the length of the Internet header in 32 bit words, and thus points to the beginning of the data. Note that the minimum value for a correct header is 5.

**Type of Service**: The Type of Service provides an indication of the abstract parameters of the quality of service desired. The type of service is used to specify the treatment of the datagram during its transmission through the internet system.

**Total Length**: Total Length is the length of the datagram, measured in octets, including Internet header and data. This field allows the length of a datagram to be up to 65,535 octets. Such long datagrams are impractical for most hosts and networks. **Identification**: An identifying value assigned by the sender to aid in assembling the fragments of a datagram.

Flags: Various Control Flags.

**Fragment Offset**: This field indicates where in the datagram this fragment belongs. The fragment offset is measured in units of 8 octets (64 bits). The first fragment has offset zero.

Time to Live: This field indicates the maximum time the datagram is allowed to remain in the Internet system. If this field contains the value zero, then the datagram must be destroyed.

**Protocol**: This field indicates the next level protocol used in the data portion of the Internet datagram.

**Header Checksum**: A checksum on the header only. Since some header fields change (e.g., time to live), this is recomputed and verified at each point that the Internet header is processed. The checksum field is the 16 bit one's complement of the one's complement sum of all 16-bit words in the header. For purposes of computing the checksum, the value of the checksum field is zero.

**Options**: The options may appear or not in datagram's. In some environments the security option may be required in all datagram's. The option field is variable in length. There may be zero or more options.

**WXES3182**

## 2.16 IP Packet Processing

Transmission of a frame over Ethernet

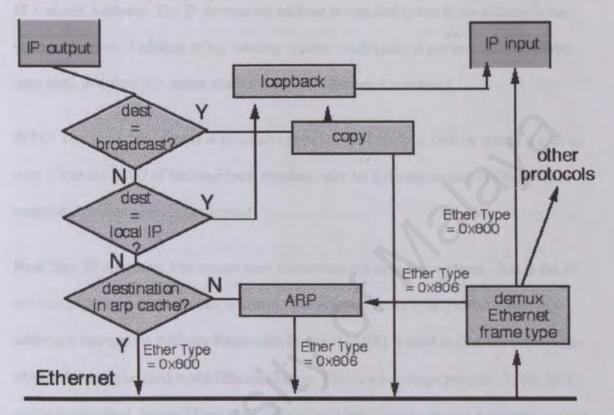

Figure 2.4 Transmission of a frame over Ethernet

The IP packet is placed in an Ethernet frames as follows:

**IP Broadcast/Multicast Address:** The IP destination address is checked to see if the system should also receive a copy of the packet. This happens if this is an IP network broadcast address (or a multicast address is used that matches one of the registered IP multicast filters set by the IP receiver). If a copy is required, it is sent to the loop back

interface. This directly delivers the packet to the IP input routine. The original packet continues to be processed.

**IP Unicast Address:** The IP destination address is checked to see if the address is the unicast (source) IP address of the sending system. Such packets are sent directly to the loop back interface (i.e. never reach the physical Ethernet interface).

**MTU:** The size of the packet is checked against the MTU of the link on which it is to be sent. (Note the MTU of the loop back interface may be different to that of Ethernet). If required, fragmentation is performed.

Next Hop IP Address: The sender then determines the next hop address - that is the IP address of the next Intermediate System/End System to receive the packet. Once this address is known, the Address Resolution Protocol (ARP) is used to find the appropriate MAC address to be used in the Ethernet frame. This is a two stage process: (i) the ARP cache is consulted, to see if the MAC address is already known, in which case the correct address is added and the packet queued for transmission. (ii) If the MAC address is not in the ARP cache, the ARP protocol is used to request the address, and the packet is queued until an appropriate response (or timeout) occurs.

**Encapsulation:** The Ethernet frame is completed, by inserting the Destination, Source and Ethernet Type fields.

Transmit: The frame is transmitted using the MAC procedure for Ethernet.

#### 2.17 IP Fragmentation processing at a Router

To fragment/segment a long internet packet, an Intermediate System using the Internet Protocol (for example, a router), creates two new IP packets and copies the contents of the IP header fields from the long packet into BOTH new IP headers.

The data of the long packet is divided into two portions on a 8 byte (64 bit) boundary. All packets which have a more fragments (MF) flag set, must have an integral multiple of 8 bytes, but those that do not have this flag set need not do.

If we call the number of 8 byte blocks in the first portion NFB (for Number of Fragment Blocks). The first portion of the data is placed in the first new IP packet, and the total length field is set to the length of the FIRST IP packet. The more-fragments flag (MF) is set to one.

The second portion of the data is placed in the second new IP packet, and the total length field is set to the length of the SECOND packet. The more-fragments flag (MF) carries the same value as the long packet. The fragment offset field of the second new IP is set to the value of that field in the long IP packet plus the NFB.

## 2.18 IP Fragmentation processing at the Receiving End System

An end system that accepts an IP packet (with a destination IP address that matches its own IP source address) will also reassemble any fragmented IP packets before these are passed to the next higher protocol layer.

The system stores all received fragments (i.e., IP packets with a more-fragments flag (MF) set to one, OR where the fragment offset is non-zero), in one of a number of buffers (memory space). Packets with the same 16-bit Identification value are stored in the same buffer, at the offset specified by the fragment offset field specified in the packet header.

Packets which are incomplete remain stored in the buffer until either all fragments are received, OR a timer expires, indicating that the receiver does not expect to receive any more fragments. Completed packets are forwarded to the next higher protocol layer.

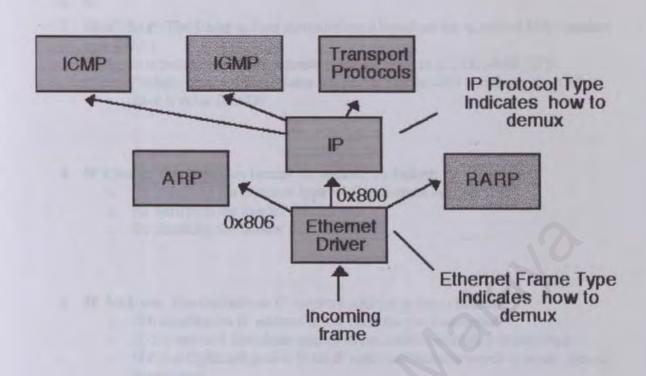

## 2.19 Reception of a frame from Ethernet

The following summary shows the processing performed by an end system in an IP network. It is assumed that the system is connected to an Ethernet network.

**WXES3182**

Figure 2.5 Reception of a frame from Ethernet

The received frames are processed as follows:

- 1. MAC Protocol: The Ethernet controller in the network interface card verifies that the frame is:

- Not less than the minimum frame length not greater than the maximum length (1500 B)

- Contains a valid CRC at the end

- Does not contain a residue (i.e. extra bits which do not form a byte)

- MAC Address: The frame is then filtered based on the MAC destination address and accepted only if:

- It is a broadcast frame (i.e. all bits of the destination address field are set to 1)

- o It is a multicast frame to a registered MAC group address

- o It is a unicast frame to the node's own MAC address

- Or the interface is acting in promiscuous mode (i.e. as a bridge)

- MAC SAP: The frame is then demultiplexed based on the specified MAC packet type (SAP)

- o It is passed to the appropriate protocol layer (e.g. LLC, ARP, IP)

- Packets destined for IP have a type field of 0x0800 and those for ARP have a value 0x0806

- 4. IP Check: The IP packet header is checked, including:

- By checking the protocol type =4 (i.e. current version of IP)

- o By verifying the header checksum

- o By checking the header packet length

- 5. IP Address: The destination IP network address is then checked:

- o If it matches an IP address of the node then it is accepted

- o If it is network broadcast packet to the node's network it is accepted

- If it is a multicast packet to an IP multicast address which is in use then it is accepted

- If it is none of these, it is forwarded using the routing table (if possible) or discarded

- 6. **IP Fragmentation:** Packets for the node are then checked concerning whether reassembly is required:

- o The fragmentation offset value and more flags are inspected

- Fragments are placed in a buffer until other fragments are received to complete the packet.

- 7. IP SAP: The IP protocol field (SAP) is checked:

- The SAP field identifies the transport protocol (1 = ICMP; 6 = TCP; 17= UDP)

- o The complete packet is passed to the appropriate transport layer protocol.

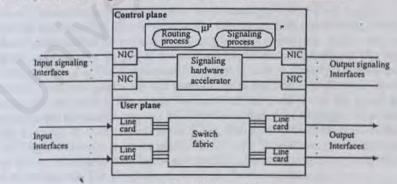

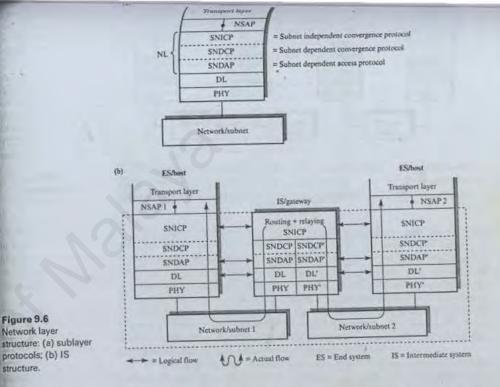

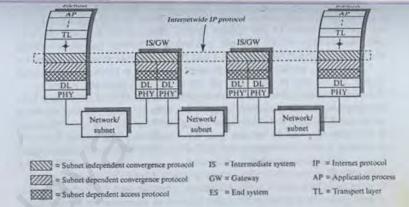

# 2.20 System Comparison Architecture

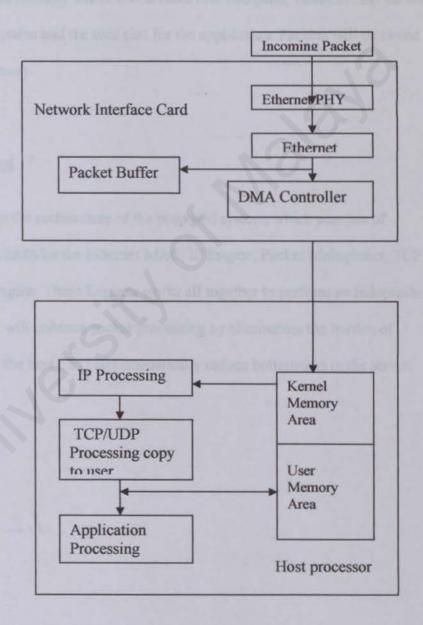

# 2.20.1 Existing System

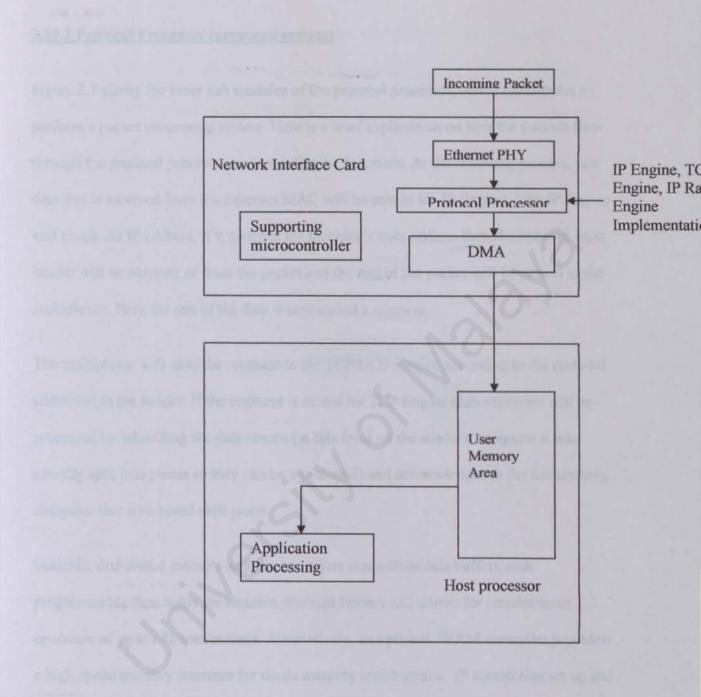

The diagram below shows the architecture of the existing system, which is implemented in software.

Figure 2.6 Existing System Architecture

#### **WXES3182**

In general, this system receives packets through the network Interface Card, process them and then store the packets in buffer before sending it to the main memory. Later on, the IP header and the TCP/UDP header will be processed by the operating system. The checksum operation will be made on the packet to make sure it's free from errors. The operating system has the memory where it is divided into two parts, which are the kernel part for the operating system and the user part for the application. Packets will be stored and retrieved from memory.

#### 2.20.2 System Proposed

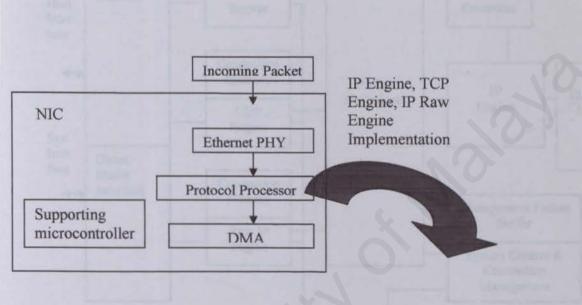

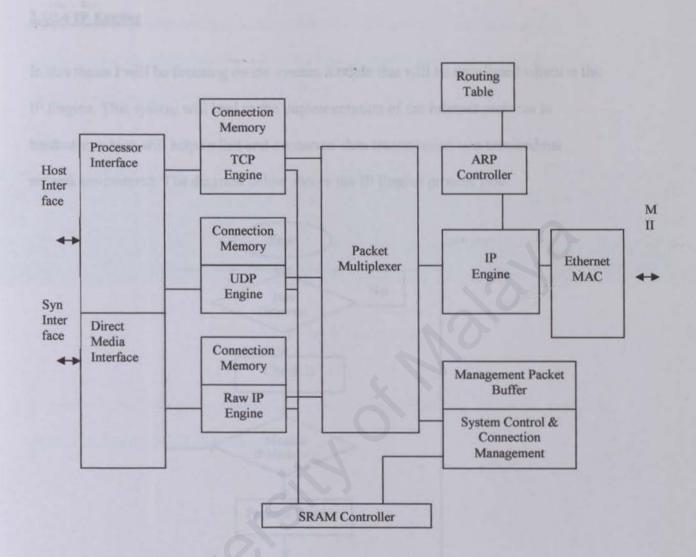

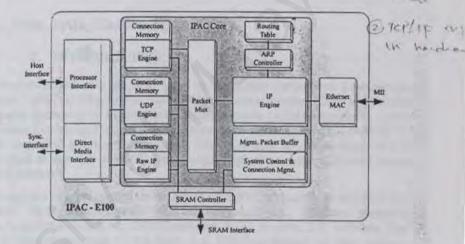

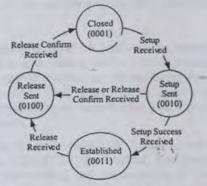

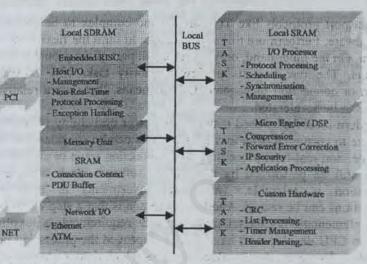

The figure below shows the architecture of the proposed system, which consists of protocol processor that includes the Ethernet MAC, IP Engine, Packet Multiplexer, TCP Engine and the UDP Engine. These Engines works all together to perform an independent protocol processor that will enhance packet processing by eliminating the burden of protocol processing on the host CPU and dramatically reduce bottlenecks in the server.

Figure 2.7 Proposed System Architecture

#### **WXES3182**

#### 2.20.3 Protocol Processor (proposed system)

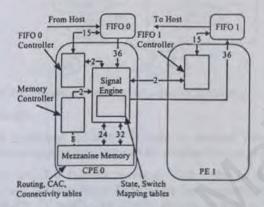

Figure 2.7 shows the inner sub modules of the protocol processor, which contributes to perform a packet processing system. Here is a brief explanation on how the packets flow through the protocol processor and each Engine functions. At the receiving process, raw data that is received form the Ethernet MAC will be sent to the IP Engine. The IP Engine will check the IP address, if it matches the machine's own address then the network layer header will be stripped of from the packet and the rest of the packet will be passed to the multiplexer. Here the rest of the data is now called a *segment*.

The multiplexer will send the segment to the TCP/UDP Engine according to the protocol addressed in the header. If the segment is meant for TCP Engine then segments will be processed by rebuilding the data stream (at this level on the sender's computer it was actually split into pieces so they can be transferred) and acknowledges to the transmitting computer that it received each piece.

Scalable, distributed memory architecture offers connection data buffers with programmable thresholds for variable interrupt latency and allows for simultaneous operation of up to 64k connections. Alternatively, an optional SRAM controller provides a high-speed memory interface for single memory architectures. IP connection set up and management is made easy by a message-based interface of the comprehensive control unit, which fully supports IP management protocols and allows for system configuration.

**WXES3182**

Its auto-configuration and remote management capability enable it to provide IP connectivity even without any external processor interaction, which makes it an ideal communication extension for existing applications.

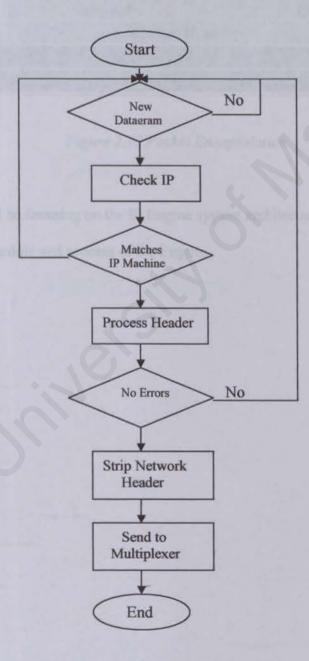

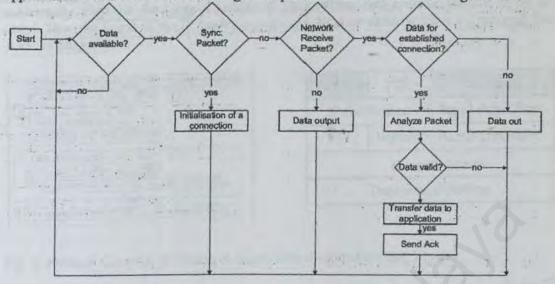

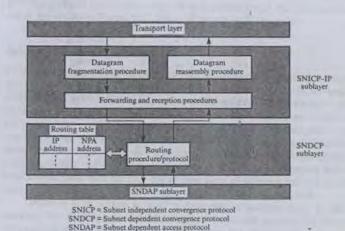

# 2.20.4 IP Engine

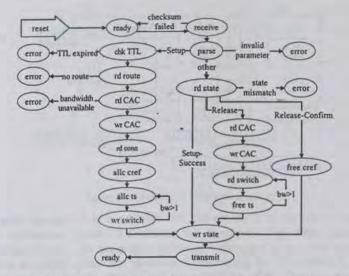

In this thesis I will be focusing on the system module that will be developed which is the IP Engine. This system will lead to the implementation of the internet protocol in hardware, which will help in fast and accuarate data transmission in a tremendous netwok enviroment. The diagram below shows the IP Engine process flow.

Figure 2.9 IP Engine Process Flow

Figure 2.10 shows the minimal header encapsulation where the network header is stripped out of the packet and the rest of the header is passed to the multiplexer. This process made at the IP Engine.

| 01 02 03 04 05 06 | 07 08          | 09 10 11 12 13 14 15 | 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |

|-------------------|----------------|----------------------|-------------------------------------------------|

| Protocol          | S              | S Reserved           | Header checksum                                 |

|                   | and the second | Destination          | n IP address                                    |

|                   |                | Original Sou         | In Pakless                                      |

|                   | 180 M          | Design of D          |                                                 |

Figure 2.10 Packet Encapsulation

In chapter 5 i will be focusing on the IP Engine system architecture, which will explain in detail each sub module and process of the Engine.

birthedd bgs

# **Chapter 3**

This chapter illustrate the interference that have been send to bis project out the advantages

# Methodology

### 3.1 Methodology

This chapter illustrate the methodology that have been used in this project and the advantages of the implemented architecture in developing the IP Engine. The methodology used is the hardware description language is VHDL.

### Methodology

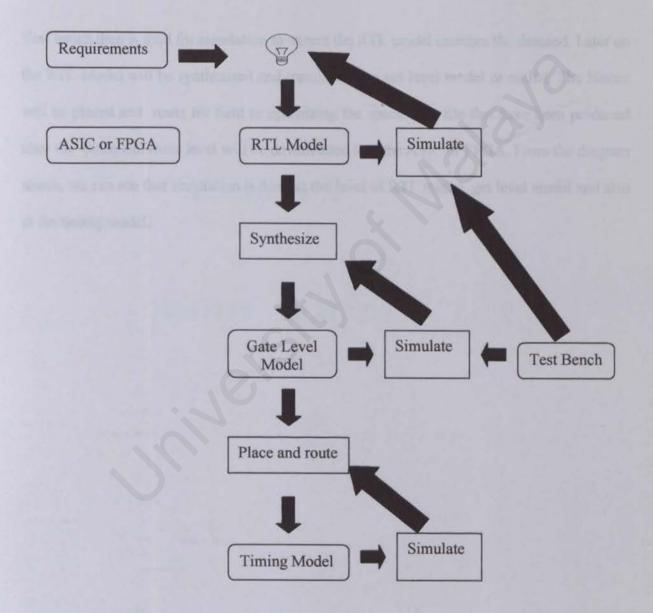

The diagram above shows the basic VHDL methodology process architecture beggining by inserting the architecture into the FPGA or ASIC. Firstly, we have to think of the demand of each architecture. According to the demmand we can develop the RTL model and the test bench using VHDL.

Test bench then is used for simulation to ensure the RTL model matches the demand. Later on the RTL Model will be synthezised and translated into get level model or netlist. The Netlist will be placed and route for field or optimizing the speed. The file that have been produced after the place dan route level will be downloaded into the ASIC or FPGA. From the diagram above, we can see that simulation is done at the level of RTL model, get level model and also at the timing model.

# 11.9100

The backward description begans will be used to description and modeling of digital grains, by description for the backward of the backward of a space of the part of a side of the backward o

# **Chapter 4**

# System Analysis

### 4.1 VHDL

The hardware description language will be used in this project is VHDL hardware description language. Recently, it is increasingly being used for description and modeling of digital system, leading to use of this language for system design field especially robotics and microprocessors development. It is useful in describing hardware for the purpose of simulation, modeling, testing design and documentation. It provides a convenient and compact format for the hierarchical representation of functional and writing detail of digital systems.

#### 4.2 What is VHDL

VHDL is an acronym for VHSIC Hardware Description Language. VHSIC is an acronym for very high-speed integrated circuit. It is hardware description language that can be used to model a digital system at many levels of abstraction, ranging from the algorithmic level to the logic level. The complexity of the digital system being modeled could vary from that of a simple gate to a complete digital electronic system, or anything in between. The digital system can also be explicitly modeled in the same description.

The VHDL language can be regarded as an integrated amalgamation of the following languages:

- Sequential language

- Concurrent language

- Next-list language

- Wave generation language

Therefore, the language has construct that enable the user to express the concurrent or sequential behavior of a digital system with or without timing. It also allows users to model

41

the system as an interconnection of components. Test waveforms can also be generated using the same constructs. All the above constructs may be combined to provide a comprehensive description of the system in a single model.

The language not only defines the syntax but also vary clear simulation semantics for each language construct. Therefore, models written in this language can be verified using a VHDL simulator. It is a strongly typed language and is often verbose to write. It inherits many its features, rop-daily the sequential language part from the ADA programming language. Because VHDL provides an extensive range of modeling capabilities, it is often difficult to understand. Fortunately, it is possible to quickly assimilate a core subset of the language that is both easy and simple to understand without learning the more complex features. This subset is usually sufficient to model most applications. However the complete language has sufficient power to capture the description of the most complex chips to a complete electronic system.

#### 4.3 VHDL Advantages

VHDL offers the following advantages for digital design:

- Standard: VHDL is an EKE standard. Just like any standards (such as graphic xwindow standard, bus communication interface standard, high level programming languages and so on), it reduces confusion and makes interfaces between tools, companies and products easier. Any development to the standard would have better chances of lasting longer and have less chance of becoming obsolete due to incompatibility with others.

- Industry support: With the advent of more powerful and efficient VHDL tools has come the growing support of the electronic industry. Companies use VHDL tools not only with regard to defense contracts, but also for their commercial designs.

- Portability: The same VHDL code can be simulated and used in many design tools whose limited capability may not be competitive in later markets. The VHDL standard also transforms design data much easier than a design database of a proprietary design tools.

- Modeling Capability: VHDL was developed to model all levels of designs, from electronic boxes to transistors. VHDL can accommodate behavioral constructs and mathematical routines that describe complex model, such as queuing networks and analog circuits. It allows the use of multiple architectures and associated with the same design during various stages of the design process.

- Reusability: Certain common designs can be described, verified and modified slightly in VHDL for future use. This eliminates reading and marking changes to schematic pages, which is time consuming and subject to error. For example, a parameterized multiplier VHDL code can be reused easily by changing the width parameter so that the same code can do either 16 by 16 or 12 by 8 multiplication.

- Technology and Foundry Independence: The functionality and behavior of the design can be described with VHDL and verified, making it foundry and technology independent. This frees the designer to proceed without having to wait for the foundry and technology to be selected.

- Documentation: VHDL is a design description language, which allows documentation to be located in a single place by embedding it in the code. The combining of comments and the code that actually dictates what the design should do to reduce the ambiguity between specification and implementation.

- New Design Methodology: Using VHDL and synthesis creates a new methodology that increases the design productivity, shortens the design cycle and lower costs. It amounts to a revolution comparable to that introduced by the automatic semi-custom layout synthesis tools of the last few years.

#### 4.4 VHDL and Verilog comparison

This section compares and contrasts the individual aspects of both languages the VHDL and the Verilog.

### i. Capability

Hardware structure can be modeled equally effectively in both VHDL and Verilog. When modeling abstract hardware, the capability of VHDL can sometimes only be achieved in Verilog when using the PLI. The choice of which to use is not therefore based solely on technical capability but on:

- Personal preferences

- EDA tool availability

- Commercial, business and marketing issues

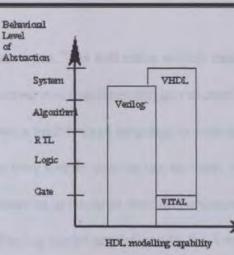

The modeling constructs of VHDL and Verilog cover a slightly different spectrum across the levels of behavioral abstraction; see Figure 1.

System Analysis

**WXES3182**

Figure 1. HDL modeling capability

#### ii. Compilation

VHDL multiple design-units (entity/architecture pairs), that reside in the same system file, may be separately compiled if so desired. However, it is good design practice to keep each design unit in it's own system file in which case separate compilation should not be an issue. The Verilog language is still rooted in its native interpretative mode. Compilation is a means of speeding up simulation, but has not changed the original nature of the language. As a result care must be taken with both the compilation order of code written in a single file and the compilation order of multiple files. Simulation results can change by simply changing the order of compilation.

#### iii. Data types

In VHDL a multitude of language or user defined data types can be used. This means dedicated conversion functions are needed to convert objects from one type to another. The choice of which data types to use should be considered wisely, especially enumerated (abstract) data types. This will make models easier to write, clearer to read and avoid unnecessary conversion functions that can clutter the code. VHDL may be preferred because it allows a multitude of language or user defined data types to be used. In Verilog data types a re very simple, easy to use and very much geared towards modeling hardware structure as opposed to abstract hardware modeling. Unlike VHDL, all data types used in a Verilog model are defined by the Verilog language and not by the user.

#### iv. Design reusability

VHDL procedures and functions may be placed in a package so that they are avail able to any design-unit that wishes to use them.

There is no concept of packages in Verilog. Functions and procedures used within a model must be defined in the module. To make functions and procedures generally accessible from different module statements the functions and procedures must be placed in a separate system file and included using the include compiler directive.

# v. High level constructs

There are more constructs and features for high-level modeling in VHDL than there is in

Verilog. Abstract data types can be used along with the following statements:

- Package statements for model reuse

- Configuration statements for configuring design structure

- Generate statements for replicating structure

- Generic statements for generic models that can be individually characterized, for example, bit width.

All these languages statements are useful in synthesizable models.

Except verilog for being able to parameterize models by overloading parameter constants, there is no equivalent to the high-level VHDL modeling statements in Verilog.

47

# **Chapter 5**

# **System Design**

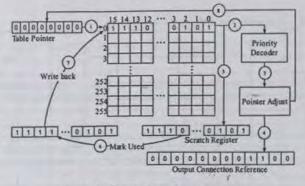

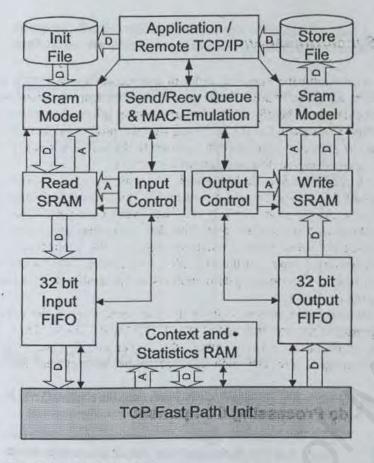

# 5.1 System Design

The system module which will be developed is the IP Engine. This system will lead to the implementation of the internet protocol in hardware, which will help in fast and accuarate data transmission in a tremendous netwok environment. This chapter will explain in detail each process of the IP Engine by illustrating the system design, flow charts and block diagrams that will ease the understanding of the system and module functions.

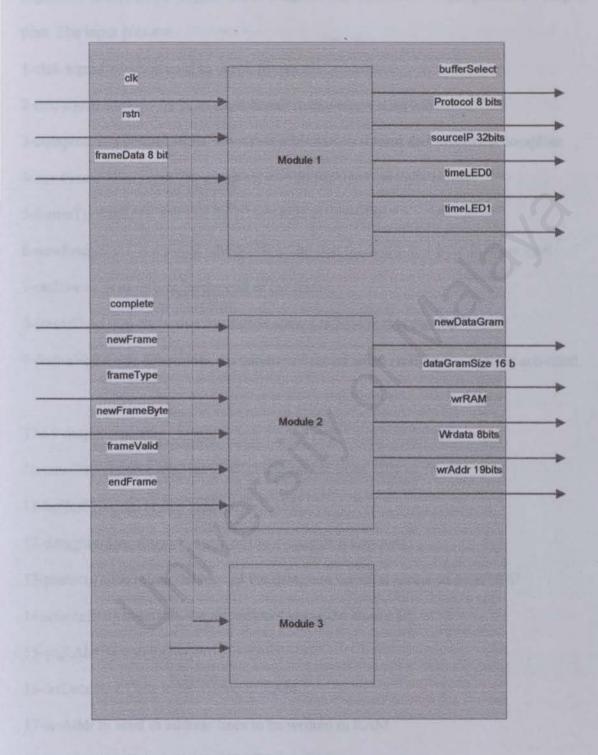

The IP Engine internal block diagram is designed at the part one of this thesis and will be developed at the second part of the thesis using the peakFPGA software. Each sub process module will be developed and then integreted to perform the whole Engine as an Internet Protocol Engine which will process packets independently. The diagram below shows the Engine Black Box by explening each in and out pin, followed by the internal Black Box of the IP Engine describing the sub process modules and the signals used to activate each process.

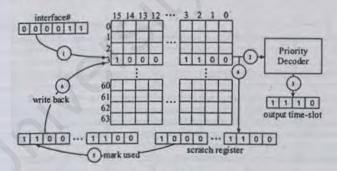

# 5.2 IP Engine Block Diagram

Figure 5.1 IP Engine Block Diagram

#### System Design

#### **WXES3182**

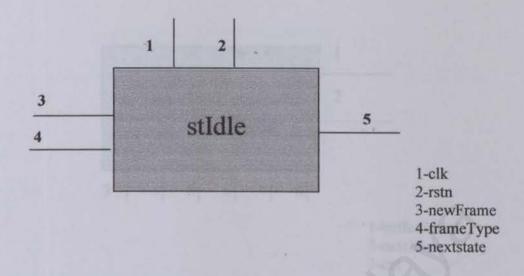

Figure 5.1 shows the IP Engine Block Diagram that consist of 9 input pins and 9 output pins. The input pins are :

1-clck signal which is used to check for positive transition.

2-rstn signal to show its in an asynchronous active low reset mode.

3-complete is a control signal from ram arbitrator to inform that process is complete.

4-newFrame is an input pin which recieve frame from the layer below

5-frameType tells its a frame for IP when its activated to 1.

6-newFrameByte is a signal which informing that there is a new byte in the stream.

7-endFrame is to inform its the end of the frame.

8-frameData is to show that the data is streamed here in this frame.

9-frameValid will determines the validity of frame when endframe is high or activated.

The 9 output pins are:

10-newDatagram shows that an IP datagram has been fully recieved.

11-bufferSelect indicates location in RAM.

12-datagramSize shows the size of the datagram is recieved.

13-protocol determines the type of the datagram which is meant to TCP/UDP

14-sourceIP its to lets the upper protocol know the source IP.

15-wrRAM its a signal to write to RAM.

16-wrData its a Data to be written in RAM.

17-wrAddr to send th address lines to be written in RAM.

18-timeLED0/LED1 indicates if buffer 0/1 is busy.

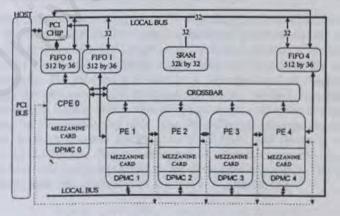

# 5.3 Internal Block diagram

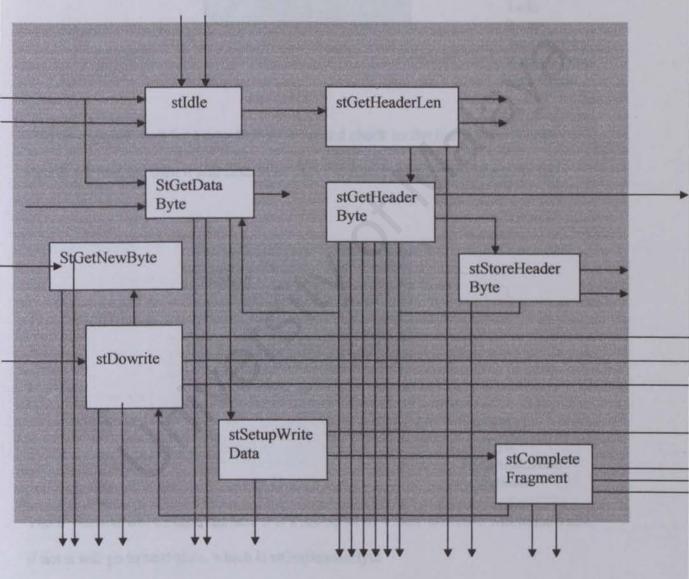

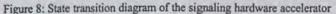

The diagram below shows the internal block diagram of the IP Engine sub modules which illustrate the sub process of the Engine. This design is for the process of recieving a packet from the Ethernet and processing it, then passing it to the upper layer of the TCP/IP stack.

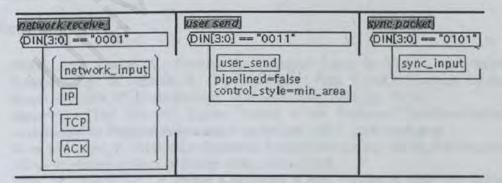

Figure 5.2 IP Engine internal Block Diagram

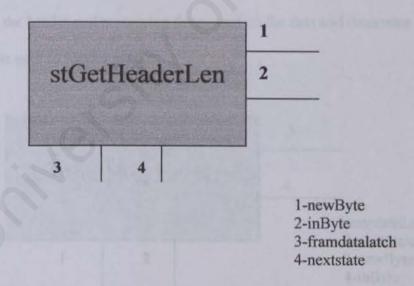

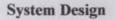

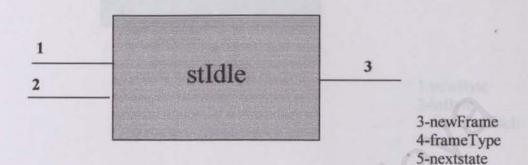

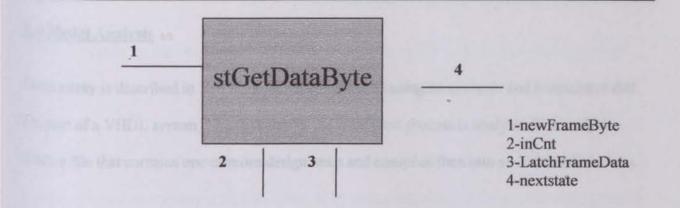

This process will wait for a new frame arrival and check on the frame type. If both signals are enabled then it will determine the next state by getting the header length.

The IP version will be checked here if it's not equal to 4 then next state will remain idle, if not it will go to next state, which is stGetHeaderByte.

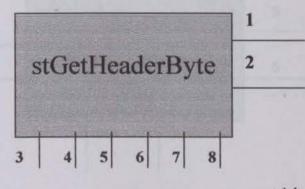

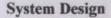

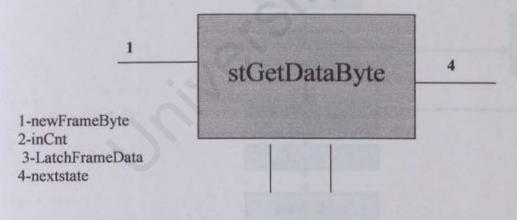

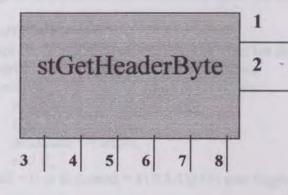

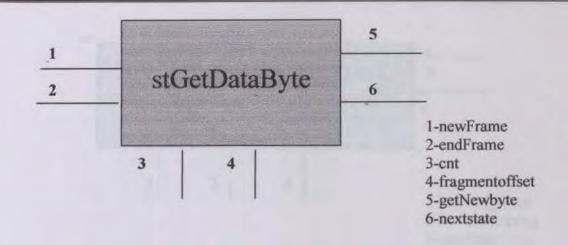

1-bufferSelect 2-nextState 3-cnt 4-checksum 5-ident0 6-position0 7-ident1 8-position1

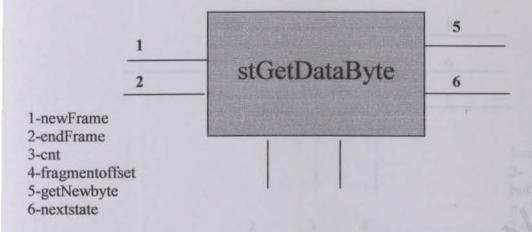

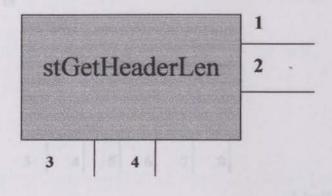

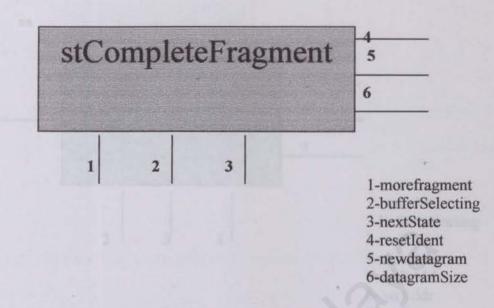

If we finished getting the header and processing them, start on the data and determine which buffer should be used to handle the data.

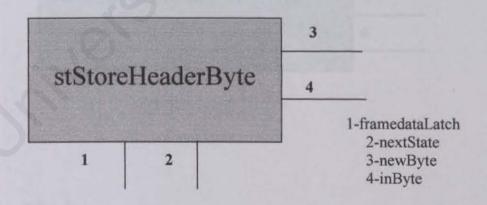

Operate on each value of the header received according to count and store the header in RAM.

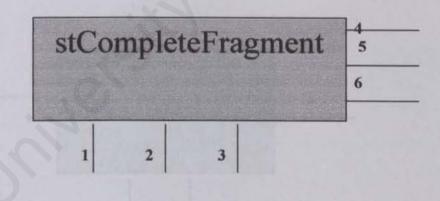

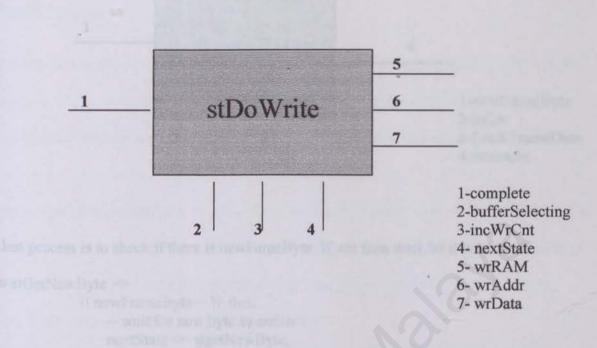

If we haven't finished receiving the data, then check the counter if it is not equal to datagram length then the next state will be stSetupWriteDataByte. Else if endFrame and frameValid is enabled, that means that the frame is finished and was valid. Then it will go to the next state which is stSetupwriteData.

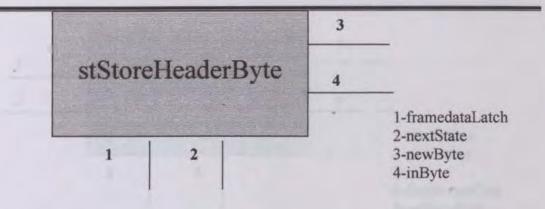

1-morefragment 2-bufferSelecting 3-nextState 4-resetIdent 5-newdatagram 6-datagramSize

At this state a signal will be sent to the transport layer informing that the datagram is

finished or await of a next frame.

At this state we wait for RAM write request to be serviced if complete, then we can write data to RAM.

The last process is to check if there is newFameByte. If yes then wait for it to arrive.

Figure 5.3 Process Flow

Constant Inspirement Station

WIEDONE.

search figure by show a surplicity design process including but see

# Chapter 6

# **System Implementation**

#### System Implementation

WXES3182

#### 6.1 Introduction

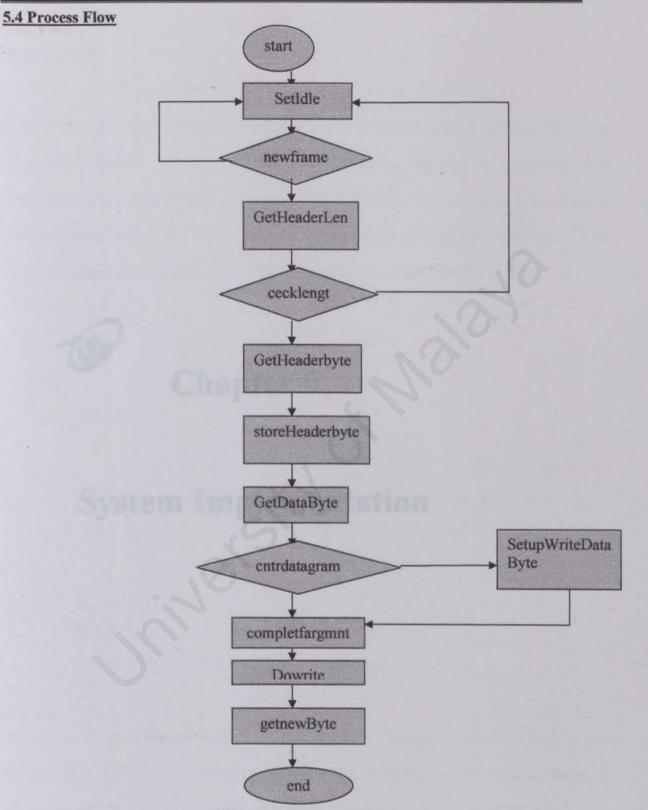

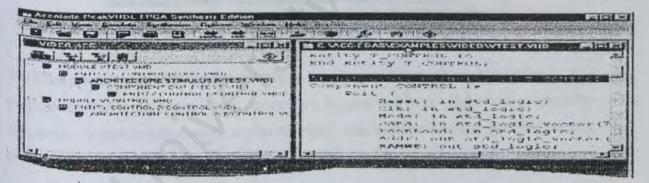

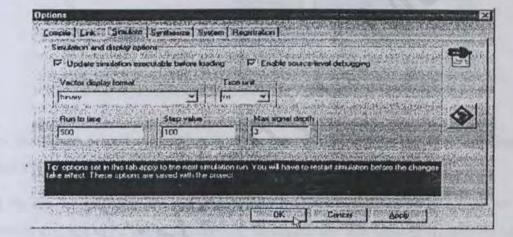

After the design of the architecture has been fixed, the implementation of the IP Engine was then bieng started. Figure 6.1 shows a simplified design process including both synthesis and simulation for one or more programmable logic design. The key for understanding this process and to understand how to use VHDL, is to know the importance of test development. Test development should begin as soon as the general requirements of the system are known.

Figure 6.1 Steps In Implementing A VHDL Module

VHDL is used for design entry. After bieng captured into a design entry system using a text editor, the VHDL source code must be passed diresctly to synthesis tools for implementation in a specified type of device. The its input to simulation, allowing it to be functionally verified.

#### System Implementation

On the test development side, script files or VHDL test benches can be created to exercise the cercuit to verify that it meats the functional and timing constrains of the specification. Thesse script files may be entered using a text editor, or ma be generated from other forms of test stimulus information such as graphical waveforms.

#### 6.2 Design Entry

An external editor has been used for the design entry. Xilinx Foundation offers three types of design entry editor for the prefernces of the user. Three of these editors are listed below:

- HDL editor

- FSM editor

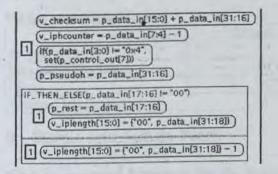

- Schematic Editor